1

Изобретение относится к технике электросвязи и может быть использовано в цифровых линиях связи для контроля линейного сигнала, передаваемого в кодах BIF, CMI и DMI.

Целью изобретения является повышение помехоустойчивости устройства,

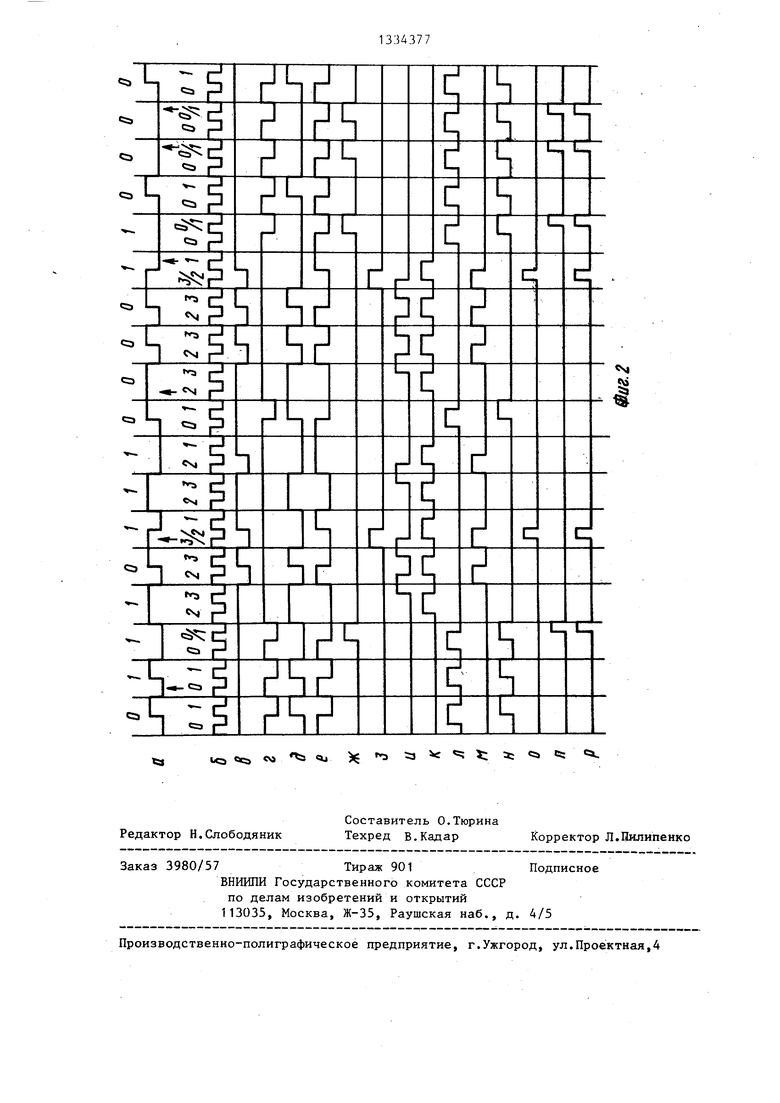

На фиг.1 представлена структурная схема устройства для обнаружения ошибок цифрового сигнала; на фиг,2 - временные диаграммы, иллюстрирзгющне работу устройства.

Устройство для обнаружения ошибок цифрового сигнала содержит первый 1 и второй 2 элементы НЕ, первьш 3 и второй 4 элементы И, элементы ИЛИ 5 и 6, третий 7 и четвертый 8 элементы И, накопитель 9, дешифратор 10, коммутатор 11, блок 12 памяти, блок

13вьщеления максимального кода, блок

14выделения минимального кода, элемент ИЛИ 15, 16 - 18 - входы устройства, выход 19 устройства.

Устройство работает следующим образом.

На вход 16 подается последовательность импульсов с частотой следования, равной двойной тактовой частоте (фиг.26), на вход 17 подается информационная последовательность цифровых сигналов (фиг.2а).

Цифровая сумма в устройстве подсчитывается в накопителе 9. С выхода первого элемента НЕ 1 на вход накопителя 9 поступают импульсы двойной тактовой частоты в инвер сном виде а на другие входы накопителя 9 поступают разрешающие сигналы соответственно с выхода элементов И 7 и 8. При наличии на втором входе накопителя 9 сигнала высокого уровня в нем происходит процесс сложения поступающих на первый вход импульсов. При наличии сигнала высокого уровня на третьем входе накопителя 9 в нем идет обратный процесс - вычитание из записанной суммы импульсов, поступающих на первый вход накопителя 9. Сумма импульсов, содержащаяся в накопителе 9, отражается состоянием его выходов. Таким образом, накопитель 9 может содержать цифровую сумму сигнала в коде в пределах от О до 2 для сигналов в кодах BIF и DMI и от О до 3 для кода CMI. Эти пределы цифровых сумм строго определяются структурой сигналов в этих кодах при отсутствии ошибок.

343772

Дешифратор 10 предназначен для определения состояния накопителя 9, в частности высокий уровень сигнала на втором выходе дешифраторв 10 (фиг.2и) свидетельствует о наличии в накопителе 9 суммы, равной трем. Высокий уровень сигнала на первом выходе дешифратора 10 свидетельству-jQ ет о наличии суммы, равной двум

(фиг.2к), а высокий уровень на третьем выходе дешифратора 10 свидетельствует о наличии нуля (фиг.2л). Вся эта информация с выходов дешифратора 15 10 поступает в блок 12 памяти для последующего анализа. На первый вход блока 12 памяти поступает через коммутатор 11 сигнал либо с второго, либо с первого выхода дешифратора

20

10. При наличии высокого уровня на входе 18 устройства коммутатор 11

пропускает сигнал с второго выхода дешифратора 10, что соответствует анализу кода CMI. При низком уровне

на входе 18 устройства коммутатор 11 пропускает сигнал с первого выхода ешифратора 10, что соответствует режиму проверки кодов BIF и DMI. На вто- рой вход блока 12 памяти постоянно поступает сигнал с третьего выхода дешифратора 10, а на третий - сигнал двойной тактовой частоты (фиг.2б), обеспечивающий запись информации в блок 12 памяти.

Если блок 12 памяти фиксирует наличие цифровой cyMivibi, отличной от максимальной или минимальной, то на его первом и втором выходах появляются сигналы высокого уровня (фиг.2в,

г), поступающие на входы соответственно элементов И 3 и 4. Цифровая сумма для сигнала в коде CMI (фиг.2а) проставлена под его временной диаграммой, а стрелками на фиг.2а помечены ошибочные символы сигнала в коде. Реакция бпока 12 памяти на изменение цифровой суммы сигнала (фиг. 2а) задержана на половину тактового интервала относительно сигнала из-за

задержек на четверть тактового интервала в накопителе 9 и блоке 12 памя- ти. При высоких уровнях на первых входах элементов И 3 и 4 (фиг.2в,г) элемент И 3 формирует выходной сигнал (фиг.2д) высокого уровня при высоком уровне си гнала на входе 17 устройства (фиг.2а), поступающего на инверсный вход эдемента И 3 в инверсном виде с выхода второго элемента

НЕ 2, при низком уровне сигнала (фиг.2а) элемент И 3 формирует сигнал низкого уровня , элемент И 4, наоборот, формирует сигнал (фиг.2е), в котором высокий уровень присутствует при низком уровне сигнала (фиг.2а), а низкий - при высоком уровне сигнала (фиг.2а). Высокий уровень сигнала, появившийся на выходе элемента И 3 (фиг.2д), приводит к появлению высокого уровня на выходе элемента И 7 и разрешает сложение в накопителе 9, Высокий уровень сигнала на выходе элемент И 4 (фиг.2е) вызывает появление высокого уровня на выходе элемента И 8 и разрешает вычитание в накопителе 9.

Если блок 12 памяти фиксирует максимальную цифровую сумму для данного кода, то на втором выходе блока 12 памяти появится (с задержкой относительно сигнала на фиг.2а на половину тактового интервала) сигнал низкого уровня (фиг.2в), который вызывает появление низкого уровня в выходном сигнале элемента И 3 (фиг.2д) независимо от уровня цифрового сигнала (фиг.2а). В этом случае при отсутствии ошибок в цифровом сигнале (фиг.2а) на выходе элемента И 7 присутствует сигнал низкого уровня, запрещающий накопителю 9 производить суммирование. В это время на выходе элемента И 4 (фиг.2е), а значит и элемента И 8 присутствует сигнал высокого уровня, разрешающий вычитание в накопителе 9.

Если блок 12 памяти фиксирует нулевую цифровую сумму, то на его первом выходе появится сигнал низкого уровня, вызывающий появление низкого уровня в выходном сигнале элемента И 4 (фиг.2е). В этом случае при отсутствии ошибок на выходе элемента И 8 присутствует сигнал низкого уровня, а на выходе элемента И 3 (фиг.2д), а значит и элемента И 7 присутствует сигнал высокого уровня, в результате накопитель 9 производит суммирование.

Из-за наличия ошибок в цифровом сигнале (фиг.2а) возникают ситуации, когда в выходных сигналах элементов

нал низкого уровня (фиг.2в), а низкий уровень сигнала (фиг.2е) на выходе элемента И 4 определяется высо КИМ уровнем сигнала (фиг.2а), либо при минимальной цифровой сумме, ког да элемент И 4 закрыт низким уровне сигнала (фиг.2г) на втором выходе блока 12 памяти, а низкий уровень

10 сигнала (фиг.2д) на выходе элемента И 3 обусловлен низким уровнем сигнала (фиг.2а).

При одновременно низких уровнях сигналов (фиг.2д,е) на выходах эле15 ментов И 3 и 4 появляется импульс высокого уровня на выходе элемента ИЛИ 5 (фиг.2ж), если на втором выхо де блока 12 памяти высокий уровень сигнала (фиг.2в) или появляется им20 пульс высокого уровня на выходе эле мента ИЛИ 6 (фиг.2з), если высокий |уровень сигнала имеется на первом выходе блока 12 памяти (фиг.2г). Им пульсы высокого уровня (фиг.2ж, з),

25 пройдя через элементы И 7 и 8, дополнительно разрешают накопителю 9 произвести соответственно одно слож ние или одно вычитание (в цифровой сумме, проставленной под временной

30 диаграммой на фиг.2а, эти дополнительные сложения и вычитания в отдельных тактовых интервала отражены в виде дробей, знаменатель которых цифровая сумма после дополнительног

сложения или вычитания). 35 I

Блок 12 памяти, кроме управления работой накопителя 9, формирует на четвертом и третьем выходах сигнала (фиг.2н,м), представляющие собой за

40 держанные на четверть тактового интервала сигналы нулевой цифровой су мы на третьем выходе дешифратора 10 (фиг.2л) и максимальной цифровой сум мы с выхода коммутатора 11 (в рас45 сматриваемом примере сигнала на фиг. 2 По импульсам высокого уровня сигнал (фиг.2м) блок 13 вьщеления максимал ного кода формирует импульсы (фиг.2 при высо1 ом уровне сигнала на входе 17 устройства (фиг.2а). По импульса высокого уровня сигнала (фиг.2н) бл вьщеления минимального кода формиру ет импульсы (фиг.2п) при высоком уро не выходного сигнала второго элемен

50

И 3 и 4 (фиг.2д,е) одновременно при- gg НЕ 2, инверсного сигналу на фиг.2а,

сутствует низкий уровень. Эти ситуации возникают либо при максимальной цифровой сумме, когда на четвертом выходе блока 12 памяти имеется сигБлок 15 формирования сигнала ошибки объединяет импульсы выходных сигналов блоков 13 и 14 вьщеления максимального и минимального кодов (фиг.

нал низкого уровня (фиг.2в), а низкий уровень сигнала (фиг.2е) на выходе элемента И 4 определяется высо- КИМ уровнем сигнала (фиг.2а), либо при минимальной цифровой сумме, когда элемент И 4 закрыт низким уровнем сигнала (фиг.2г) на втором выходе блока 12 памяти, а низкий уровень

0 сигнала (фиг.2д) на выходе элемента И 3 обусловлен низким уровнем сигнала (фиг.2а).

При одновременно низких уровнях сигналов (фиг.2д,е) на выходах эле5 ментов И 3 и 4 появляется импульс высокого уровня на выходе элемента ИЛИ 5 (фиг.2ж), если на втором выходе блока 12 памяти высокий уровень сигнала (фиг.2в) или появляется им0 пульс высокого уровня на выходе элемента ИЛИ 6 (фиг.2з), если высокий |уровень сигнала имеется на первом выходе блока 12 памяти (фиг.2г). Импульсы высокого уровня (фиг.2ж, з),

5 пройдя через элементы И 7 и 8, дополнительно разрешают накопителю 9 произвести соответственно одно сложение или одно вычитание (в цифровой сумме, проставленной под временной

0 диаграммой на фиг.2а, эти дополнительные сложения и вычитания в отдельных тактовых интервала отражены в виде дробей, знаменатель которых- цифровая сумма после дополнительного

сложения или вычитания). 5 I

Блок 12 памяти, кроме управления работой накопителя 9, формирует на четвертом и третьем выходах сигнала (фиг.2н,м), представляющие собой за0 держанные на четверть тактового интервала сигналы нулевой цифровой суммы на третьем выходе дешифратора 10 (фиг.2л) и максимальной цифровой суммы с выхода коммутатора 11 (в рас5 сматриваемом примере сигнала на фиг. 2и) . По импульсам высокого уровня сигнала (фиг.2м) блок 13 вьщеления максимального кода формирует импульсы (фиг.2о) при высо1 ом уровне сигнала на входе 17 устройства (фиг.2а). По импульсам , высокого уровня сигнала (фиг.2н) блок вьщеления минимального кода формирует импульсы (фиг.2п) при высоком уровне выходного сигнала второго элемента

0

НЕ 2, инверсного сигналу на фиг.2а,

Блок 15 формирования сигнала ошибки объединяет импульсы выходных сигналов блоков 13 и 14 вьщеления максимального и минимального кодов (фиг.2о.

п), образуя сигнал (фиг,2р), каждый импульс которого соответствует одной ошибке в цифровом,сигнале (фиг.2а). Как видно из временных диаграмм (фиг.2), каждая отдельная ошибка в цифровом сигнале (фиг.2а) приводит к появлению только одного импульса на выходе блока 13 выделения максимального кода (фиг.2о) или блока 14 выделения минимального кода (фиг.2п), причем в том же полутактовом интервале, когда появляется импульс на выходе блока 13 или 14; цифровая сумма в накопителе 9 приводится к.нормальной величине, свойственной цифровому сигналу без ошибок.

Формула изобретения

Устройство для обнаружения ошибок цифрового сигнала, содержащее первый элемент НЕ, выход которого подключен к первому входу накопителя, блок выделения максимального кода и блок выделения минимального кода,, второй элемент НЕ, выход которого соединен с инверсным входом первого элемента И и вторым входом блока вьщеления минимального кода, выходы накопителя подключены к соответствующим входам дешифратора, первый и второй выходы которого подключены к соответствуюпгим входам коммутатора, выход которого соединен с первым входом блока памяти, первый выход которого соединен с прямым входом второго элемента И, вто- poft выход - с прямым входом первого элемента И, третий и четвертый выходы блока памяти подключены соответст™

0

5

венно к второму входу .блока выделения максимального кода и третьему входу блока выделения минимального кода, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу блока вЬщеления максимального кода, а выход является выходом устройства,., третий выход дешифратора подключен к второму входу блока памяти, третий вход которого объединен с входом первого элемента НЕ и является первым входом устройства, третий вход блока выделения максимального кода объединен с инверсньп входом второго элемента И и входом второго элемента НЕ и является вторым входом устройства, третий вход коммутатора является тре0 тьим входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости устройства, в него введены третий и четвертый элементы И и второй и третий элементы ИЛИ,

5 выход первого элемента И подключен к первьм входам второго и третьего элементов ИЛИ и третьего элемента И, выход второго элемента И соединен с вторыми входами второго и третьего элементов ИЛИ и первым входом четвертого элемента И, третьи входы второго и третьего элементов ИЛИ подключены соответственно к второму и первому выходам блока памяти, выходы второго и третьего элементов ИЛИ подключены к вторым входам соответственно третьего и четвертого элементов И, выходы которых соединены соответственно с вторым И третьим входами накопителя.

0

5

са

СЭ

иэ а «

) 3V:«5;t;:i.«5iJS:«X

Редактор Н.Слободяник

Составитель О.Тюрина Техред В.Кадар

Заказ 3980/57Тираж 901Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

«SI

J

Корректор Л.Пилипенко

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок цифрового сигнала | 1981 |

|

SU1012451A1 |

| Дискретное устройство синхронизации | 1982 |

|

SU1109928A2 |

| Цифровой измеритель максимального давления сгорания в цилиндре двигателя | 1981 |

|

SU1000810A1 |

| Способ измерения скорости изменения низкой частоты и устройство для его осуществления | 1989 |

|

SU1718135A1 |

| Устройство для исправления ошибок в волоконно-оптических цифровых системах передачи информации | 1989 |

|

SU1608730A1 |

| Устройство для контроля псевдослучайной последовательности двоичных сигналов | 1988 |

|

SU1622950A1 |

| Устройство для контроля дискретных сигналов | 1988 |

|

SU1597881A1 |

| Адаптивный цифровой корректор | 1982 |

|

SU1083379A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1987 |

|

SU1494210A1 |

| Устройство для преобразования цифрового сигнала | 1982 |

|

SU1109925A1 |

| Авторское свидетельство СССР № 780804, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для обнаружения ошибок цифрового сигнала | 1981 |

|

SU1012451A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-30—Публикация

1985-12-09—Подача