11

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в твердотельных приемника изображения для хранения и коммутаци информации с одного из элементов матрицы приемника на шину обработки сигнала.

Целью изобретения является повыше ние быстродействия устройства,

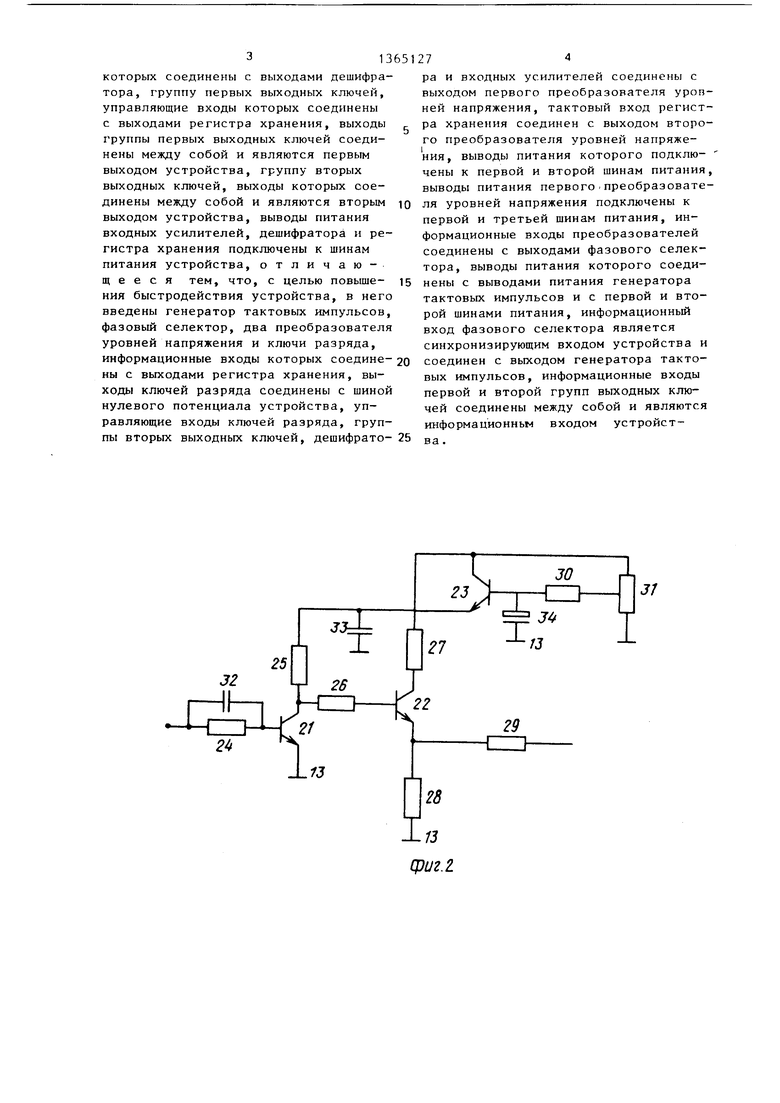

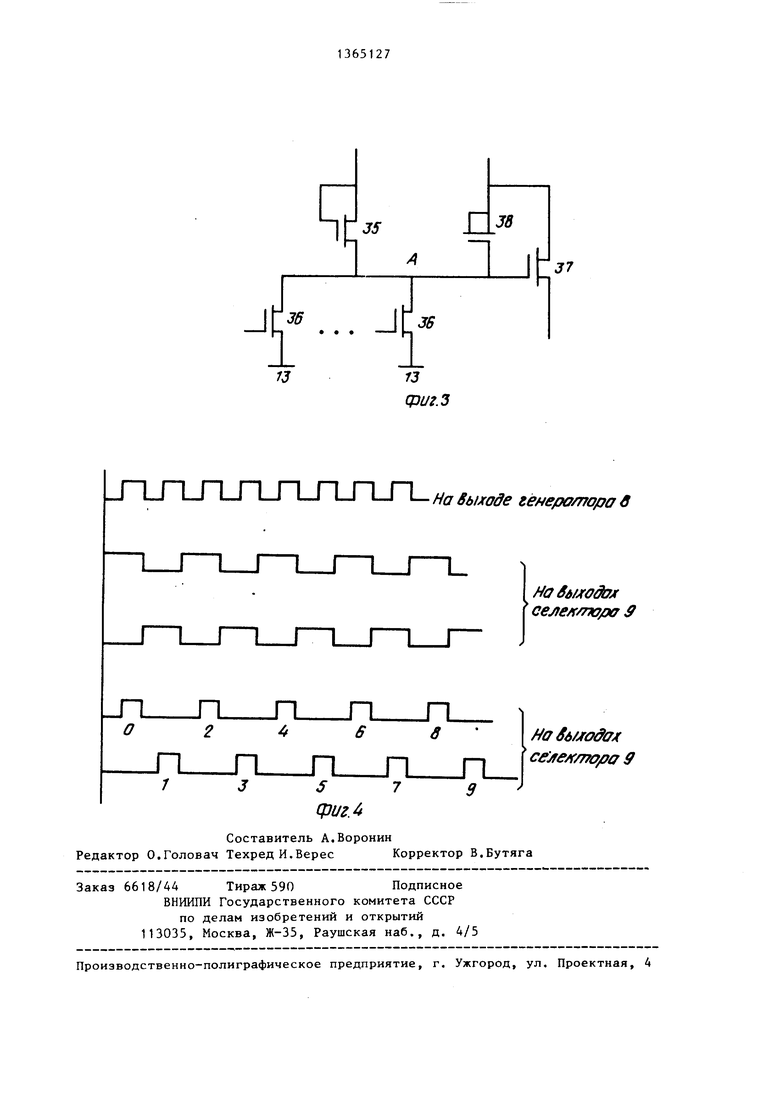

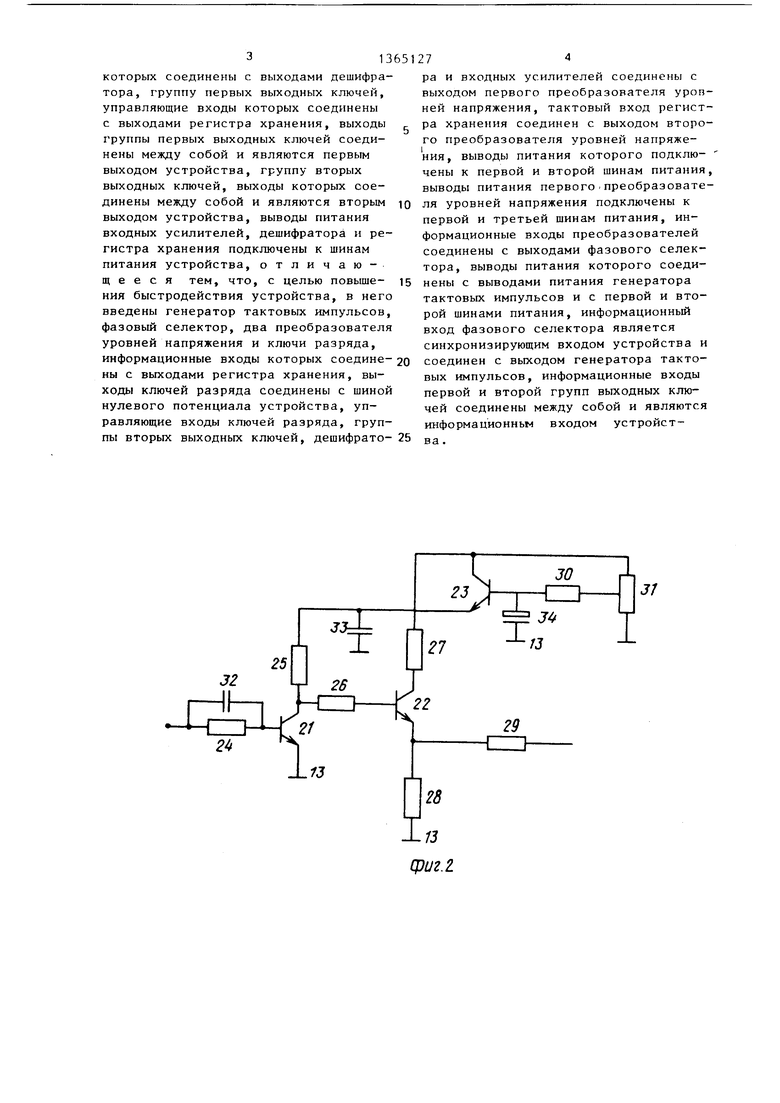

На фиг,1 представлена функциональная схема предлагаемого устройства; на фиг.2 - электрическая схема преобразователя уровней напряжения; на фиг.З - электрическая схема ячейки; на фиг. f - временные диаграммы, поясняющие работу устройства.

Устройство (фиг.1) содержит входные усилители 1, дешифратор 2, ре- гистр 3 хранения, ячейки 4 памяти регистра 3, выходные ключи 5 и 6, ключи 7 разряда, генератор 8 тактовых импульсов, фазовый селектор 9, преобразователи 10 и 11 уровней напряже- ния, адресные входы 12, шину 13 нулевого потенциала, шины 14-16 питания, синхронизирующий вход 17, выходы 18 и 19 и информационный вход 20. Преобразователь 10 или 11 уровней напряже- ния (фиг.2) выполнен на транзисторах 21-23, резисторах 24-31 и конденсаторах 32-34. Ячейка 4 памяти выполнена на транзисторах 35-38.

Устройство работает следующим об- разом.

Код через усилитель 1 поступа ет на вход дешифратора 2 под воздействием выработанных генератором 8 тактовых импульсов и выделенных фазовым селектором 9 четной фазы, высокий уровень которой обеспечивается преобразователем 10 уровня.

Одновременное появление кода адреса на входе 12 и четной фазы на выхо- де преобразователя 10 обеспечивается импульсами по входу 17, при этом записывается логическая 1 в регистр 3

При этом емкость выхода ячейки 4 памяти регистра 3 и затвора транзис- тора одного из ключей 5 обнуляется через открытый транзистор соответствующего ключа 7 разряда, а входы 20 либо обнуляются, либо заряжаются до потенциала второго выхода 19, либо переключается информация входов 20 на второй выход 19. С прекращением действия четного тактового импульса закрываются транзистор ключа 7 и со272

ответствующий ключ 6. При этом потенциал выхода преобразователя 10 равен нулю и в одной из ячеек 4 памяти сохраняется заряд. С приходом нечетного тактового импульса высокого уровня с преобразователя 11 и благодаря использованию МДП-варактора в ячейке 4 памяти формируется накопление заряда: быстро открывается транзистор 37 и импульс управления поступает на затвор транзистора ключа 5, который открывается и коммутируется на первьм выход 18. Связь входов управления питания дешифратора 2 усилителя 1, затворов всех транзисторов ключей 7 разряда и ключей 6 с выходами преобразователей 10, 11 и формирование соответствующих импульсов управления генератора 8 тактовых импульсов, фазового селектора 9 позволяют с высокой скоростью перераспределить заряды, что способствует увеличению быстродействия за счет меньшения времени переключения. При этом достигается увеличение скорости нарастания переднего и заднего фронтов

e

,c

- -с 1Пл

U2()

и:о-; )

раз.

е

и, - амплитуда напряжения входа управления ячеек 4 памяти, дешифратора 2, усилителя 1 затворов транзисторов ключей 5 и 6 в известном устройстве;

и - амплитуда напряжения на этих же входах в предложенном устройстве;

R - сопротивление цепи перезаряда в известном устрой„ Ri-Hj

К, ---- - сопротивление этой

Iv 3 1ч

цепи в предложенном устройстве; RJ - сопротивление открытого

транзистора ключа 7 разряда

Формула изобретения

Запоминающее устройство, содержащее входные усилители, информационные входы которых являются адресными входами устройства, дешифратор, информационные входы которых соединены с выходами входных усилителей, регистр хранения, информационные входы

3136

которых соединены с выходами дешифратора, группу первых выходных ключей, управляющие входы которых соединены с выходами регистра хранения, выходы группы первых выходных ключей соединены между собой и являются первым выходом устройства, группу вторых выходных ключей, выходы которых соединены между собой и являются вторым выходом устройства, выводы питания входных усилителей, дешифратора и регистра хранения подключены к шинам питания устройства, отличающееся тем, что, с целью повыше- ния быстродействия устройства, в него введены генератор тактовых импульсов, фазовый селектор, два преобразователя уровней напряжения и ключи разряда, информационные входы которых соедине- ны с выходами регистра хранения, выходы ключей разряда соединены с шиной нулевого потенциала устройства, управляющие входы ключей разряда, группы вторых выходных ключей, дешифрато-

27

ра и входных усилителей соединены с выходом первого преобразователя уровней напряжения, тактовый вход регистра хранения соединен с выходом второго преобразователя уровней напряжения, выводы питания которого подключены к первой и второй шинам питания выводы питания первого.преобразователя уровней напряжения подключены к первой и третьей шинам питания, информационные входы преобразователей соединены с выходами фазового селектора, выводы питания которого соединены с выводами питания генератора тактовых импульсов и с первой и второй шинами питания, информационный вход фазового селектора является синхронизирующим входом устройства и соединен с выходом генератора тактовых импульсов, информационные входы первой и второй групп выходных ключей соединены между собой и являются информационньм входом устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО СЧИТЫВАНИЯ СИГНАЛЬНОГО ЗАРЯДА С МАТРИЧНОГО ПЗИ-ФОТОПРИЕМНИКА | 2007 |

|

RU2341850C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Стенд для измерения частотных характеристик свойств веществ | 1982 |

|

SU1114981A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1416978A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| Калибратор фазы | 1988 |

|

SU1647449A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может быть исгюльзовано в твердотельных приемниках изображения для хранения и коммутации информации с одного из элементов матрицы приемника на шину обра0, ботки сигнала. Цель изобретения - повышение быстродействия - достигается введением в устройство генератора 8 тактовых импульсов, фазового селектора 9, преобразователей 10, 11 уровней напряжения и ключей 7 разряда. Управление питанием усилителей 1, дешифратора 2, регистра 3 хранения, ключей 7.разряда и ключей 6 с выходов преобразователей 10 и 11 уровней напряжения позволило уменьшить время переключения транзисторов и увеличить скорость нарастания переднего и зад него фронтов импульсов напряжения питания, которые вырабатываются генератором 8 тактовых импульсов и формируются фазовым селектором 9 и преобразователями 10 и 11 уровней напряжения. 4 ил. Л (Л оо о; ел иг.1

Jt... J

rj сриг.З

На Выходе гёнеротора б

| Аналоговые и цифровые интегральные микросхемы | |||

| Справочное пособие:/ /Под ред | |||

| С.Б.Якубовского | |||

| М.: Радио и связь, 1984, с.431, 373. |

Авторы

Даты

1988-01-07—Публикация

1986-07-02—Подача