(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Оперативное запоминающее устройство | 1986 |

|

SU1483493A1 |

| Полупроводниковое запоминающее устройство | 1988 |

|

SU1674261A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Формирователь адресных сигналов для блоков памяти | 1983 |

|

SU1163354A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1096693A1 |

| Усилитель считывания | 1979 |

|

SU858093A1 |

| Запоминающее устройство | 1977 |

|

SU720509A1 |

| Усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-Транзисторах | 1983 |

|

SU1140245A1 |

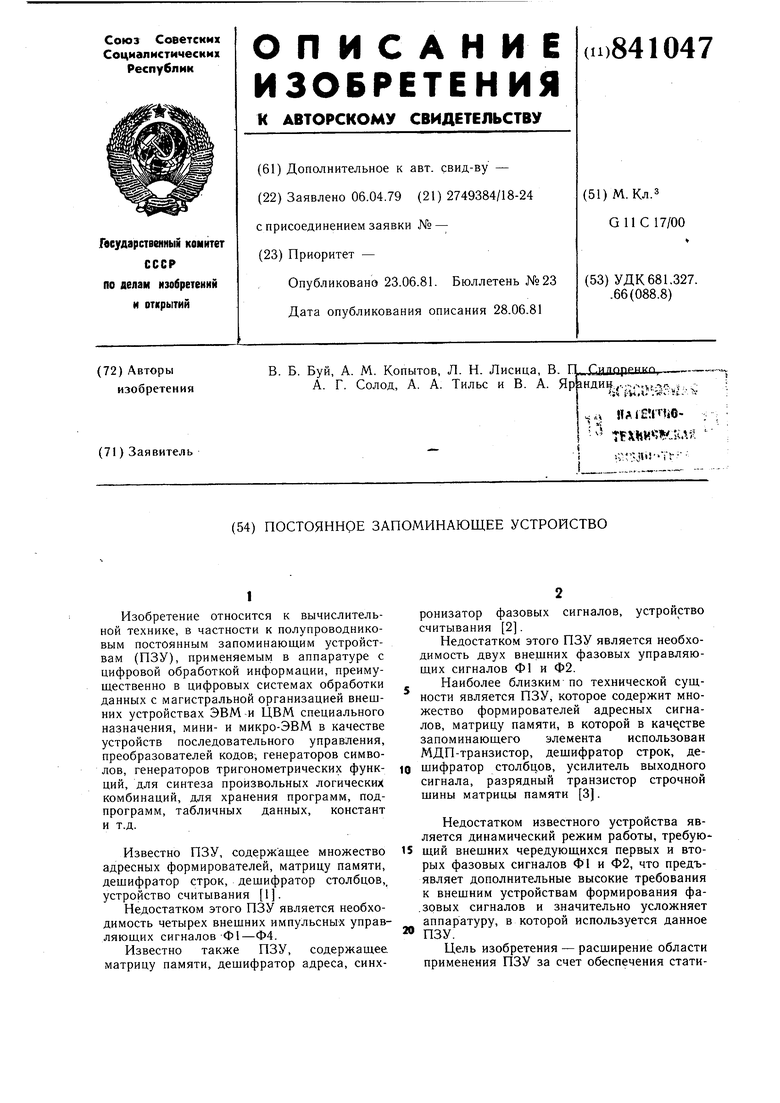

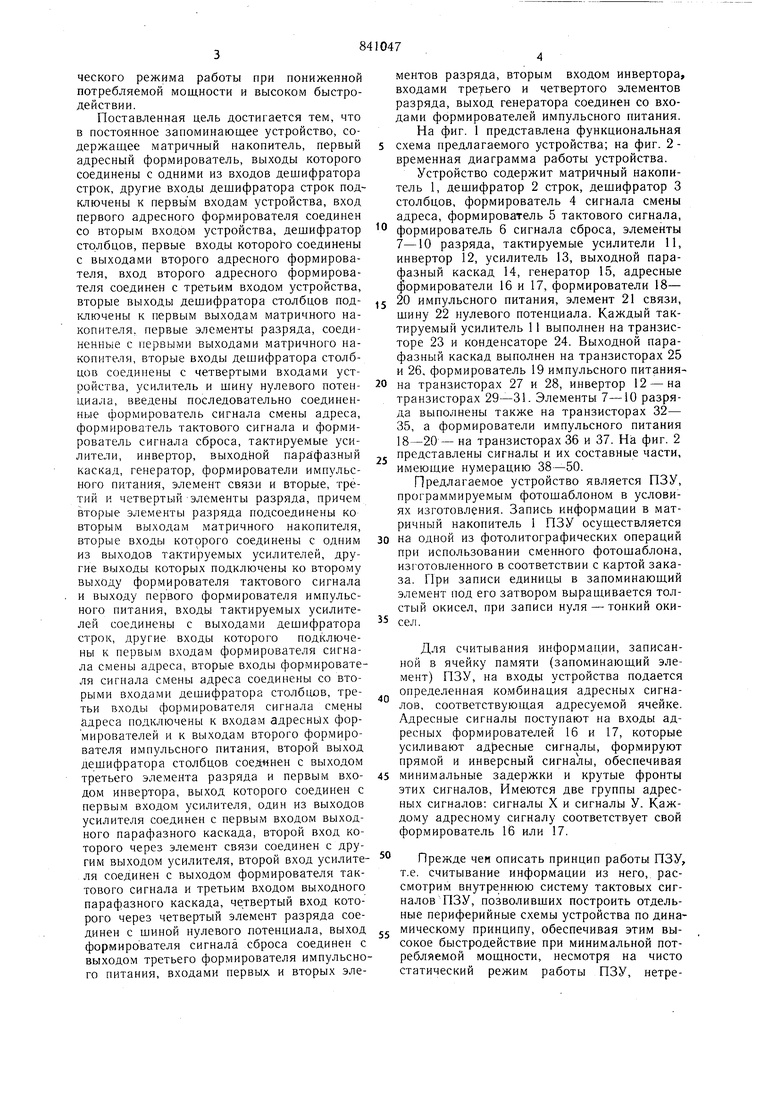

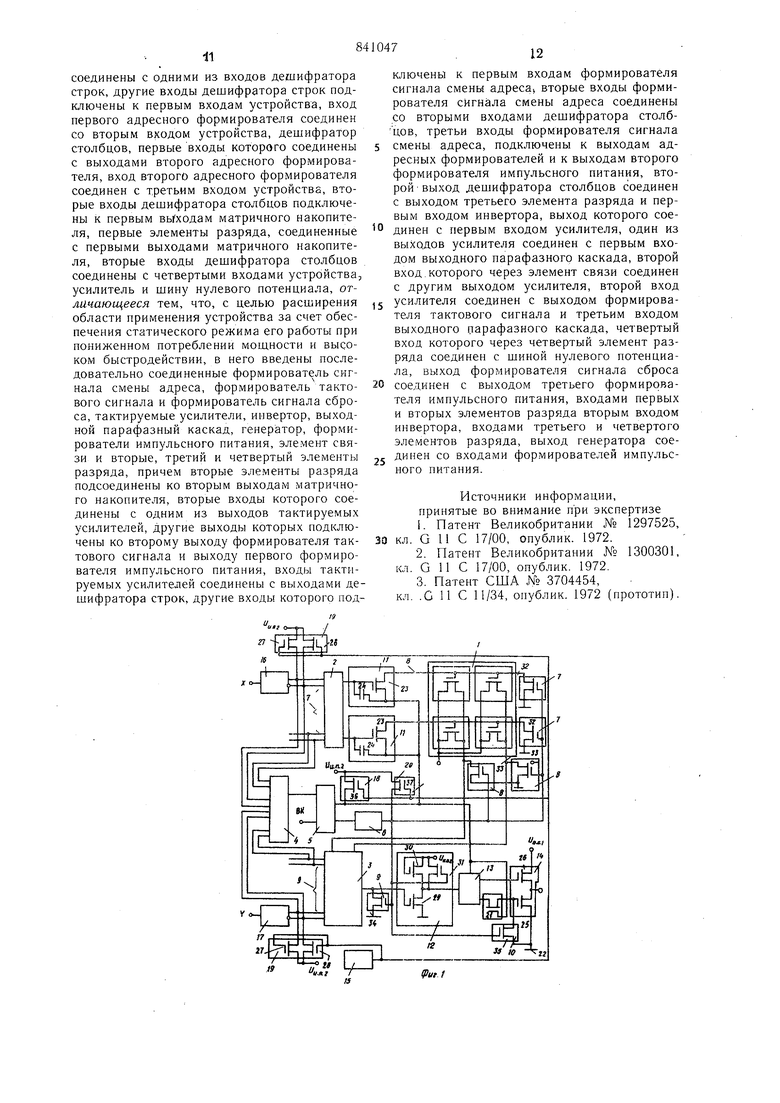

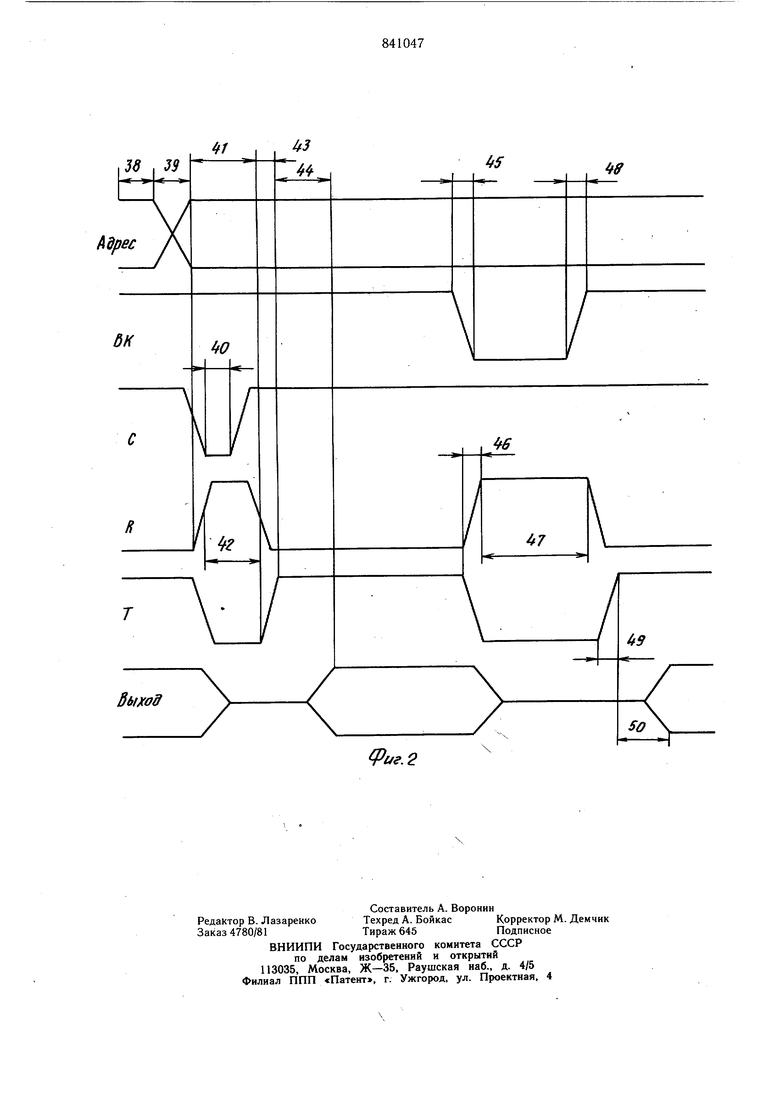

Изобретение относится к вычислительной технике, в частности к полупроводниковым постоянным запоминающим устройствам (ПЗУ), применяемым в аппаратуре с цифровой обработкой информации, преимущественно в цифровых системах обработки данных с магистральной организацией внешних устройствах ЭВМ-и ЦВМ специального назначения, мини- и микро-ЭВМ в качестве устройств последовательного управления, преобразователей кодов, генераторов символов, генераторов тригонометрических функций, для синтеза произвольных логических комбинаций, для хранения программ, подпрограмм, табличных данных, констант и т.д. Известно ПЗУ, содержащее множество адресных формирователей, матрицу памяти, дешифратор строк, дешифратор столбцов, устройство считывания 1. Недостатком этого ПЗУ является необходимость четырех внешних импульсных управляющих сигналов-Ф -Ф4. Известно также ПЗУ, содержащее матрицу памяти, дешифратор адреса, синхронизатор фазовых сигналов, устройство считывания 2. Недостатком этого ПЗУ является необходимость двух внещних фазовых управляющих сигналов Ф1 и Ф2. Наиболее близким по технической сущности является ПЗУ, которое содержит множество формирователей адресных сигналов, матрицу памяти, в которой в качестве запоминающего элемента использован МДП-транзистор, дешифратор строк, дещифратор столбцов, усилитель выходного сигнала, разрядный транзистор строчной шины матрицы памяти 3. Недостатком известного устройства является динамический режим работы, требующий внешних чередующихся первых и вторых фазовых сигналов Ф1 и Ф2, что предъявляет дополнительные высокие требования к внешним устройствам формирования фазрвых сигналов и значительно усложняет аппаратуру, в которой используется данное ПЗУ. Цель изобретения - расширение области применения ПЗУ за счет обеспечения статического режима работы при пониженной потребляемой мощности и высоком быстродействии. Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее матричный накопитель, первый адресный формирователь, выходы которого соединены с одними из входов дещифратора строк, другие входы дешифратора строк подключены к первым входам устройства, вход первого адресного формирователя соединен со вторым входом устройства, дешифратор столбцов, первые входы которого соединены с выходами второго адресного формирователя, вход второго адресного формирователя соединен с третьим входом устройства, вторые выходы дешифратора столбцов подключены к первым выходам матричного накопителя, первые элементы разряда, соединенные с первыми выходами матричного накопителя, вторые входы дешифратора столбцов соединены с четвертыми входами устройства, усилитель и щину нулевого потенциала, введены последовательно соединенные формирователь сигнала смены адреса, формирователь тактового сигнала и формирователь сигнала сброса, тактируемые усилители, инвертор, выходной пара;фазный каскад, генератор, формирователи импульсного питания, элемент связи и вторые, третий и четвертый элементы разряда, причем вторые элементы разряда подсоединены ко вторым выходам матричного накопителя, вторые входы которого соединены с одним из выходов тактируемых усилителей, другие выходы которых подключены ко второму выходу формирователя тактового сигнала и выходу первого формирователя импульсного питания, входы тактируемых усилителей соединены с выходами дешифратора строк, другие входы которого подключены к первым входам формирователя сигнала смены адреса, вторые входы формирователя сигнала смены адреса соединены со вторыми входами дешифратора столбцов, третьи входы формирователя сигнала смены адреса подключень к входам адресных формирователей и к выходам второго формирователя импульсного питания, второй выход дещифратора столбцов соединен с выходом третьего элемента разряда и первым входом инвертора, выход которого соединен с первым входом усилителя, один из выходов усилителя соединен с первым входом выходного парафазного каскада, второй вход которого через элемент связи соединен с другим выходом усилителя, второй вход усилителя соединен с выходом формирователя тактового сигнала и третьим входом выходного парафазного каскада, четвертый вход которого через четвертый элемент разряда соединен с шиной нулевого потенциала, выход формирователя сигнала сброса соединен с выходом третьего формирователя импульсно го питания, входами первых и вторых элементов разряда, вторым входом инвертора, входами треуьего и четвертого элементов разряда, выход генератора соединен со входами формирователей импульсного питания. На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 временная диаграмма работы устройства. Устройство содержит матричный накопитель 1, дешифратор 2 строк, дешифратор 3 столбцов, формирователь 4 сигнала смены адреса, формирователь 5 тактового сигнала. формирователь 6 сигнала сброса, элементы 7-10 разряда, тактируемые усилители 11, инвертор 12, усилитель 13, выходной парафазный каскад 14, генератор 15, адресные формирователи 16 и 17, формирователи 18- 20 импульсного питания, элемент 21 связи, шину 22 нулевого потенциала. Каждый тактируемый усилитель 11 выполнен на транзисторе 23 и конденсаторе 24. Выходной парафазный каскад выполнен на транзисторах 25 и 26, формирователь 19 импульсного питанияна транзисторах 27 и 28, инвертор 12 - на транзисторах 29-31. Элементы 7-10 разряда выполнены также на транзисторах 32- 35, а формирователи импульсного питания 18-20 - на транзисторах 36 и 37. На фиг. 2 представлены сигналы и их составные части, имеющие нумерацию 38--50. Предлагаемое устройство является ПЗУ, программируемым фотощаблоном в условиях изготовления. Запись информации в матричный накопитель 1 ПЗУ осуществляется на одной из фотолитографических операций при использовании сменного фотошаблона, изготовленного в соответствии с картой заказа. При записи единицы в запоминающий элемент под его затвором выращивается толстый окисел, при записи нуля - тонкий окисел. Для считывания информации, записанной в ячейку памяти (запоминающий элемент) ПЗУ, на входы устройства подается определенная комбинация адресных сигналов, соответствующая адресуемой ячейке. Адресные сигналы поступают на входы адресных формирователей 16 и 17, которые усиливают адресные сигналы, формируют прямой и инверсный сигналы, обеспечивая минимальные задержки и крутые фронты этих сигналов. Имеются две группы адресных сигналов: сигналы X и сигналы У. Каждому адресному сигналу соответствует свой формирователь 16 или 17. Прежде чей описать принцип работы ПЗУ, т.е. считывание информации из него, рассмотрим внутреннюю систему тактовых сигналов ПЗУ, позволивших построить отдельные периферийные схемы устройства по динамическому принципу, обеспечивая этим высокое быстродействие при минимальной потребляемой мощности, несмотря на чисто статический режим работы ПЗУ, нетребующий внешних специальных запускающих сигналов. Предлагается следующая система внутренних тактовых сигналов (фиг. 2): вспомогательный сигнал «смена адресного сигнала С, сигнал сброса R, сигнал тактирования Т. Формирование этих сигналов осуществляется функциональными узлами 4-6. В исходном состоянии в момент времени 38, когда устройство выбрано, т.е. сигнал на управляющем входе «Выбор кристалла (ВК.) равен логической единице и не изменяется, установилась вполне определенная комбинация адресных сигналов на адресных входах; на выходе формирователя 4 сигнал; С и на выходе формирователя 5 сигнал Т равен логической единице, а на выходе формирователя 6 сигнал Р равен логическому нулю. Предполагается, что для процессов в ПЗУ, описываемых ниже, сигнал на входе ВК по-прежнему остается равным логической единице. Каждый прямой и инверсный выходы формирователей 16 и 17 адресных сигналов X и У соединен с определенным входом формирователя 4, отсюда при появлении новой комбинации адресных сигналов на адресных входах ПЗУ в интервале времени 39 происходит соответствующее изменение сигналов на прямых и инверсных выходах формирователей 16 и 17, фронтами которых запускается формирователь 4. В результате выход формирователя 4 переходит из состояния логической единицы в состояние логического нуля, т.е. на этом выходе формируется передний фронт вспомогательного отрицательного импульса С, который запускает формирователь 5. На другом выходе формирователя 5 с минимальной задержкой относительно переднего фронта отрицательного импульса С формируется, дополнительный сигнал, запускающий формирователь 6, выход которого переходит из состояния логического нуля в состояние логической единицы, т.е. формируется передний фронт положительного импульса сброса R, первый выход формирователя 5 переходит из состояния логической единицы в состояние логический нуль, т.е. происходит сброс тактового сигнала Т. Длительность отрицательного импульса С, т.е. интервал времени 40, определяется параметрами внутренних элементов формирователя 4 и длительностью фронтов прямых и инверсных сигналов на выходе формирователя 16 и 17. Через интервал времени 40 выход формирователя 4 переходит из состояния логический ноль в состояние логической единицы, т.е. формируется задний фронт отрицательного импульса С, которым изменяется логическое состояние выходов формирователей 5 и 6. На выходе формирователя 6 формируется задний фронт положительного импульса сброса R, а на выходе формирователя 5 формируется передний фронт положительного импульса - тактового сигнала Т. Таким образом, ввод формирователей 4- 6 в структурную схему ПЗУ позволил сформировать внутренние тактовые сигналы: положительный иТипульс сброса Р и сдвинутый с ним на интервал времени 41 положительный импульс тактирования Т, при условии изменения сигналов на адресных входах и при выборе данного ПЗУ. Адресный дешифратор устройства представляет собой двухмерную матрицу и состоит из двух дешифраторов: дешифратора 2 строк и дешифратора 3 столбцов. Адресуемая ячейка йамяти накопителя 1 находится на пересечении двух выбранных в данный момент щин: горизонтальной и вертикальной. Дешифратор 2 строк осушествляет доступ к строкам, дешифратор 3 столбцов - к столбцам матричного накопителя 1. Цикл считывания в ПЗУ начинается с появления новой комбинации адресных сигналов на адресных входах ПЗУ в интервале времени 39. Как было описано выше в начале цикла считывания формируются соответствующие импульсы С, R и Т. В интервале врмени 42 с помощью элементов 7-10 разрядов на затворы их транзисторов 32-35 поступает положительный импульс сброса R, который осуществляет обнуление, т.е. потенциал становится равным логическому нулю следующих шин и узлов ПЗУ, строки накопителя 1-транзистором 32, столбцы накопителя 1 -транзистором 33, затвор ключевого транзистора 29 инвертора 12 - транзистором 34, затвор нижнего транзистора 25 выходного парафазного каскада 14 - транзистором 35. Адресные сигналы X, X сформированные соответственно на прямых и инверсных выходах формирователя 16, поступают на входы дешифратора 2 строк. Причемкаждой из 2 (где .п - количество входов X) комбинации адресных сигналов X соответствует один вполне определенный возбужденный выход дещифратора 2, т.е. сигнал на этом выходе равен логической единице в то время, когда сигналы на всех остальных 1 выходах равны логическому нулю. Для усиления выходных, сигналов дешифратора 2 с целью повыщения быстродействия ПЗУ введены тактируемые усилители 11. К каждому выходу дещифратора 2 подключен свой усилитель 11, причем непосредственно к выходу дещифратора 2 подключены одна обкладка конденсатор 24 и затвор транзистора 23, тактируемого усилителя 11. Транзистор 23 и конденсатор 24 - элементы образующие тактируемый усилитель 11. Следует отметить, что емкость конденсатора 24 управляется напряжением. Исток транзистора 23 тактируемого усилителя 11 подключен к строчной щине накопителя 1, сток этого транзистора соединен с другой обкладкой конденсатора 24 и с выходом формирователя 5. В интервале времени 42 конденсатор 24, подключенный к возбужденному выходу дешифратора 2, предзаряжается так, что на затворе транзистора 23 тактируемого усилителя 11 появляется положительный потенциал относительно стока транзистора 23, имеющего в этот момент времени нулевой потенциал, в результате емкость конденсатора 24 возрастает и становится значительно больше, чем суммарная емкость затвора транзистора 23 и паразитная емкость выхода дешифратора 2. Конденсаторы, подключенные ко всем остальным невозбужденным выходам, остаются незаряженными и имеют малую емкость, что делает небольшой емкостную нагрузку выхода формирователя 5 и способствует повышению быстродействия ПЗУ. В интерва-ле времени 43 на выходе формирователя 5 формируется передний фронт положительного импульса тактирования Т, т.е. потенциал на выходе формирователя 5 возрастает. Это изменение через конденсатор 24 большой емкости тактированного усилителя 11, подключенного к возбужденному выходу дешифратора 2, передается на затвор транзистора 23, в остальных усилителях 11 такая передача не осуш,ествляется и потенциал на затворах транзисторов 23 остается равным логическому нулю. По истечении времени 43, когда на выходе формирователя 5 сформирован сигнал Т, уровень которого равен логической единице и близок к Un.nj, напряжение на затворе транзистора 23, подключенного к .возбужденному выходу дешифратора 2, оказывается существенно выше ии.п.ь а это позволяет получить напряжение на строчной шине накопителя 1-, подключенной к указанному транзистору 23, т.е. выбранной шине, равное или примерно равное Уи.п.г.В то время, как на остальных невыбранных строчных шинах накопителя 1 потенциала остается равным нулю. Помимо возможности получения высокого уровня выходного сигнала дешифратора 2 строк ввод описанного тактированного усилителя 11 дает существенно меньшую длительность фронта нарастания сигнала на выбранной строчной шине накопителя 1, несмотря на большую величину ее емкости, а в целом все это способствует повышению быстродействия ПЗУ. Адресные сигналы У и У, сформированные на прямых и инверсных выходах формирователя 17, поступают на входы дешифратора 3 столбцов, которы.й осуществляет подключение одного ит 2 (где к - количество входов У) выбранного столбца накопителя 1 ко входу инвертора 12, а именно, к затвору его транзистора 29. Таким образом, в результате декодирования адреса по истечении интервала времени 43 на затворе транзистора накопителя 1 адресуемой ячейки памяти сформирован потенциал близкий к U,.M.JL, а HCTOJi; транзистора накопителя 1, соединенный с : выбранным столбцом матрицы, элементами дешифратора 3 подсоединен к затвору транзистора 29 инвертора 12. Так как сток транзистора накопителя 1 подключен к U.. , то при записи нуля в адресуемую ячейку памяти накопителя на затворе транзистора 29 инвертора 12 образуется потенциал, равный логической единице, а при записи единицы сохраняется потенциал, равный логическому нулю, образованный в результате обнуления инвертора 12 в интервал времени 42 элементом разряда 9. Итак, по истечении интервала времени 43 информация, записанная в накопитель 1, поступает на вход устройства вывода данных, включающая элемент 10 разряда, инвертор 12 и усилитель 13, выходной парафазный каскад 14, элемент 21 связи. Назначение этого устройства - усиление, вывод данных, считанных из накопителя 1 на выходы ПЗУ, обеспечение возможности работы на емкостную и резистивную нагрузку. Введенный в устройство инвертор 12 построен по динамическому принципу. Транзисторы 29 и 31 инвертора 12 образуют характерную схему «без отнощения. В начале цикла считывания в интервале времени 42 положительным импульсом сброса R обнуляется затвор транзистора 29, одновременно открывается транзистор 31, так как на его затвор подается сиглал R и через транзистор 31 емкость С е,ых (емкость выходного узла инвертора 12 перезаряжается до напряжения, близкого к Un.ji.no истечении интервала времени 43, в интервале времени 44, т.е. когда уровень сигнала R равен логическому нулю, а исток транзистора накопителя 1 подключен к затвору транзистора 29 инвертора 12, при считывании единицы на выходе инвертора 12 сохраняется потенциал, близкий к UU.M... при считывании нуля формируется потенциал, равный логическому нулю в результате разряда емкости Свь1хчерез открытый транзистор 29. Ввод инвертора 12, построенного по динамическому принципу в виде схемы «без отношения повышает быстродействие ПЗУ, так как позволяет сделать одновременно транзисторы 29 и 31 инвертора 12 с высокой крутизной, что снижает рассеиваемую мощность. Транзистор 30 инвертора 12 имеет низкую крутизну характеристики и введен только для обеспечения работоспособности инвертора 12 в статике, т.е. при длительном считывании информации. Сигнал с выхода инвертора 12 поступает на вход усилителя 13, который осуществляет его усиление и преобразование в парафазный сигнал, поступающий на затворы транзисторов 25 и 26 выходного парафазного каскада 14. Если описываемое ПЗУ выбрано, то вначале цикла считывания по ист.ечении интервала времени 43 на выходе

формирователя 5 формируется сигнал Т, равный логической единице. Так как этот выход формирователя 5 соединен с усилителем 13 и с затвором транзистора элемента 21 связи, то в интервале времени 44, считанный из накопителя 1 и усиленный усилителем 13 сигнал с одного выхода усилителя 13 поступает непосредственно на затвор верхнего транзистора 26 каскада 14, а с другого выхода усилителя 13 инверсный описанному выше сигналу через открытый транзистор элемента 21, поступает на затвор нижнего транзистора 25 выходного парафазного каскада 14. Двухтактный принцип построения выходного каскада 14 позволяет использовать транзисторы 26 и 25 очень высокой крутизны, обеспечивая этим малые фронты выходного сигнала при большой емкости нагрузки и низкую рассеиваемую мощность. Кроме этого/транзисторы 26 и 25 выбраны taK, что возможна работа на заданную резистивную нагрузку. Парафазный выходной каскад 14 и связанные с ним элементы 21 и 10 обеспечивают возможность объединения выходов ПЗУ по «проводному ИЛИ. Указанные свойства введенного парафазного каскада 14 и элементов 21 и 10 улучшают быстродействие, уменьшают рассеиваемую мощность ПЗУ, расширяют область его применения.

Рассмотрим работу ПЗУ в режиме «Невыбор, т.е. когда сигнал на входе ВК равен логическому нулю. Предположим, что в интервале времени 45 сигнал на входе ВК формирователя- 5 изменяется от уровня, равного логической единице, до уровня, равного логическому нулю, так как управляющий сигнал ВК непосредственно поступает на вход формирователя 5, то на его одном выходе в интервале времени 46 формируется сигнал Т, равный логическому нулю, а на его другом выходе дополнительный сигнал, способствующий формированию на выходе формирователя 6 сигнала R, равного логической единице. В результате в интервале времени 47, т.е. тогда, когда сигнал на входе ВК формирователя 5 равен логическому нулю, сигнал сброса R равен логической единице, сигнал тактирования Т равен логическому нулю, при этом обнуляются горизонтальные и вертикальные шины накопителя 1, затвор транзистора 29, затвор транзистора 25 элементами 7-10 разряда, а на затворе транзистора 26 усилитель 13 формирует потенциал равный логическому нулю, затвор транзистора 25 отключается от выхода усилителя 13 транзистором элементом 21 связи, на затвор которого поступает сигнал Т. Выход ПЗУ переходит в состояние «высокого импеданса, что позволяет соединять выходы ПЗУ по «проводному ИЛИ. При переходе ПЗУ из режима «Невыбор в режим «Выбор в интервале времени 8, т.е. когда

сигнал на входе ВК формирователя 5 переходит от уровня логического нуля к уровню логической единицы, в то время как сигналы на адресных входах не изменяются, на одном выходе формирователя 5 формируется

сигнал Т равный логической единице, на выходе. формирователя 6 формируется сигнал R, равный логическому нулю. В интервалах времени 49 и 50 в ПЗУ происходят процессы, идентичные описанным выше процессам, происходящим в интервалах времени 43 и 44.

В ПЗУ введен генератор 15, работающий в режиме автоколебаний. Незначительные флуктуации токов в элементах генератора 15 при включении напряжения питания приводят к возникновению колебательного процесса в генераторе 15, на выходе которого формируются прямоугольные импульсы, амплитуды которых больше ик-п.г, а частота равна 5 МГц. Выходной сигнал генератора 15 поступает на затворы транзисторов 27, 28, 36 и 37. Из-за наличия паразитных токов утечки в ПЗУ возможно недопустимое уменьшение уровней сигналов логической единицы на прямых и инверсных вы-, ходах формирователей 16 и 17, выходе формирователя 5, на выходе формирователя 6 при длительном считывании, т.е. в статике, что не гарантирует работоспособность ПЗУ в этом режиме. Ввод в ПЗУ генератора 15, элементов импульсного питания 18-20 и соединение затворов транзисторов этих элементов с выходом генератора 15 обеспечивает работоспособность ПЗУ в статике путем импульсной подпитки выходов формирователей J6, 17, 5 и 6 и поддержания уровней сигналов логической единицы на этих выходах, близких к напряжению (ц .

Техническое преимущество изобретения, создаваемый им положительный эффект заключается в том, что благодаря введению допо4вительных функциональных блоков, элементов и связей, не ведущих к значительному усложнению конструкции ПЗУ, расширяется область его применения за счет обеспечения статического режима работы при низкой потребляемой мощности и высоком быстродействии, т.е. такого режима работы, при котором ПЗУ не требует внешних фазовых сигналов, благодаря чему исключаются внешние устройства формирования фазовых сигналов и высокие требования к ним, на 50% уменьщается объем периферийных устройств, обслуживающих ПЗУ в аппаратуре, повыщается в целом надежность аппаратуры.

Формула изобретения

Постоянное запоминающее устройство, содержащее матричный накопитель, первый адресный формирователь, выходы которого соединены с одними из входов дешифратора строк, другие входы дешифратора строк подключены к первым входам устройства, вход первого адресного формирователя соединен со вторым входом устройства, дешифратор столбцов, первые входы которого соединены с выходами второго адресного формирователя, вход второго адресного формирователя соединен с третьим входом устройства, вторые входы дешифратора столбцов подключены к первым вьfxoдaм матричного накопителя, первые элементы разряда, соединенные с первыми выходами матричного накопителя, вторые входы дешифратора столбцов соединены с четвертыми входами устройства усилитель и шину нулевого потенциала, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения статического режима его работы при пониженном потреблении мощности и высоком быстродействии, в него введены последовательно соединенные формирователь сигнала смены адреса, формирователь тактового сигнала и формирователь сигнала сброса, тактируемые усилители, инвертор, выходной парафазный каскад, генератор, формирователи импульсного питания, элемент связи и вторые, третий и четвертый элементы разряда, причем вторые элементы разряда подсоединены ко вторым выходам матричного накопителя, вторые входы которого соединены с одним из выходов тактируемых усилителей, другие выходы которых подключены ко второму выходу формирователя тактового сигнала и выходу первого формирователя импульсного питания, входы тактируемых усилителей соединены с выходами де шифратора строк, другие входы которого ключены к первым входам формирователя сигнала смены адреса-, вторые входы формирователя сигнала смены адреса соединены со вторыми входами дешифратора столбцов, третьи входы формирователя сигнала смены адреса, подключены к выходам адресных формирователей и к выходам второго формирователя импульсного питания, второй выход дешифратора столбцов соединен с выходом третьего элемента разряда и первым входом инвертора, выход которого соединен с первым входом усилителя, один из выходов усилителя соединен с первым входом выходного парафазного каскада, второй вход.которого через элемент связи соединен с другим выходом усилителя, второй вход усилителя соединен с выходом формирователя тактового сигнала и третьим входом выходного парафазного каскада, четвертый вход которого через четвертый элемент разряда соединен с шиной нулевого потенциала, выход формирователя сигнала сброса соединен с выходом третьего формирователя импульсного питания, входами первых и вторых элементов разряда вторым входом инвертора, входами третьего и четвертого элементов разряда, выход генератора соеД нен со входами формирователей импульсного питания. Источники информации, принятые во внимание при экспертизе 1.Патент Великобритании № 1297525, кл. G И С 17/00, опублик. 1972. 2.Патент Великобритании № 1300301, кл. G 11 С 17/00, опублик. 1972. 3.Патент США № 3704454, кл. .С 11 С 11/34, опублик. 1972 (прототип).

из

1

Зв 39 4

бК

0

5

е

I

г

т

Biifxod

fPue.2

Авторы

Даты

1981-06-23—Публикация

1979-04-06—Подача