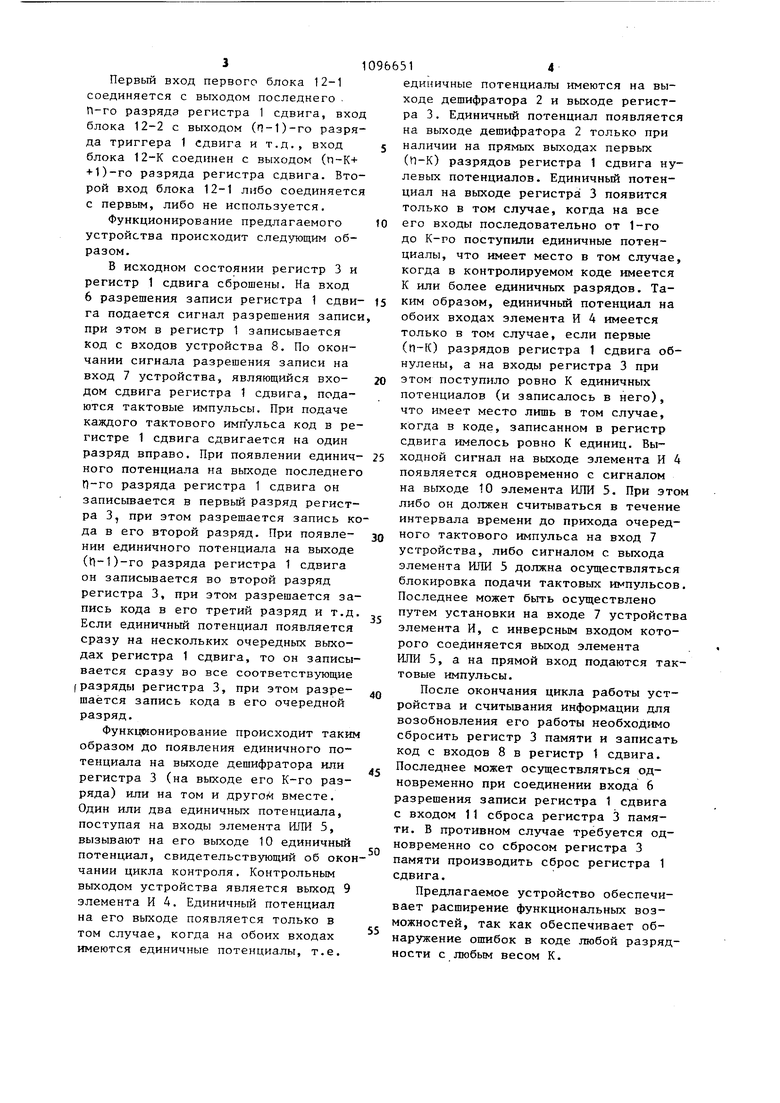

f Изобретение относится к автоматике и вычислительной технике и мОжет использоваться для построения различ ных устройств обработки дискретной информации. Известна схема контроля двух линий из шести, которая содержит первую логическую схему, входы которой соединены соответственно с двумя из шести линий, вторую логическую схему, входы которой соединены соответственно с выходом первой логической схемы и третьей входной шиной, а так же третью, четвертую и пятую логичес кие схемы, соединенные аналогичным образом lj . Недостатками этого устройства являются мал111е функциональные возможности, так как устройство позволяет контролировать только код 2 из 6, а также малая надежность функционирования ввиду аналогового принципа работы. Наиболее близким к изобретению по технической сущности является уст ройство для контроля параллельного двоичного кода на четность, содержащее два элемента И, регистр сдвига и триггер 2j . Недостаток известного устройства состоит в ограниченности его функциональных возможностей. Устройство мо жет вести контроль по четности, но не может вести контроль информации в кодах К из п . Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения контроля информации в кодах К из И . Поставленная цель достигается тем что в устройство для обнар гження ошибок в параллельном г) -разрядном коде, содержащее регистр сдвига, дешифратор и элемент И, причем информационные входы сдвига и записи регистра являются соответственно ин формационньми входами, тактовым входом и входом записи устройства, выходы младших (f1-K) разрядов регистра сдвига соединены с входами дешифрато ра, введен регистр и элемент ИЛИ, причем выходы К старших разрядов регистра сдвига соединены с информа ционными входами регистра, выход дешифратора соединен с первыми вход ми элементов И и ИЛИ, выход регистр памяти соединен со вторыми входами элементов И и ИЛИ, выходы которых 51 являются соответственно контрольным В1з1ходом и выходом конца контроля устройства, вход пуска устройства соединен с входом разрешения записи регистра. На фигр 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - схема регистра. Предлагаемое устройство содержит регргстр 1 сдвига, дешифратор 2, регистр 3, элемент И 4 и элемент ИЛИ 5. Первые (п-К) выходов (выходы первых (п-К) разрядов) регистра 1 сдвига соединены с входами дешифратора 2, а остальные К выходов - с входами регистра 3, выход которого, а также выход блока 2 контроля обнуления соединены с входами элемента И 4 и элемента ИЛИ 5. Устройство имеет вход 6 разрешения записи, тактовый вход 7, информационный вход 8, выход 9 контроля и выход 10 конца контроля устройства и вход 11 пуска устройства. Дешифратор 2 контроля обнуления может быть вьшолнен в виде элемента И, соединенного входами с инверсными выходами первых (п-К) разрядов регистра 1 сдвига (первым является крайний левый разряд), либо в виде элемента И с инверсными входами, соединенного с прямыми выходами первых (Г|-К) разрядов регистра 1 сдвига. Регистр 3 может быть выполнен (фиг. 2) в виде К блоков 12. Первый вход каждого блока соединен с входом регистра, а второй -- с вторым выходом предыдущего блока 12. Вход сброса регистра 3 соединен с входом 11 З стройства. Второй вход первого блока 12 соединен с входом 11 пуска устройства, а второй - с вторым выходом предыдущего блока 12, Каждый блок 12 состоит из триггера 13, соединенного прямым входом с выходом элемента И 14, первый вход которого является первым входом блока, а второй соединен с первым входом элемента И 15 и вторым входом блока. Второй вход элемента И 15 соединен с прямым выходом триггера 13, ЯВЛЯЮ1ЦИМСЯ первым вьшодом блока, выход элемента И 15 является вторым выходом блока. Инверсные входы всех триггеров 13 соединены с входом 16 сброса регистра. Выходом ,. регистра памяти является выход блока 12 К.

Первый вход первого блока 12-1 соединяется с выходом последнего . П-го разряда регистра 1 сдвига, вход блока 12-2 с выходом (П-1)-го разряда триггера 1 сдвига и т.д., вход блока 12-К соединен с выходом (п-К+ +1)-го разряда регистра сдвига. Второй вход блока 12-1 либо соединяется с первым, либо не используется.

Функционирование предлагаемого устройства происходит следующим образом.

В исходном состоянии регистр 3 и регистр 1 сдвига сброшены. На вход 6 разрешения записи регистра 1 сдвига подается сигнал разрешения записи при этом в регистр 1 записывается Код с входов устройства 8. По окончании сигнала разрешения записи на вход 7 устройства, являющийся входом сдвига регистра 1 сдвига, подаются тактовые импульсы. При подаче каждого тактового импульса код в регистре 1 сдвига сдвигается на один разряд вправо. При появлении единичного потенциала на выходе последнего П-го разряда регистра 1 сдвига он записьгоается в первый разряд регистра 3, при этом разрешается запись кода в его второй разряд. При появлении единичного потенциала на выходе (Ц-1)-го разряда регистра 1 сдвига он записывается во второй разряд регистра 3, при этом разрешается запись кода в его третий разряд и т.д Если единичный потенциал появляется сразу на нескольких очередных выходах регистра 1 сдвига, то он записывается сразу во все соответствующие (разряды регистра 3, при этом разрешается запись кода в его очередной разряд.

Функционирование происходит таким образом до появления единичного потенциала на выходе дешифратора или регистра 3 (на вьосоде его К-го разряда) или на том и другой вместе. Один или два единичных потенциала, поступая на входы элемента ИЛИ 5, вызывают на его выходе 10 единичный потенциал, свидетельствующий об окончании цикла контроля. Контрольным выходом устройства является выход 9 элемента И 4. Единичный потенциал на его выходе появляется только в том случае, когда на обоих входах имеются единичные потенциалы, т.е.

единичные потенциалы имеются на выходе дешифратора 2 и выходе регистра 3. Единичный потенциал появляется на выходе дешифратора 2 только при наличии на прямых выходах первых (П-К) разрядов регистра 1 сдвига нулевых потенциалов. Единичный потенциал на выходе регистра 3 появится только в том случае, когда на все его входы последовательно от 1-го до К-го поступили единичные потенциалы, что имеет место в том случае, когда в контролируемом коде имеется К или более единичных разрядов. Таким образом, единичный потенциал на обоих входах элемента И 4 имеется только в том случае, если первые (п-К) разрядов регистра 1 сдвига обнулены, а на входы регистра 3 при этом поступило ровно К единичных потенциалов (и записалось в него), что имеет место лишь в том случае, когда в коде, записанном в регистр сдвига имелось ровно К единиц. Выходной сигнал на выходе элемента И 4 появляется одновременно с сигналом на выходе 10 элемента ИЛИ 5. При это либо он должен считываться в течение интервала времени до прихода очередного тактового импульса на вход 7 устройства, либо сигналом с выхода элемента ИЛИ 5 должна осуществляться блокировка подачи тактовых импульсов Последнее может быть осуществлено путем установки на входе 7 устройств элемента И, с инверсным входом которого соединяется выход элемента ИЛИ 5, а на прямой вход подаются тактовые импульсы.

После окончания цикла работы устройства и считьшания информации для возобновления его работы необходимо сбросить регистр 3 памяти и записать код с входов 8 в регистр 1 сдвига. Последнее может осуществляться одновременно при соединении входа 6 разрешения записи регистра 1 сдвига с входом 11 сброса регистра 3 памяти. В противном случае требуется одновременно со сбросом регистра 3 памяти производить сброс регистра 1 сдвига.

Предлагаемое устройство обеспечивает расширение функциональных возможностей, так как обеспечивает обнаружение ошибок в коде любой разрядности с любым весом К.

12-1

12-2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в параллельном п-разрядном коде | 1986 |

|

SU1325482A2 |

| Пороговый элемент (его варианты) | 1980 |

|

SU1034188A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде | 1984 |

|

SU1168948A1 |

| Пороговый элемент | 1986 |

|

SU1368978A2 |

| Пороговый элемент | 1982 |

|

SU1091344A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Формирователь разновесных кодов | 1985 |

|

SU1297031A1 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ ОШИБОК В ПАРАЛЛЕЛЬНОМ -РАЗРЯДНОМ КОДЕ, содержащее регистр сдвига, дешифратор и элемент И, причем информационные входы сдвига и записи регистра являются соответственно информационными входами, тактовым входом и входом записи устройства, выходы младших (ц-К) разрядов регистра сдвига соединены с входами дешифратора, отличающее ся тем, что, с целью расширения его функциональных возможностей за счет обеспечения возможности контроля информации в кодах К из п , в устройство введен регистр и элемент ИЛИ, причем выходы К старших разрядов регистра сдвига соедине{ш с информационными входами регистра, выход дешифратора соединен с первыми входами элем-ентов И и ИЛИ, выход регистра соединен со вторыми входами элементов И и ИЛИ, выходы «оторых являются соответствен3 но контрольньн выходом и выходом конца контроля устройства, вход пуска устройства соединен с входом разрешения записи регистра. со 9) 9) on

Фш.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1974 |

|

SU530332A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-06-07—Публикация

1982-07-16—Подача