Вход

(Л

Изобретение относится к вычислительной технике и может быть использовано в электроизмерительных приборах.

Цель изобретения - повышение точности преобразования.

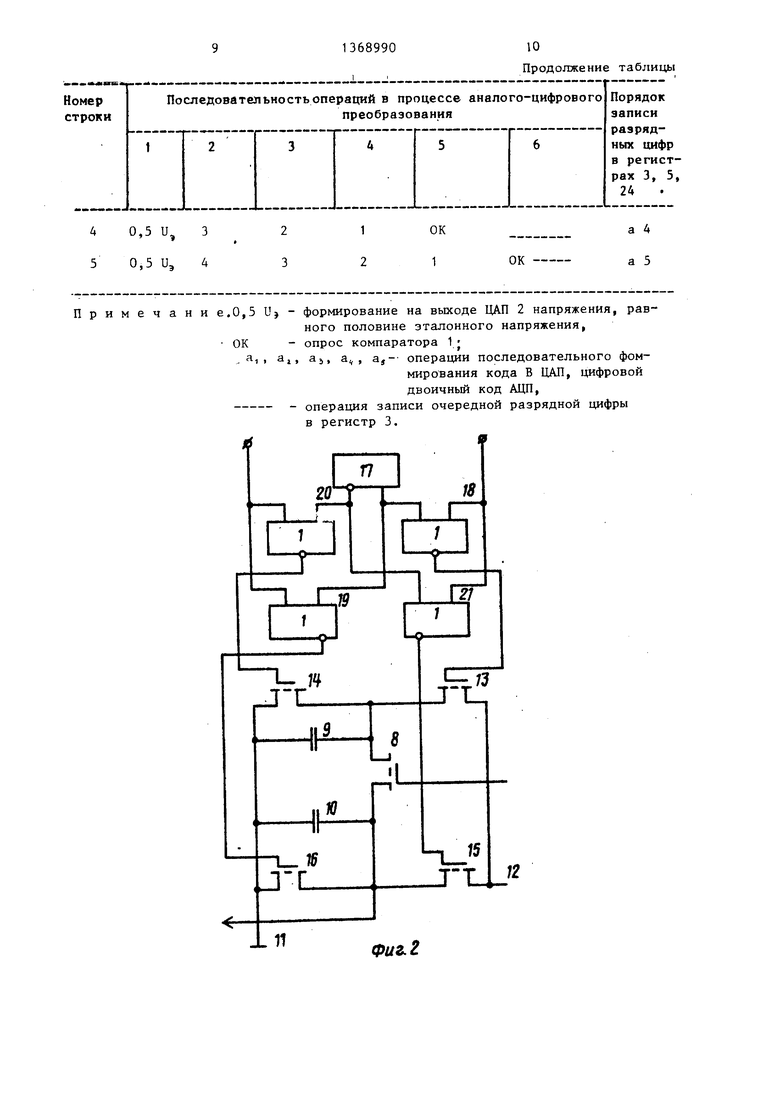

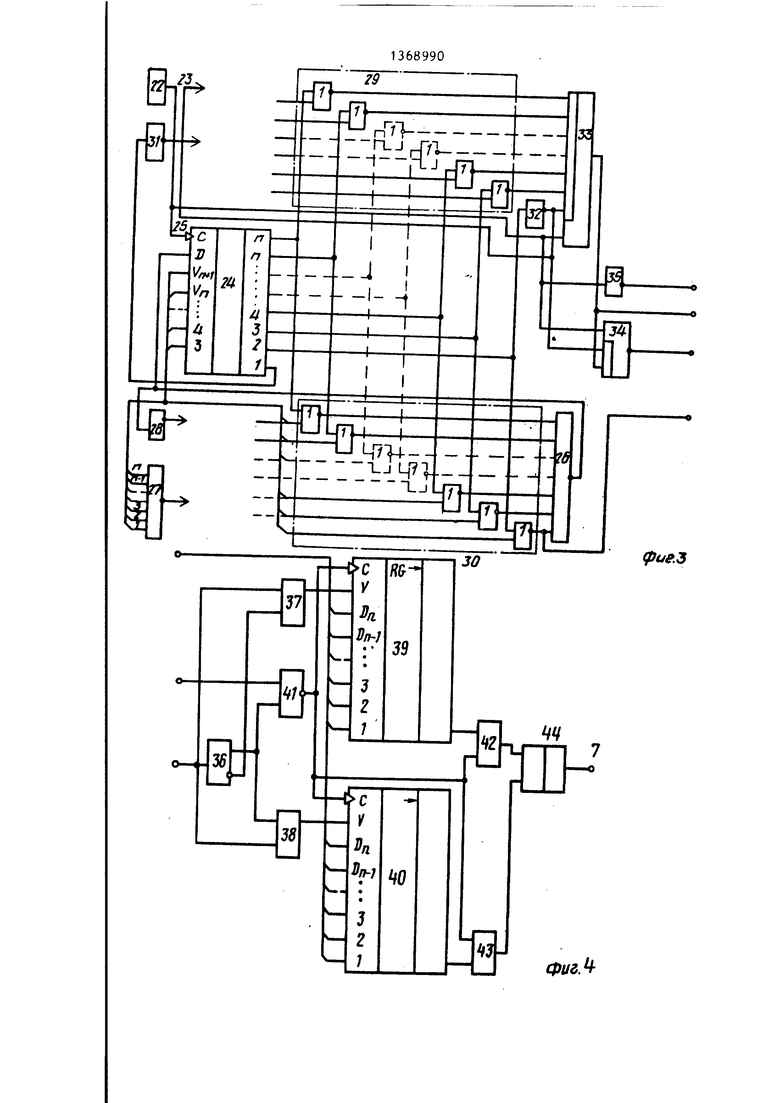

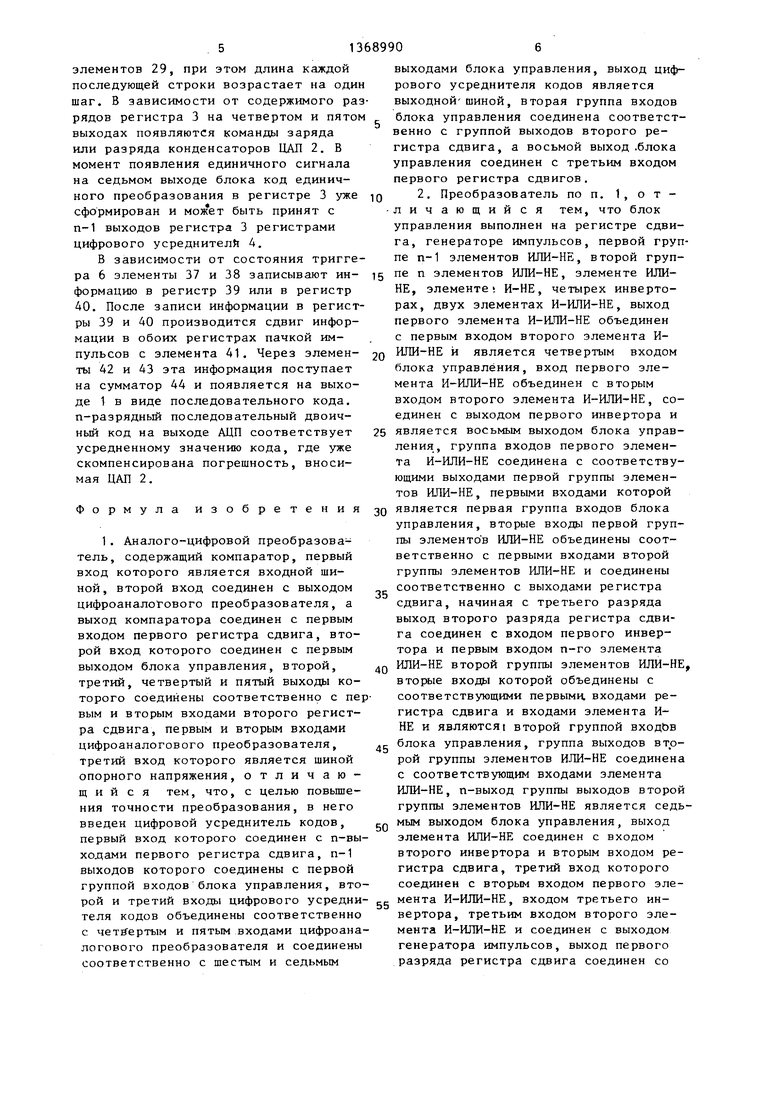

На фиг. 1 приведена функциональ- ная схема устройства; на фиг. 2 - фукциональная схема цифроаналогового преобразователя; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - функциональная схема цифрового усреднителя кодов.

Устройство содержит компаратор 1 цифроаналоговый преобразователь 2, первый регистр 3 сдвига цифровой усреднитель 4 кодов, второй регистр 5 сдвига, блок 6 управления, выходную шину 7,

Цифроаналоговый преобразователь (фиг. 2) содержит ключ 8, два накопительных элемента, выполненных на конденсаторах 9 и 10, общую шину 11,

вход 12, ключи 13-16, триггер 17, эл

крытые в этом также ключи 13 или 16 соответственно. Заряд конденсатора 9 производится в случае, если реализуемой разрядной цифрой является 1, а разряд конденсатора 10 производится в случае, если реализуемой разрядной цифрой является 0. В этом же первом такте на некоммутируемом конденсаторе ,(в случае реализации 1 , это конденсатор 10, а в случае реализации О, это конденсатор 9) осуществляется хранение напряжения, сформированного в предыдущем рабочем цикле ЦАП 2. Во втором такте, когда все заряжающие и разряжающие транзисторы заперты, производится отпирание ключа 8 и выравнивание напряжения на конденсаторах 9 и 10. Сумма напряжений на конденсаторах 9 и 10 при этом делится на два, что соответствует суммированию напряжения только что сформированного двоичного разряда с суммой напряжений разрядов, сформированных в пре

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1988 |

|

SU1594699A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1991 |

|

RU2013863C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Реверсивный аналого-цифровой преобразователь | 1986 |

|

SU1361710A1 |

| Преобразователь сигналов датчиков переменного тока | 1984 |

|

SU1182671A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1988 |

|

SU1615888A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2037267C1 |

| Электропривод переменного тока | 1986 |

|

SU1334342A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197078A1 |

Изобретение относится к вычислительной технике и может быть использовано в электроизмерительных приборах. Изобретение позволяет повысить точность преобразования. Это достигается тем, что разброс погрешностей циф- роаналогового преобразователя 2 компенсируется при цифровом усреднении двух следующих друг за другом преобразований цифровым усреднителем А кодов, который управляется с помощью регистров 3, 5 сдвига и блока 6 управления. 3 з.п. ф-лы, 4 ил., 1 табл.

менты ИЛИ-НЕ 18-21.

Блок 6 управления (фиг. 3) содержит генератор 22 импульсов, имеющий выход 23, регистр 24 сдвига с тактовым входом 25, элемент КПИ-НЕ , элемент И-НЕ 27, инвертор 28, первую группу 29 элементов ИЛИ-НЕ, вторую группу 30 элементов ИЛИ-НЕ, инверторы 31 и 32, элементы И-ИЛИ-НЕ 33 и

34, инвертор 35. I

Цифровой усреднитель 4 кодов (фиг. 4) содержит триггер 36, элементы И 37 и 38, регистры 39 и 40 сдвиг элемент ИЛИ-НЕ 41, элементы И 42 и 43, сумматор 44.

Аналого-цифровой преобразователь АЦП построен по принципу поразрядного уравновешивания с циклическим цифроаналоговым преобразователем 2 ЦАП в цепи обратной связи компаратора 1. При этом производится цифровое интегрирование и усреднение результата двух преобразований, проиводимых при взаимном изменении функций заряжаемого 9 и разряжаемого 10 конденсаторов.

Напряжение на выходе ЦАП, соответствующее одной разрядной цифре двоичного кода, формируется за два такта. В первом также производится либо заряд одного из конденсаторов, например конденсатора 9, либо разряд другого конденсатора 10 через отUj,, - (Uj-ь а;из).

где а; - разрядная цифра (О или 1).

Формирование напряжения, соответствующего двоичному коду, начинается с младшего разряда.

Основной составляющей погрешности ЦАП 2 является погрешность, связанная с относительным разбросом емкостей конденсаторов 9 и 10.

у

4С

5 )

0

где Д Де

c с.

-1--1 г 4. г - 7Г

2 2 Cj - номиналы емкостей конденсаторов .

Передаточная характеристика АЦП с 5 таким ЦАП имеет вид монотонной дугот образной кривой с максимальным отклонением от идеальной передаточной характеристики в центре в ту или другую сторону, в зависимости от знака &С.

Введение в ЦАП 2 второго ключа 15, триггера 17, элементов 18-21 позволяет одно из преобразований осуществить таким образом, что в качестве заряжаемого конденсатора ЦАП 2 выступает конденсатор 9, а в качестве разряжаемого конденсатора выступает конденсатор 10, а второе преобразование так, что конденсатор 10 становится

0

5

заряжаемым, а конденсатор 9 разряжаемым. Таким образом, после каждого 3 преобразований функции конденсаторов 9 и 10 взаимно изменяются, а погрешности аналого-цифрового преобразователя за счет разброса емкости онденсаторов 9 и 10 одинаковы по величине и имеют разный знак. Эти

погрешности компенсируются при цифро- ю подключенным к первому входу региством усреднении двух следующих друг за другом преобразований цифровым усреднителем 4.

При этом на вход триггера 17 пос- упает сигнал начала преобразования i изменяет его состояние на противоположное. Так происходит перед каждым преобразованием. На первые входы элементов 18 и 21 поступают нулевые соманды в зависимости от состояния риггера 17 включения одного из клю- ей 13 или 14. На первые входы поступают нулевые команды включения од- ого из ключей 14 или 16, в зависимости от состояния триггера 17. Вхо- цы элементов 18-21 связаны с выходами триггера 17 и соответствующими вы- одами блока 6, по которым поступают заряда и разряда конденсато- юв ЦДЛ 2 таким образом, что функци- |нирующие в данном преобразовании аряжающий и разряжающий ключи нахо- ,ятся в противоположных плечах ДАЛ 2. акое диагональное управление ключа- :и ДАЛ 2, когда функционирующие в даном преобразовании заряжающий и раз- яжающий ключи ЦАП 2 разделены запер- ым в первом такте преобразования лючом 8, позволяет заряжать до нап- яжения эталонного источника один из онденсаторов и одновременно разря- ать другой конденсатор. Такая опера- ия одновременного заряда и разряда онденсаторов необходима при форми- овании исходного для начала каждого реобразования напряжения 0,5 U на ыходе ЦАП 2 без дополнительных клю- ей.

Работа каждого из блоков устройст- а синхронизируется и управляется ре- истрами 3 и 5 и блоков 6. Последова- ельность операций в процессе преоб- азования приведена в таблице.

Циклическая развертка строки про- зводится регистром 24, на тактовый ход которого поступают им17ульсы с енератора 22. В начале каждой строки 13 второй вход регистра 24 производит :я запись нулевого сигнала, поступающего с выхода элемента 26. На первые входы регистра 24 поступают поочередно нулевые сигналы с выходов регист- ра 5, осуществляющего развертку кадра им измерения по строкам. Запись нулевого сигнала на второй вход регистра 5 осуществляется элементом 27, а сдвиг осуществляется инвертором 28,

ра 5. Сдвигом регистра 5 и записью регистра 24 управляет первая группа элементов 26, выходы которых подключены к входам элемента 26. Сдвиг нуля в регистре 24 происходит с первой ячейки до той, на входе которой нулевой сигнал. Нулевой сигнал перемещается от третьего к (п+1)-му разряду на один разряд после окончания каждой строки. Началу кадра преобразования соответствует появление единичного сигнала на седьмом выходе блока 6. Перед формированием каждой строки кадра измерения происходит опрос результата сравнения напряжения на выходе ЦАП 2 с входным напряжением АЦП. Этому соответствует появление нулевого сигнала на выходе регистра 24. При этом на второй вход регистра 3 поступает единичный сигнал с инвертора 31, а с выхода компаратора в первый разряд регистра 3 записывается информация с компаратора 1. Появление нулевого сигнала на втором выходе

регистра 24 вызывает сдвиг информации в регистре 3 за счет появления единичного сигнала на инверторе 32 и появление нулевых сигналов на выходах элементов 33 и 34. Появление двух

нулевых сигналов на четвертом и пятом блока выходах 6 соответствует командам заряда и разряда конденсаторов 9 и 10 ЦАП 2 одновременно. Эта операция в первом такте цикла формирования на выходе ЦАП 2 напряжения равного 0,5 и, возможна при диагональном управлении ключами ЦАП 2 с помощью триггера 17, элементов 18-21. Сигналы на четвертом и пятом выходах состробируются генератором 22 и их длительность составляет один такт генератора 22, т.е. равна половине периода. Во время второго такта генератора 22 всегда появляется единичный сигнал на выходе инвертора 35 и на шестом выходе блока 6.

Содержимое регистра 3 циклически опрашивается регистром 24 строчной развертки с помощью первой группы

5

элементов 29, при этом длина каждой последующей строки возрастает на од шаг. В зависимости от содержимого ррядов регистра 3 на четвертом и пят выходах появляются команды заряда или разряда конденсаторов ЦАП 2. В момент появления единичного сигнала на седьмом выходе блока код единичного преобразования в регистре 3 уж сформирован и может быть принят с п-1 выходов регистра 3 регистрами цифрового усреднители 4.

В зависимости от состояния триггра 6 элементы 37 и 38 записывают информацию в регистр 39 или в регистр АО. После записи информации в регисры 39 и 40 производится сдвиг информации в обоих регистрах пачкой импульсов с элемента 41. Через элементы 42 и 43 эта информация поступает на сумматор 44 и появляется на выходе 1 в виде последовательного кода, п-разрядный последовательный двоичный код на выходе АЦП соответствует усредненному значению кода, где уже скомпенсирована погрешность, вносимая ДАЛ 2.

Формула изобретения

дс блока управления, группа выходов вто рой группы элементов ИЛИ-НЕ соединен с соответствующим входами элемента ИЛИ-НЕ, п-выход группы выходов второ группы элементов ИЛИ-НЕ является сед мым выходом блока управления, выход элемента ИЛИ-НЕ соединен с входом второго инвертора и вторым входом ре гистра сдвига, третий вход которого соединен с вторым входом первого эле

группой входов блока управления, второй и третий входы цифрового усредни- gg мента И-ИЛИ-НЕ, входом третьего ин- теля кодов объединены соответственно вертора, третьим входом второго эле- с четвертым и пятым входами цифроана- мента И-ИЛИ-НЕ и соединен с выходом логового преобразователя и соединены генератора импульсов, выход первого соответственно с шестым и седьмым разряда регистра сдвига соединен со

0

5

20

35

зо

выходами блока управления, выход цифрового усреднителя кодов является выходной-шиной, вторая группа входов блока управления соединена соответственно с группой выходов второго регистра сдвига, а восьмой выход .блока управления соединен с третьим входом первого регистра сдвигов.

25 является восьмым выходом блока управления, группа входов первого элемента И-ИЛИ-НЕ соединена с соответствующими выходами первой группы элементов ИЛИ-НЕ, первыми входами которой является первая группа входов блока управления, вторые входы первой группы элементов ИЛИ-НЕ объединены соответственно с первыми входами второй группы элементов ИЛИ-НЕ и соединены соответственно с выходами регистра сдвига, начиная с третьего разряда выход второго разряда регистра сдвига соединен с входом первого инвертора и первым входом п-го элемента

ИЛИ-НЕ второй группы элементов ИЛИ-НЕ вторые входы которой объединены с соответствующими первыми, входами регистра сдвига и входами элемента И- НЕ и являютсяI второй группой входЬв

дс блока управления, группа выходов второй группы элементов ИЛИ-НЕ соединена с соответствующим входами элемента ИЛИ-НЕ, п-выход группы выходов второй группы элементов ИЛИ-НЕ является седьмым выходом блока управления, выход элемента ИЛИ-НЕ соединен с входом второго инвертора и вторым входом регистра сдвига, третий вход которого соединен с вторым входом первого эле50

gg мента И-ИЛИ-НЕ, входом третьего ин- вертора, третьим входом второго эле- мента И-ИЛИ-НЕ и соединен с выходом генератора импульсов, выход первого разряда регистра сдвига соединен со

входом четвертого инвертора, выходом которого является первый выход блока управления, пятый и шестой выходы которого являются соответственно выходами второго элемента И-ИЛИ-НЕ и третьего инвертора, выходы второго инвертора и элемента И-НЕ являются соответственно вторым и третьим выходами блока управления.

а выход соединен с объединенными так- 25 третьего и четвертого ключей, вход

товыми входами первого и второго регистров сдвига, первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с выходами первого и второго регистров сдвига, а выходы третьего

четвертого элементов И соединены :;оответственно с первым и вторым входами сумматора, выход которого явля- гтся выходом цифрового усреднителя.

30

последнего из которых объединен с входом первого ключа, первыми выхода ми первого и второго конденсаторов и является общей шиной, выход четвертого ключа объединен с выходами пятого и второго ключей, вторым выво дом второго конденсатора и является выходом цифроаналогового преобразователя, вход второго ключа объединен с входом третьего ключа и явля....,

1нформационные входы регистров пораз- ется третьим входом цифроаналогового зядно объединены и являются первымипреобразователя, выход третьего клю ходами цифрового усреднителя кодов,ча объединены с выходом первого клю1торые входы первого и второго эле- iBHTOB И являются третьим входом циф- ового усреднителя кодов.

40

ча, вторым выводом первого конденсатора и соединен со входом пятого ключа, управляющий вход которого является четвертым входом цифроаналогового преобразователя.

4, Преобразователь по п. 1, о т - ичающийся тем, что цифро.10

-п 3689908

аналоговый преобразователь выполнен на четьфех элементах ИЛИ-НЕ, двух накопительных элементах, выполненных на конденсаторах, пяти ключах, триггере, счетным входом которого является пятый вход цифроаналогового преобразователя, инверсный выход триггера соединен с первыми входами первого и второго элементов ИЛИ-НЕ, прямой выход соединен с первыми входами третьего и четвертого элементов ИЛИ- НЕ, второй вход первого элемента ИЛИ- НЕ объединен со вторым входом четвертого элемента ИЛИ-НЕ и является вторым входом цифроаналогового преобразователя, второй вход третьего элемента ИЛИ-НЕ объединен со вторым входом второго элемента ИЛИ-НЕ и является первым входом цифроаналогового преобразователя, выходы первого, второго, третьего и четвертого элементов ИЛИ-НЕ соединены соответственно с управляющими .входами первого, второго

15

0

последнего из которых объединен с входом первого ключа, первыми выходами первого и второго конденсаторов и является общей шиной, выход четвертого ключа объединен с выходами пятого и второго ключей, вторым выводом второго конденсатора и является выходом цифроаналогового преобразователя, вход второго ключа объединен с входом третьего ключа и явля

ча, вторым выводом первого конденсатора и соединен со входом пятого ключа, управляющий вход которого является четвертым входом цифроаналогового преобразователя.

0,5 и, 3 0,5 и, 4

- - -- - - - -- -.-.«-и.-..и....,

Примечание.О,5U,- формирование на выходе ЦАП 2 напряжения, равного половине эталонного напряжения, - опрос компаратора 1

ОК

1 1. а,,, а , а,-- операции последовательного фоммирования кода В ЦАП, цифровой двоичный код АЦП,

- операция записи очередной разрядной цифры в регистр 3.

±11

OK 1

OK

а 4 а 5

Фиг. 2

г

чч

Авторы

Даты

1988-01-23—Публикация

1984-08-01—Подача