тре., RS-триггере, дешифраторе, цифр.овом блоке сравнения, первые, входы .которого объединены с соответствующими управляющими входами коммутатора, соответствующими информационными входами дешифратора и подключены к соот. ветствующим выходам счетчика, вторые являются пятыми входами блока управления, выход подключен к первому адресному входу постоянного запокинающего устройства, второй адресный вход которого подключен к выходу коммутатора, третий.и четвертый адресные входы являются соответственно первым и тре.ть.им входами блока управления, пятый, шестой, седьмой и восьмой адресные входы подключены соответственно к первому, второму, -третьему и четвертому выходам регистра, управляющий вход объединен с первым управляющим входом регистра и пйдключен к выходу генератора импульсов, .первый выход подключен к первому управляющему входу счетчика, второй выход - к управляющему входу дешифратора, третий, четвертый, пятый, шестой, седьмой, восьмой и девят.ый выходы являются соответственно вторым третьим., че.тве.ртым, пятым, шестым, BocbMbiM, де вятым выходами блока управления, десятый выход подключен к S-входу. RS-тригге.ра, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый выходы подключены соответственно к первому, второму, третьему и четвертому .информационным входам регистра, второй управляющий вход которого объединен с R-входом RS-триггера,. вторым управляющим входом счетчика и является четвертым входом блока управления, при этом в.ыход RSтриггера является первым выходом .блока управления, выходы дешифратора являются седьмыми выхода ми блока управления, информационные входы коммутатора являются вторьтми. входами блока управления.

( . . .

3. Преобразователь по п. 1 отличающийся тем, что блок синтеза кодов выполнен на т-1 элементах И, где m - число переходных комбинаций избыточного измерительного кода (т .п - 2 для кода Фибоначчи, где п - количество разрядов аналогоцифрового преобразователя), m - 1 инверторах, m элементах -ИЛИ, первые входы которых являются первыми вхо- . дами блока синтеза кодов, вторые входы .- вторыми входами блока синтеза у кодов и объединены, заисключением второго входа т-го :элемента ИЛИ, -с входами соответствующих т-1 инве.рторов, выход первого элемента ИЛИ, выходы т-1 элементов И и п-т шин постоянного сигнала логического О являются выходами блока синтеза кодов, причем первые, входы т-1 элементов И подключены к выходам соответствующих т-1 элементов РШИ, вторые входы .объединены между собой, и подключены к выходу первого инвертора, выходы с второго по т-1 инверторов соответственно подключены к соответствующим третьим и остальным т-3 входам соответствующих т-2 элементов И. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221755A1 |

| Устройство цифро-аналогового преобразования | 1985 |

|

SU1312739A1 |

| Аналого-цифровой преобразователь | 1987 |

|

SU1522400A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Устройство цифроаналогового преобразования | 1986 |

|

SU1405117A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1790030A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1288913A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Цифроаналоговый преобразователь | 1982 |

|

SU1051701A1 |

1. АНАЛОГО-Ц ФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок управления, блок сравнения, цифроаналоговый преобразователь, вьрсод которого подключен к первому входу блока сравнения, выход крто.рргр подключен к первому входу блока управления, отличающийся тем, что, с целью повышения его точности, в него введены первый и второй счетчики, аналоговый запоминающий блок, блок синтеза кодов, блок цифровых схем сравнения, блок регистров, элемент . ИЛИ и переключатель, управляющий вход которого подключен к первому выходу блока управления, выход соединен с вторым входом блочка сравнения, первый информационный вход является входной шиной преобразователя, а второй информационный вход подключен к выходу аналогового запоминающего блока, управляющий вход которого подключен к второму выходу блока управления, а информационный вход подключен к выходу цифроаналого ЕОго преобразователя, входы которого объединены с соответствующими вторыми входами блока управления, первыми входами блока синтеза кодов, блока цифровых схем сравнения и информационными входами блока регистров и подключены к соответствующим выходам первого счетчика, первый, второй, третий и четвертый управляющие входы которого подключены соответственно к третьему, четвертому, пятому и шестому выходам блока управления, а информационные входы подключены к выходам блока синтеза кодов, вторые входы которого объединены, (Л с соответствующими входами элемента ИЛИ и подключены к соответствующим выходам блока цифровых схем сравнения, вторые входы которого подключены к. соответствующим вьЬсодам блока регистров, управляющие входы которо.го подключены к соответствующим седьмым выходам блока управления, со третий вход которого подключен к выходу элемента ИЛИ, четвертый вход является .первой управляющей щиной пре .образователя, пятые входы являются 90 вторыми управляющими шинами преобразователя, восьмой и девятый выходы подключены соответственно к первому .и второму управляющим входам второго счетчика, выходы которрго являются . , выходными шинами преобразователя. 2. Преобразователь по п. 1, о т.личающийся тем, что блок управления выполнен на постоянном запоминающем устройстве, коммутаторе, генератор импульсов, счетчике, регис

Изобретение относится к вычислительной и цифровой .измерительной технике.

Цель изобретения - повьш ение точности аналого-цифро.вого преобразователя. ;

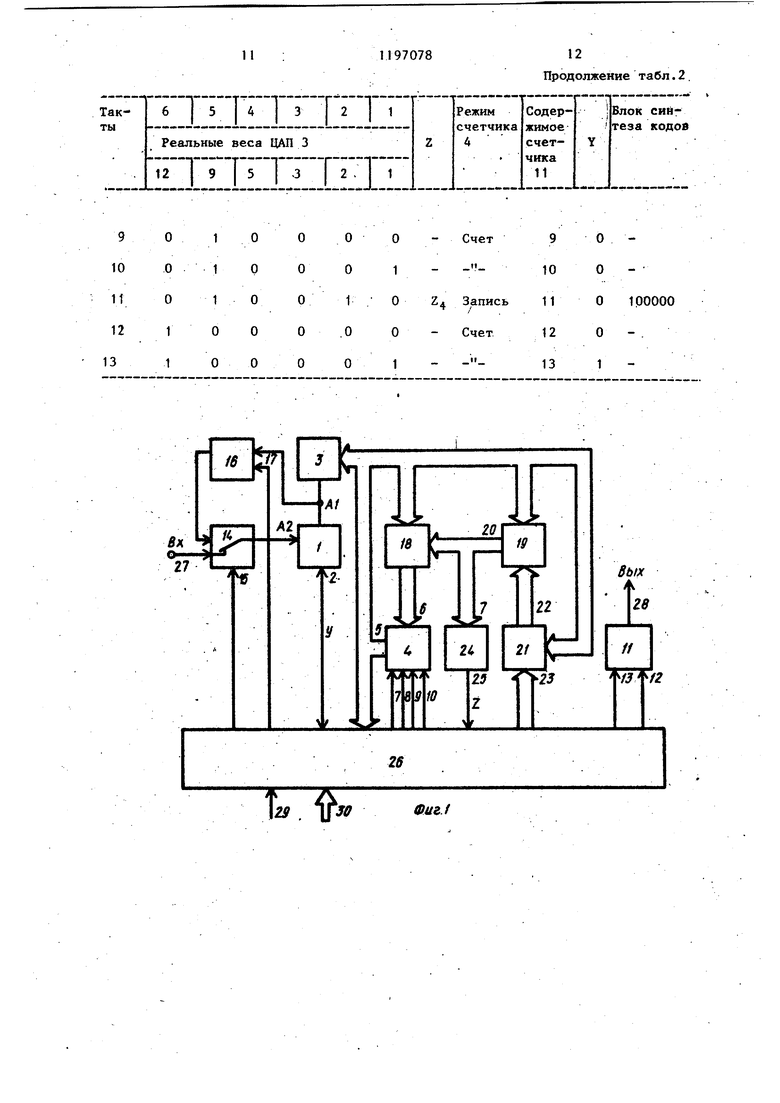

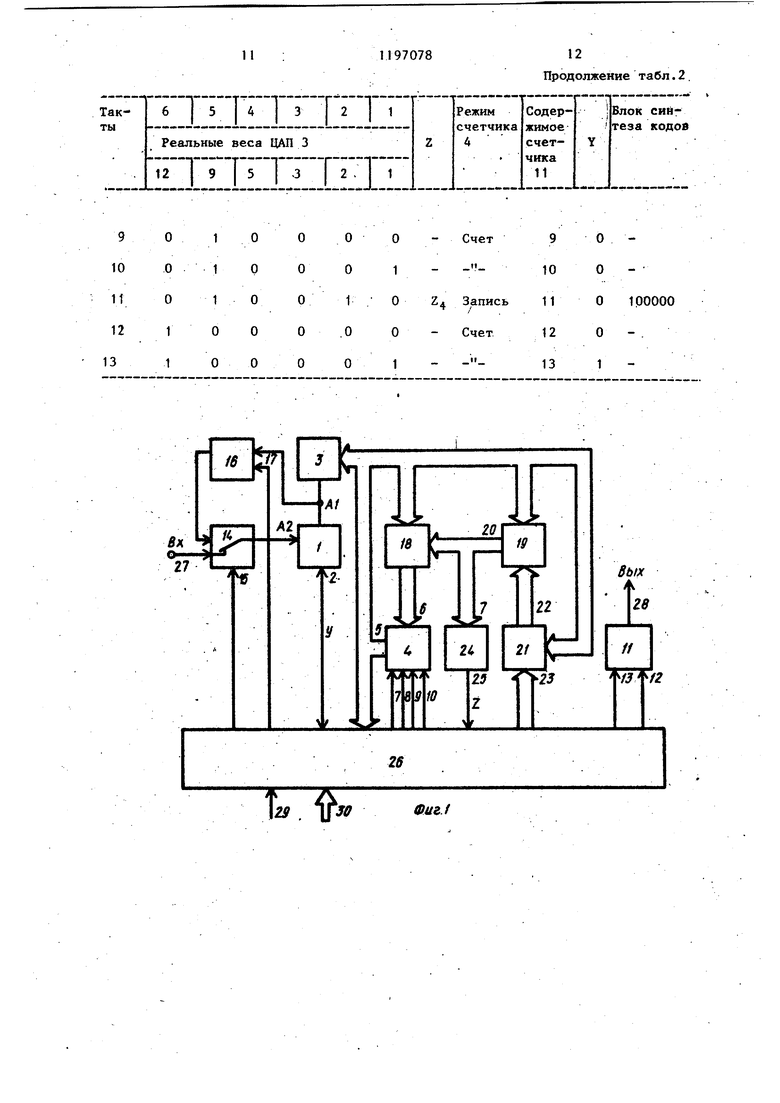

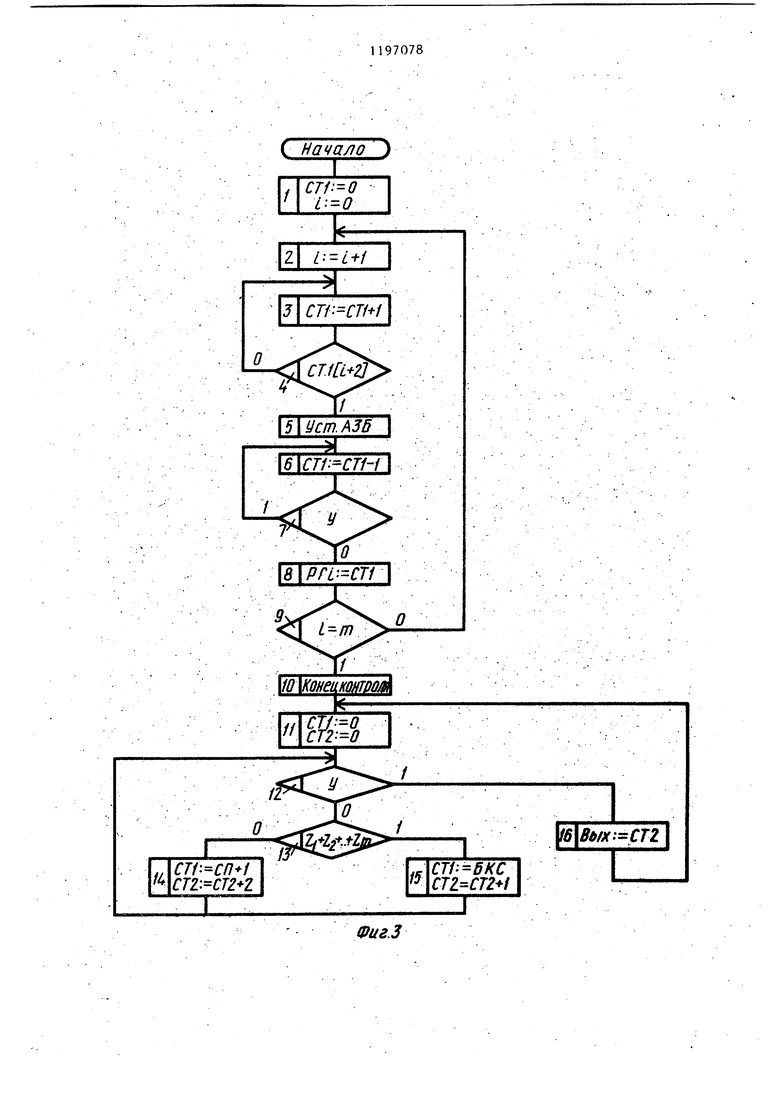

На фиг. 1 приведена.структурная схема устройства; на фиг. 2 - функциональная схема блока синтеза кодов; на фиг. 3 - алгоритм работы устройства; на фиг,.4 - функциональная схема блока управления. . Аналого-цифровой преобразователь содержит, блок 1 сравнения (БС) с выходом 2, цифроаналоговый преобразователь 3 (ЦАП), выполненный на основе избыточного измерительного кода, первый счетчик 4 (СТ1) с выходом 5, информационным входом 6 параллельного занесения данных и управляющими входами первым 7 обнуления, вторым

8 параллельной записи, третьим 9 прямого и четвертью 10 обратного счета импульсов, второй счетчик 11

J

(CT2) с первым и вторым управляющими входами 12 и 13 прямого счета и- обнуления, переключатель 14(П) с управляющим входом 15, аналоговый запоминающий блок 16 (АЗБ) с входом 17управления, блок 18 синтеза кода (БСК), блок 19 цифровых схем сравнения (БЦСС) с вьпсодом 20, блок 21 регистров (БРГ) с выходом 22 и входом 23 управления,-элемелт ИЛИ 24 с выходом 25, блок 26 управления (БУ), входную шину 27 (Вх) и выходные ши.ны 28 (Вых), первую, управляющую шину 29, вторые управляющие шины 30.

Входная шина 27 преобразователя, на которую .подается преобразуемая аналоговая величина А и выход аналогового запоминающего блока 16 под|клЮчены к информационным входам переключателя 14, управляющий вход 15 которого подключен к первому выходу блока 26 .поавления. осушествляющего управление функционированием всего устройства и подключающего в .зависимости от режима работы к входу блока 1 сравнения входнуюшину 27 преобразователя или выход аналогового запоминающего блока 16. Другой вход блока 1 сравнения соединен с выходом цифроаналогового преобразователя 3, соединенного также с информационным входом аналогового запоминающего блока 16, осуществляющего кратковременное хранение выходного напряжения ЦАП 3 в процессе проверки. Управляющий вход 17 аналогового запоминающего блока 16 подключен к второму выходу блока 26 управления. Блок 1 сравнения осуществляет сравнение аналоговых сигналов Aj и А на его входах, причем сигнал Y на его выходе 2, соединенном с- первым входом блока 26 управления, подчиняется следующему соотношению .

Ь

если AJ Aj 10, е

еслИ; А А 2 . Выходы 5 первого счетчика 4 подключены ко входам цифроаналогового преобразователя 3,.первь1м входам блока 18 синтеза кодов, блока 19 цифровых схем сравнения, информационным входам .блока 21 регистров и вторым входам блока 26 управления, третий вход которого соединен с выходом 25 элемента ИЛИ. Управляющие входы 7-10 соответс,твенно обнуления, записи, прямого и обратного счета первого счетчика 4 соединены с третьим, четвертым, пятым и шестым выходами блока

97078«

26 управления,. седьмые выходы которого соединены с управляющими входами 23 блока 21 регистров, служащего для хран.ния m переходных кодовых комбинаций и состоящего из m регистров с параллельным занесением информации, входы записи которых представляют собой управляющие входы 23 блока 21. .Выходы 22 блока 21 регистров соеди- . 10 нены с вторыми входами блока 19 цифровых схем сравнения, осуществляющего сравнение на равенство содержимого группы разрядов первого счетчика 4 с содержимым блока 21 регистров, 15 причем выходной сигнал Z; i-й схемы сравнения равен

tnt.nnn

- f1.

если СТ1 (i) РГ (i)

to, если СТ1 (i) РГ (i),

i 1 i 1, 2, ...m,

,где

содержимое i-ro регистРГ(1) ра блока 21;

CT1(i) содержимое группы из (п - m + i) младщих разрядов первого счетчика 4;

число разрядов первого

n счетчика 4, определяемое разрядностью цифроаналогового преобразователя 3;

количество переходных

m Кодовых комбинаций (для кода Фибоначчи m п - 2) .

Выходы 20 блока 19 цифровых схем сравнения соединены с входами элемента ИЛИ 24. Единичное значение сигнала 2ц +

+ выходе 25

элемента ИЛИ 24 определяет момент срабатывания блока 19..Кроме этого,

выходы 20 блока 19 цифровых схем сравнения соединены с вторыми входами блока 18 синтеза кодов, выходы которого соединены с входами 6 данных первого счетчика 4.

Блок 18 синтеза кодов служи.т для формирования кодовой комбинации, записываемой в первый счетчик 4 после появления на его выходе 5 переходной кодовой комбинации. Комбинация для

записи формируется по содержимому первого счетчика 4 и выходым сигналам блока 19 цифровых схем сравнения, причем i-й разряд ее формируется следующим образом.

г -, { О если 1 n-m

.4

,.,.

i+m-44.1 ч.n)-.2 ...Z,im-n,

511

где. Q-- i-й разряд первого счетчика 4.

. Восьмой и девятый выходы блока 26 управления соединены с первым управляющим входом 12 прямого счета и вторым управляющим входом 13 обнуления второго счетчика 11, выходы которого являюtcя выходными шинами 28 преобразователя.

Блок 18 синтеза кодов (фиг. 2) выполнен на элементах ИЛИ 31 ;, - 31, т-1 инвертора 32 - 32.;|, т-1 элементах И 33 - 33,п-1 и содержит шину 34 постоянного сигнала логического О.

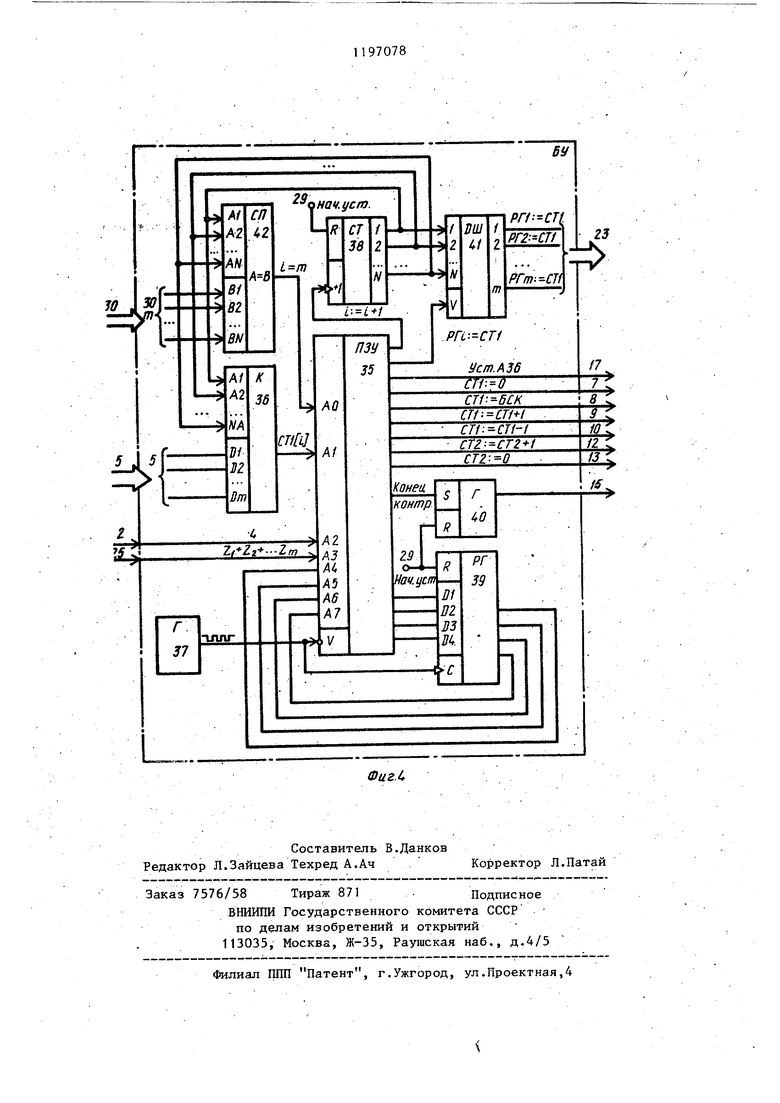

Блок 26 управлейия (фиг. 4) выполнен на постоянном запоминающем устройстве 35, коммутаторе 36, генераторе импульсов 37, счетчике 38, регистре 39, RS-триггере 40, дешифраторе, 41, цифровом блоке сравне- ; НИН 42.

Аналого-цифровой преобразователь работает в двух режимах: режиме поверки и, режиме непосредственного преобразования входной аналоговой величины А), в цифровой двоичный код. В режиме поверки происходит определение m переходных кодовых комбинаций. Переходная кодовая комбинация i-ro разряда ЦАП 3 соответствует аналоговой величине А1 на выходе ЦАП 3, значение которой меньше, реального веса i-ro разряда преобразователя на величину младшего значащего разряда. Определение переходных кодовых комбинаций начинается с разряда, вес которого отличается от двоичного вег са. Так для 1-кода Фибоначчи с младшими весами piaзpядoв .. . 8, 5, 3, 2, 1 определение переходных кодовых комбинаций будет ПРОИЗВОДИТЬСЯ с 3-горазряда.

В режиме поверки по сигналу блока 26 управления первый счетчик 4 начинает работу в режиме прямого счета импульсов до включения первого, из поверяемых разрядов. При включении этого разряда аналоговая величина А1, установившаяся на выходе ЦАП 3, запоминается э аналоговом запоминающем блоке-16 по сигналу блока 26 управления. Выход блока 16 врежиме поверки через переключатель 14 коммутируется на вход блока 1 сравнения, величины А i| и Ag будут равны и Y на выходе 2 блока 1 сравнения соответственно будет равен 1. После этого блок 26 управления переводит

7078 :6

первый счетчик 4 в режим обратного счета импульсов до момента изменения сигнала Y на выходе 2 блока 1 сравнения . Содержимое счетчика 4 при

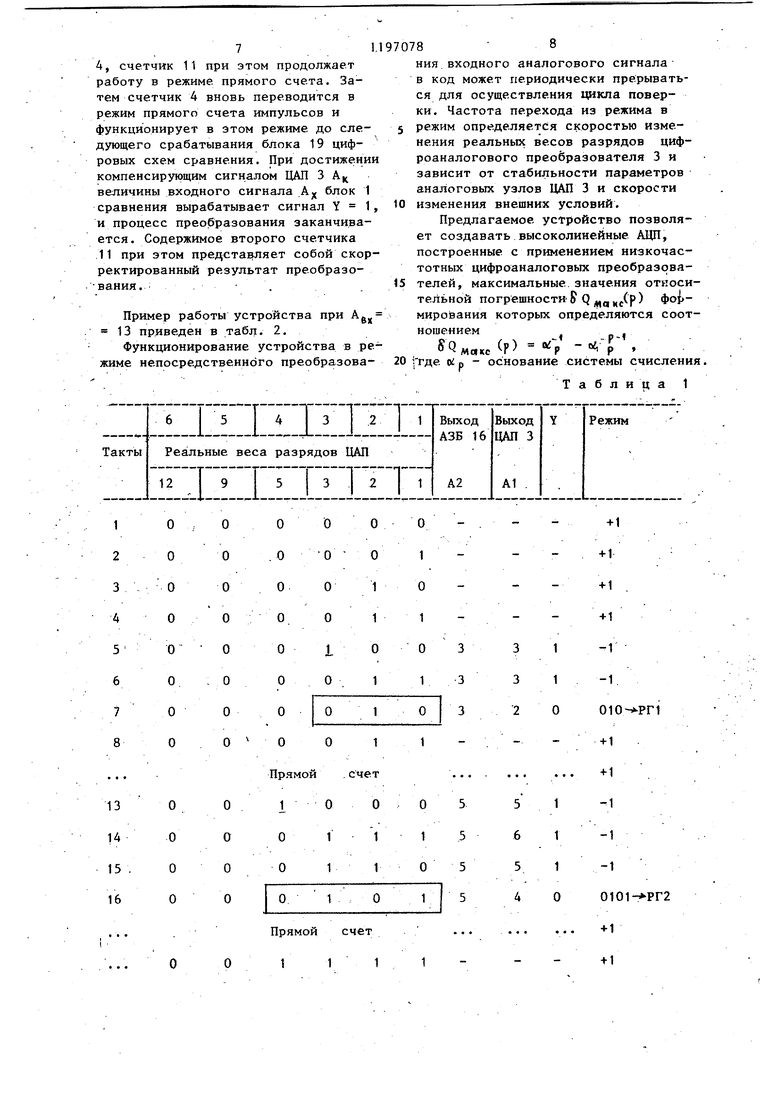

этом будет представлять собой переходную кодовую комбинацию, которая по сигналу блока 26 управления запишется в первый регистр блока 21 регистров. Затем счетчик 4 опять переводится в режим прямого счета импульсов до включения следующего проверяемого разряда. Процедура.определения 2-й и всех последующих переходных кодовых комбинаций будет аналогична определению первой. Пример определения переходных кодовых комбинаций приведен в табл.1.

В режиме непосредственного преобразования входной аналоговой величины Aj( в .код преобразователь работает следующи образом.

С входной шины 27 преобразователя аналоговый сигнал A) коммутируется на первый вход блока 1 сравнения.

5 На- второй вход блока 1 при этом по- , ступает компенсирующий аналоговый сигнал А ц , формирующийся на выходе цифроаналогового преобразователя 3. Разность указанных величин Л А, 0 - AI преобразуется в код методом последовательного счета. При этом счетчики 4 и 11 работают в режиме прямого счета импульсов. В процессе счета содержимое каждого из регистров РГ блока 21 регистров постоянно сравнивается при помощи блока 19 цифровых схем сравнения с соответст- вующей группой из п - m i разрядов счетчика 4. Здесь п - количество разрядов ЦАП, m - число переходных кодовых комбинаций, i - номер регистра, хранящего i-ю переходную комбинацию. Если после поступления очередно- го счетного импульса блок 19 цифровых схем сравнения выработал сигнал Z 1 о раве«стве содержимого i-ro регистра с соответствующей группой разрядов счетчика 4, то блок 26 управления пе.реводит счетчик 4 из |режйма счета в режим записи. Блок 18

0 синтеза кода по содержимому счетчика 4 и выходным сигналам блока 19 цифровых схем сравнения формирует код, аналоговый эквивалент которого точно на величину младшего кванта больше выходной аналоговой величины

ЦАП 3 на данном такте. На следующем такте происходит запись содержимого блока 18 синтеза .кодов в счетчик 7 4, счетчик 11 при этом продолжает работу в режиме прямого счета. Затем счетчик 4 вновь переводится в режим прямого счета импульсов и функционирует в этом режиме до сле дующего срабатывания блока 19 цифровых схем сравнения. При достижен компенсирующим сигналом ЦАП 3 А величины входного сигнала Aj блок сравнения вырабатывает сигнал Y и процесс преобразования заканчива ется. Содержимое второго счетчика 11 при этом представляет собой ско ректированный результат преобразования.. Пример работы устройства при А 13 приведен в табл. 2. Функционирование устройства в р жиме непосредственного преобразова 8 -8 ния входного аналогового сигнала в код может периодически пре;рываться для осуществления цикла поверки. Частота перехода из режима в режим определяется скоростью изменения реальных весов разрядов цифроаналогового преобразователя 3 и зависит от стабильности параметров аналоговых узлов ЦАП 3 и скорости изменения внешних условий. Предлагаемое устройство позволяет создавать высоколинейные АЦП, построенные с применением низкочастотных цифроаналоговых преобразоваталей, максимальные значения относи «чкс Р Фо тельной погрешностиS Q мирования которых определяются соотношением5Q,«,, (р) . где oi р - основание системы счисления, Таблица 1

Таблица 2

2f , Тр

Фиг.(

CTfCn Г7

-л.

8хСТ1 п

Z/W-/

ч

ft

9xCTffnfJ

Я/

8яСТф-т

S3.Z

зы

&

ВхСТ1 п-т

I

вхспш it

С Начало

Г

L-L+i

/

Уст.АЗб

7

тШнемонтроа

1

Фиг.З Г а V. уст. 36 J0, ei

L.

БУ L контр еС Hav.ycin рп-сп ь РГт-.СЛ -сг/ УстЛЗб СП-.БСК CT{- CTf+l стг-0

| Гитис Э.И., Пискулов Ё.А | |||

| Аналого-цифровые преобразователи | |||

| - М | |||

| : Энергоиздат, 1981, с | |||

| Прибор для измерения силы звука | 1920 |

|

SU218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| - | |||

Авторы

Даты

1985-12-07—Публикация

1984-04-04—Подача