со

9д

ЭО

;о

Ф1/г.1

Изобретение относится к автоматике и вычг1слительной технике и может быть использовано для преобразователя двоичного кода в двоично-десятичный.

Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности изменения разрядности входного кода и веса его младшего разряда, а также уменьшение времени преобразования.

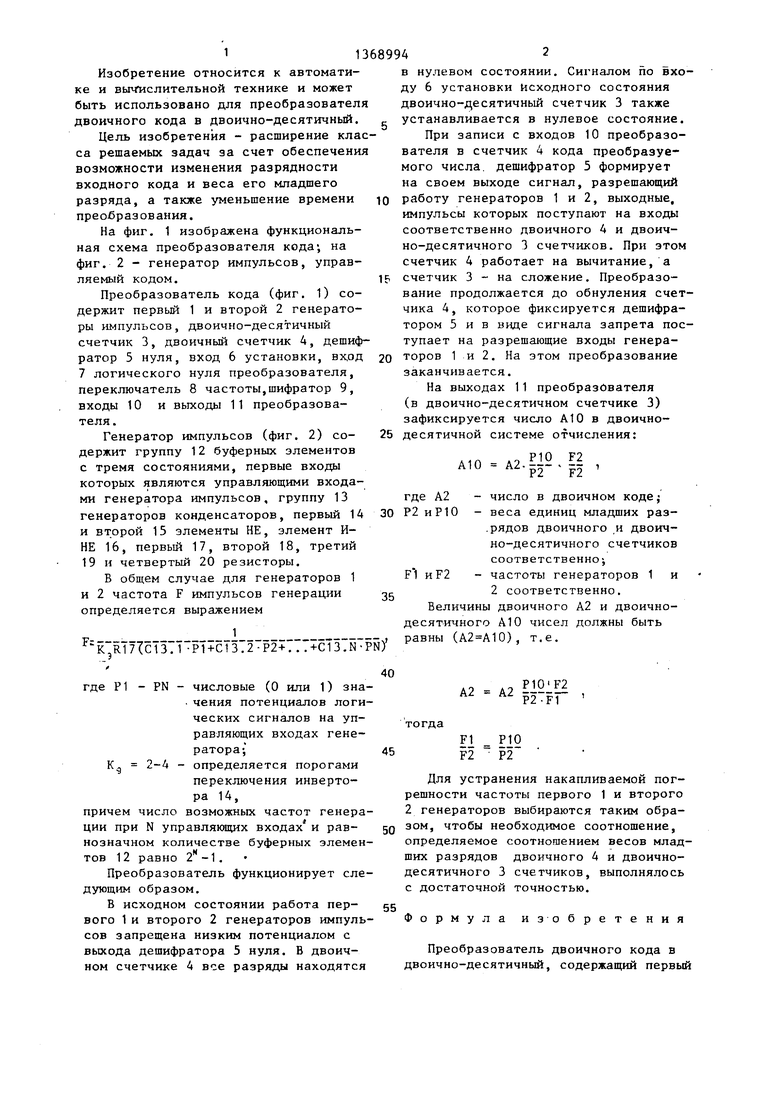

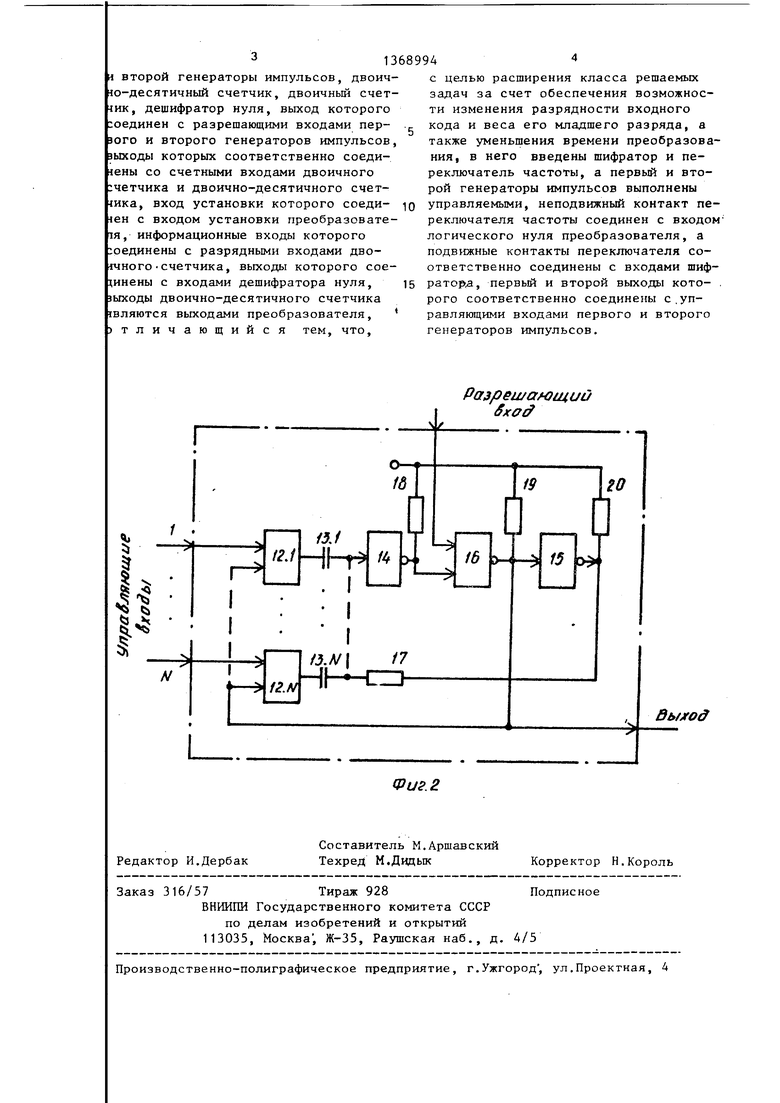

На фиг. 1 изображена функциональная схема преобразователя кода-, на фиг. 2 - генератор импульсов, управляемый кодом.

Преобразователь кода (фиг. 1) содержит первый 1 и второй 2 генераторы импульсов, двоично-десятичный счетчик 3, двоичный счетчик А, дешифратор 5 нуля, вход 6 установки, вход 7 логического нуля преобразователя, переключатель 8 частоты,шифратор 9, входы 10 и выходы 11 преобразователя.

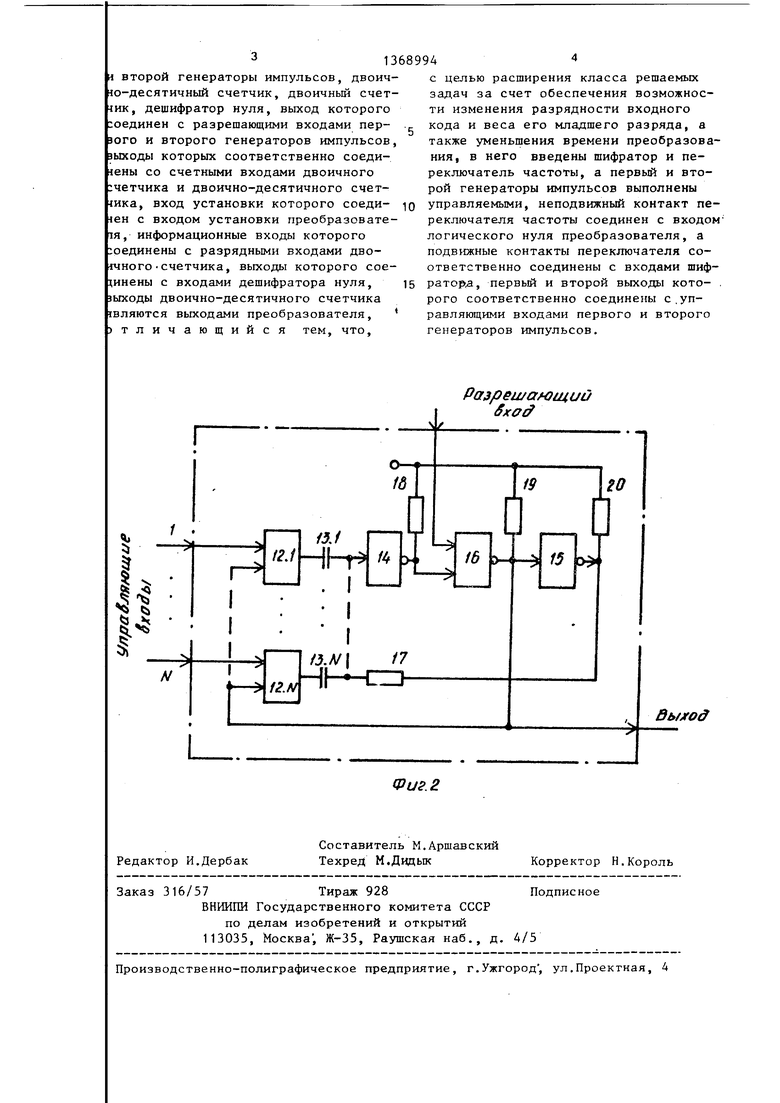

Генератор импульсов (фиг. 2) со- держит группу 12 буферных элементов с тремя состояниями, первые входы которых являются управляющими входами генератора импульсов, группу 13 генераторов конденсаторов, первый 14 и второй 15 элементы НЕ, элемент И- НЕ 16, первый 17, второй 18, третий 19 и четвертый 20 резисторы.

В общем случае для генераторов 1 и 2 частота F импульсов генерации определяется выражением

к кТ7ТсТзТТ рТ+сТзТ2 р2+777+сТзТг5 р

где Р1 - PN - числовые (О или 1) зна- . чения потенциалов логических сигналов на управляющих входах генератора;К 2-4 - определяется порогами переключения инвертора 14,

причем число возможных частот генерации при N управляклцих входах и раз- нозначном количестве буферных элементов 12 равно 2-1.

Преобразователь функционирует следующим образом.

В исходном состоянии работа пер- вого 1 и второго 2 генераторов импульсов запрещена низким потенциалом с выхода дешифратора 5 нуля. В двоичном счетчике 4 все разряды находятся

в нулевом состоянии. Сигналом по входу 6 установки Исходного состояния двоично-десятичный счетчик 3 также устанавливается в нулевое состояние.

При записи с входов 10 преобразователя в счетчик 4 кода преобразуемого числа, дешифратор 5 формирует на своем выходе сигнал, разрешающий работу генераторов 1 и 2, выходные, импульсы которых поступают на входь: соответственно двоичного 4 и двоично-десятичного 3 счетчиков. При этом счетчик 4 работает на вычитание, а счетчик 3 - на сложение. Преобразование продолжается до обнуления счетчика 4, которое фиксируется дешифратором 5 и в виде сигнала запрета поступает на разрешающие входы генераторов 1 и 2. На этом преобразование заканчивается.

На выходах 11 преобразователя (в двоично-десятичном счетчике 3) зафиксируется число А10 в двоично- десятичной системе отчисления:

Р10 F2 .|l2.|f ,

где А2 - число в двоичном коде j Р2 иР10 - веса единиц младших раз- .рядов двоичного ,и двоично-десятичного счетчиков соответственно-, F иГ2 - частоты генераторов 1 и

2 соответственно. Величины двоичного А2 и двоично- десятичного А10 чисел должны быть равны (), т.е.

Р10 F д А 1

P2.F1

тогда

F1 F2

РШ Р2

Для устранения накапливаемой погрешности частоты первого 1 и второго 2 генераторов выбираются таким образом, чтобы необходимое соотношение, определяемое соотношением весов младших разрядов двоичного 4 и двоично- десятичного 3 счетчиков, выполнялось с достаточной точностью.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий первый

i второй генераторы импульсов, двоич- 1о-десятичный счетчик, двоичный счет- 1ИК, дешифратор нуля, вьпсод которого :оединен с разрешающими входами пер- зого и второго генераторов импульсов выходы которых соответственно соединены со счетными входами двоичного счетчика и двоично-десятичного счет- 1ика, вход установки которого соеди- leH с входом установки преобразовате- 1Я, информационные входы которого соединены с разрядными входами двойного -счетчика, выходы которого сое- (инены с входами дешифратора нуля, ыходы двоично-десятичного счетчика 1ВЛЯЮТСЯ выходами преобразователя, тличающийся тем, что.

с целью расширения класса решаемых задач за счет обеспечения возможности изменения разрядности входного кода и веса его младшего разряда, а также уменьшения времени преобразования, в него введены шифратор и переключатель частоты, а первый и второй генераторы импульсов выполнены управляемыми, неподвижный контакт переключателя частоты соединен с входом логического нуля преобразователя, а подвижные контакты переключателя соответственно соединены с входами шиф- раторд, первый и второй выходы которого соответственно соединены с.управляющими входами первого и второго генераторов импульсов.

Разреша щий

Авторы

Даты

1988-01-23—Публикация

1986-05-13—Подача