00 vj

О 05

О5

Изобретение относится к импульсной технике и может быть использовано при анализе формы детерминированных и случайных импульсных сигналов. Цель изобретения - повышение надежности устройства.

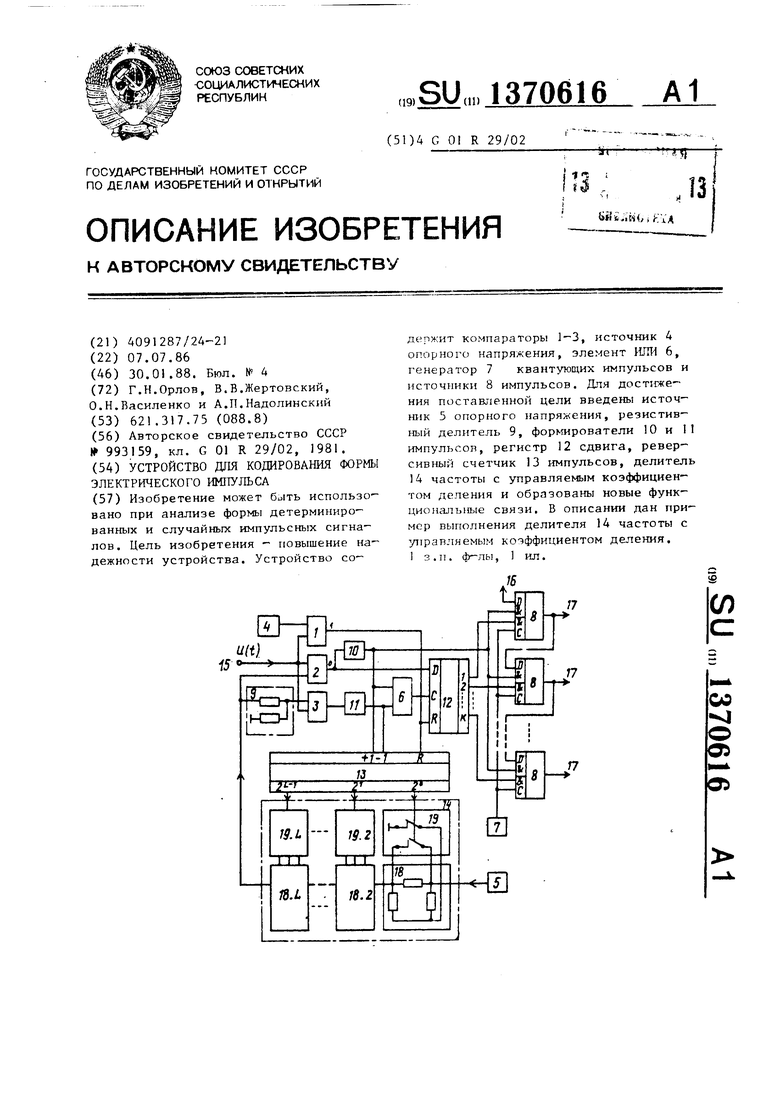

На чертеже приведена структурная схема устройства для кодирования формы электрического импульса.

Устройство дли кодирования формы электрического импульса содержит первый 1, второй 2 и третий 3 компараторы, первый 4 и второй 5 источники опорных напряжений, элемент ИЛИ 6, генератор 7 квантующих импульсов, счетчики 8 импульсов, резистивный делитель 9, первый 10 и второй II формирователи импульсов, регистр 12 сдвига, реверсивный счетчик 13 им- пульсов, делитель 14 напряжения с управляемым коэффициентом деления, входную шину 15, шину 16 логического нуля, выходные шины 17, первые входы компараторов 1 и 3 соединены с вход- ной шиной устройства, выход источника 4 опорного напряжения подключен к второму входу компаратора 1, выходы счетчиков 8 являются выходными шинами 17 устройства, информационный вход первого счетчика 8 подключен к шине логического нуля, информационные входы последующих счетчиков 8 подключены к выходам предыдущего счетчика 8, счетные входы счетчиков 8 соединены с выходом генератора 7, делитель 14 соединен с выходом источника 5, выход делителя 14 соединен с первым входом компаратора 2 и через резис- тивный делитель 9 с вторым входом компаратора 3, управляющие входы делителя 14 соединены с соответствующими выходами реверсивного счетчика 13 импульсов, вход установки в О которого объединен с входом регистра 12 сдвига и подключен к выходу компаратора 1, входы сложение и вычитания реверсивного счетчика 13 импульсов соединены соответственно с первым и вторым входами элемента ИЛИ 6 и выходами формирователей 10 и 11 импульсов, входы которых подключены соответственно к выходам компараторов 2 и 3, синхронизируюпщй вход регистра 12 сдвига соединен с выходом элемента ИЛИ 6, информационный вход - с выходом компаратора 2, второй вход которого подключен к шине 15 устройства, выходы регистра 12 сдвига подклю

Q

5 0 5 0 , Q с

0

5

чены к соответствующим управляющим входам счетчиков 8 импульсов.

Делитель 14 состоит из L последовательно включенных П-образных резис- тивных ячеек 18, вход первой резис- тивной ячейки 18 является входом делителя 14, выход последней резистив- ной ячейки 18 является выходом делителя 14 и коммутаторов 19, замыкающий контакт каждого из которых подключен между входом и выходом соответствующей резистивной ячейки 18, а размыкающий - между общим выводом ячейки 18 и общей шиной устройства, управляющие входы коммутаторов 19 являются управляющими входами делителя.

Устройство работает следующим образом.

Исследуемый сигнал U(t) через шину 15 поступает на первые входы компараторов 1 и 3 и второй вход компаратора 2. Компараторы 1-3 срабатывают при превышении напряжением на их вторых входах напряжения на их первых входах, т.е на их выходах появляется уровень логической единицы. Коэффициент деления делителя 14 зависит от состояния выходов реверсивного счетчика 13. В исходном состоянии коэффициент деления минимален.. Коэффициент деления резистивного делителя 9 равен 1/rf, где cf величина отношения двух соседних уровней (большего к меньшему), по которым ведется кодиро- вание формы входного электрического импульса. Количество счетчиков 8 выбирается из соотношения

... -IM

где а - наименьший относительный уровень, от которого начинается цифровое отображение формы сигнала.

В исходном состоянии (при U(t) 0) регистр 12 сдвига и реверсивный счетчик 13 импульсов принудительно удерживаются в нулевом состоянии напряжением, снимаемым с выхода компаратора 1. Исходное состояние счетчиков 8 импульсов безразлично. На выходе компаратора 2 присутствует напряжение логического нуля, на выходе компаратора 3 - напряжение логической единицы. При появлении сигнала U(t) и достижении им напряжения на источнике 4 опорного напряжения на выходе компаратора 1 появляется уровень логического нуля, который разре-

шает работу регистра 12 сдвига и реверсивного счетчика 13. Затем при дальнейшем росте U(t) и достижении им напряжения на втором входе компаратора 3 на его выходе появляется уровень логического нуля. После этого при достижении входным сигналом напряжения на первом входе компаратора 2 на его выходе появляется уровень логической единицы, что приводит к срабатыванию формирователя 10 ш-тульсов. При этом формирователь 10 вырабатывает короткий импульс. Этот импульс, поступающий на тактирующие входы счетчиков 8, производит запись нуля в первый счетчик 8 и перепись информации из каждого предыдущего счетчика В в последующий. Это обеспечивает подготов-

ку первого счетчика 8 к измерению на первом абсолютном уровне. Кроме этого, импульс с выхода формирователя 10 через элемент ИЛИ 6 поступает на синхронизирующий вход регистра 12 сдвига. При этом по срезу этого импульса в первьш разряд регистра 12 сдвига записывается единица, так как на информационном входе присутствует уровень логической единицы с выхода компаратора 2. Единицей с первого выхода регистра 12 сдвига разрешается работа первого счетчика 8 по счетному входу, так как начинается измерение на первом абсолютном уровне. Одновременно по заднему фронту импульса с формирователя 10 в счетчике 13 записывается единица в младшем разряде, что влечет за собой отключение первой ячейки 18 делителя 14 и увеличение коэффициента деления, а следовательно, и напряжения на его выходе в f раз. При этом компаратор 2 возвращается в нулевое состояние, так как на его выходе появляется уровень логического нуля вследствие того, что напряжение на его первом входе превышает напряжение на шине 15 устройства. Таким образом, после первого срабатывания компаратора 2 начинает работать по счетному входу первьш счетчик 8 и опорное напряжение на первом входе компаратора 2 увеличивается в с/ раз. При дальнейшем росте амплитуды входного сигнала U(t) и достижении им нового опорного на- пряжения на первом входе компаратора 2 на его выходе появляется уровень логической единицы, в результате чего на выходе формирователя 10 импульмьо -

10

3706164

сов вырабатывается снова короткий импульс. Этот импульс осуществляет перенос информации из первого счетчика 8 во второй и т.д. Первый счетчик 8 устанавливается в нулевое состояние, что обеспечивает подготовку этого счетчика к измерению на новом абсолютном уровне. Кроме этого, по срезу второго импульса производится сдвиг информации в регистре 12 сдвига на один такт, т.е. появляется уровень логической единицы и на его втором выходе. Этот уровень разрешает работу по счетному входу второго счетчика 8. Одновременно по срезу второго импульса с выхода формирователя JO в счетчик 13 досчитывается еще одна единица, в результате чего младший разряд реверсивного счетчика 13 устанавливается ,а второй разряд -.

15

20

25

30

35

40

45

50

55

в 1, что влечет за собой включение первой ячейки 18 и выключение второй ячейки 18 делителя. Выключение второй ячейки 18 увеличивает коэффициент деления, а следовательно, и опорное напряжение на первом входе компаратора 2 в с/ раз по сравнению с исходным состоянием, т.е. опорное напряжение на первом входе компаратора 2 увеличивается еще в сГ раз. При этом компаратор 2 снова возвращается в нулевое состояние, т.е. на его выходе появляется уровень логического нуля, так как напряжение на первом входе превышает напряжение на шине 15 устройства. Таким образом, после второго срабатывания компаратора 2 опорное напряжение на его первом входе увеличивается еще в J раз, во второй счетчик 8 переписывается информация о длительности фронта входного сигнала между первым и вторьм абсолютными уровнями, первый счетчик 8 подготавливается к измерению на новом абсолютном уровне.

При дальнейшем росте амплитуды входного сигнала снова срабатывают компаратор 2 и формирователь 10. При этом информация из первого счетчика 8 переписывается во второй, из второго счетчика 8 - в третий, первый счетчик 8 устанавливается в нулевое состояние. После этого в третий счетчик 8 записывается информация о длительности фронта входного сигнала между первым и третьим уровнями, во второй счетчик 8 - информация о длительности фронта между первым и вто-

51

рым уровнями, первый счетчик 8 подготавливается в измерению на новом абсолютном уровне. Кроме этого, регистр 12 по срезу третьего импульса с формирователя 10 разрешает работу по счетному входу третьего счетчика и опорное напряжение на первом входе компаратора 2 увеличивается еще в (/ раз.

Таким образом, после К срабатываний компаратора 2 разрешается работа по счетному входу всех счетчиков 8 и коэффициент деления делителя 14 увеличивается в 1/ раз. При этом в К-и счетчик 8 записывается информация о длительности фронта между первым и К-м абсолютными уровнями, в (К-1)-й счетчик 8 - информация о длительности фронта между первым и (К-1)-м абсолютными уровнями и т.д., первый счетчик 8 устанавливается в нулевое состояние. Это означает, что устройство подготовлено для кодирования формы электрического импульса по К относительным уровням, т.е. на К-м счетчике 8 после К-го срабатывания компаратора 2 измеряется длительнос импульса на наименьшем относительно уровне, а на первом счетчике 8 - на наибольшем относительном уровне. Остальные счетчики 8 измеряют длительность на относительных уровнях, лежащие между наибольшим и наименьшим относительными значениями.

Если амплитуда входного сигнала U(t) продолжает увеличиваться и срабатывает снова компаратор 2, то информация в счетчиках 8 также переписывается из предыдущего счетчика в последующий и первый счетчик 8 устанавливается в нулевое состояние. Информация, накопленная ранее в К-м счетчике 8, в этом случае теряется так как уровень, на котором он производил измерение, находится ниже наименьшего относительного уров

ня, по которому производится кодирование формы электрического импульса. Переписанная по (К+1)-му срабатыва45 де компаратора 3 в t/ раз. Опорное напряжение на втором входе компаратора 3 становится равным . Компаратор 3 возвращается в нулевое состояние, т.е. на его выходе появ.ляет-

компаратора 2 информация из счет-50 ся уровень логического нуля, так как

нию

чика 8. (К-1) в счетчик 8.К в этом случае соответствует снова наименьшему относительному уровню, по которому производится кодирование формы электрического импульса. Таким обра- 55|Амин зом, сохраняется соответствие счетчиков 8 относительным уровням, по которым производится кодирование формы.

напряжение на первом входе превышает напряжение на втором входе. При дальнейшем уменьшении входного сигнала U(t) и достижении им напряжения

снова срабатывают компаратор 3 и формирователь 11. При этом з апре- щается работа по счетному входу второго счетчика 8, а опорное напряжени на втором входе компаратора 3 умень

0

Аналогично работает устройство до достижения входным сигналом U(t) своего максимального значения. Если компаратор 2 срабатываетiраз, опорное напряжение на первом входе компаратора 2 равно А „н V где А - минимальное опорное напряжение на первом входе компаратора 2 при включении всех ячеек 18 делителя 14. Амплитуда входного счетчика в этом случае находится между А мин Опорное напряжение на втором входе компаратора 3 равно , так как коэффициент деления резистивного де- 5 лителя 9 равен 1/о. Таким образом, по срезу входного импульса при достижении им напряжения срабатывает компаратор 3, т.е. на его выходе появляется уровень логической единицы, что приводит к срабатыванию формирователя 11 импульсов, который вырабатывает короткий импульс. Этот им- пульс через элемент ИЛИ 6 поступает на синхронизирующий вход регистра 12. сдвига. Так как на его информационном входе в это время присутствует уровень логического нуля с выхода компаратора 2, то по срезу синхронизирующего импульса на первом выходе регистра 12 сдвига появляется уровень логического .нуля, который запрещает работу по счетному входу первого счетчика. К этому моменту в этом счетчике находится информация о дпи35 тельности входного импульса на наивысшем относительном уровне, по которому производится кодирование формы электрического импульса. Одновременно по срезу импульса с формировй40 теля 11 содержимое реверсивного счет чика 13 уменьшается на единицу, что приводит к уменьшению коэффициента деления делителя 14, а следовательно, и опорного напряжения нр втором вхо45 де компаратора 3 в t/ раз. Опорное напряжение на втором входе компаратора 3 становится равным . Компаратор 3 возвращается в нулевое состояние, т.е. на его выходе появ.ляет-

5

0

ся уровень логического нуля, так как

напряжение на первом входе превышает напряжение на втором входе. При дальнейшем уменьшении входного сигнала U(t) и достижении им напряжения

снова срабатывают компаратор 3 и формирователь 11. При этом з апре- щается работа по счетному входу второго счетчика 8, а опорное напряжение на втором входе компаратора 3 умень

шается еще в У раз. Компаратор 3 снова возвращается в нулевое состояние. Таким образом, по мере окончания входного сигнала U(t) регистр 12 сдвига запрещает работу в счетном режиме счетчиков 8 и коэффициент деления делителя 14 уменьшается в с раз при каждом срабатывании компаратора 3. По окончании входного сигнала информации о его форме находится в . счетчиках 8 и может быть снята с выходных шин 17.

Делитель 14 работает следующим оба

разом. На вход первой П-образной ре- 5 чениях К,-К, равных 1, то

зистивной ячейки 18 поступает напряжение с источника 5 опорного напряжения, а снимается оно с выхода последней ячейки 18. В исходном состоянии размыкающие контакты коммутаторов 19 замкнуты, а замыкающие разомкнуты, следовательно, включены все звенья делителя и коэффициент деления минимален. Коэффициент деления (Кд,) каждой i-и ячейки 18 определяется по формуле

к - JTi-

Выбор минимального и общего коэф

20

К,

1

J WUM п 1--

Исходя ИЗ приведенных со значение опорного напряжени снимаемого с источника 5 оп пряжения, Uon Л „„„ сУ Значение опорного напряж рабатываемого источником 4 напряжения, дилжно быть мен 25 {чтобы обеспечить разблокиро гистра 12 сдвига и реверсив чика 13 до момента, с котор нается кодирование формы вх сигнала.

фициентов деления делителя 14 осуществляется исходя из следующего. С выхода делителя 14 должны сниматься напряжения от А ,„„ до величины, пре- вЕзшающей А , где А д,,, - минимальное абсолютное значение напряжения, от которого начинается цифровое отоб ражение формы электрического импульса; А - максимально возможное . абсолютное значение напряжения исследуемого сигнала. Если общее количество дискретных урювней равно N, то отношение между соседними уровнями постоянно и равно с, т.е.

1cf%.

/«ии

откуда

N,

eg

Ама1(С

Амин

причем значение N округляется до бли жайшего большего целого числа. Поскольку число уровней N формируется по двоичному закону, то N 2 , где L - число П-образных резистивных ячеек 18, а следовательно, число разря50

1. Устройство для кодирования фо мы электрического импульса, содержа щее первый, второй, третий компараторы, первые входы первого и третье го из которых соединены с входной ш ной устройства, первый источник опо ных напряжений, выход которого подключен к второму входу первого компаратора, элемент ИЛИ, генератор квантую1цих импульсов, счетчики импульсов, выходы которых соединены с выходными шинами устройства, инфор-

дов реверсивного счетчика 13. Очевид- мационный вход первого счетчика имчисла. Учитывая, что коэффициент передачи К каждого i-ro звена дели14 равен К

J-

,---t

а общий

коэфйициент деления всего делителя 14 К, равен произведению всех его отдельных звеньев, можно записать

К1.-

J. ,2°- Kj ,7 t... + k; 2--

где К,...К - инверсные значения соответствующих разрядов реверсивного счетчика. Так как минимальный коэффициент деления Код,,.,, будет при знаа

чениях К,-К, равных 1, то

20

30

35

40

К,

1

J WUM п 1--

Исходя ИЗ приведенных соотношений значение опорного напряжения , снимаемого с источника 5 опорного напряжения, Uon Л „„„ .

Значение опорного напряжения, вырабатываемого источником 4 опорного напряжения, дилжно быть меньше , 25 {чтобы обеспечить разблокировку регистра 12 сдвига и реверсивного счетчика 13 до момента, с которого начинается кодирование формы входного сигнала.

Дпя нормального функционирования счетчиков 8 в режиме приема и перезаписи информации по сигналам с выхода формирователя 10 необходимо обеспечить следующую последовательность действий в каждом из счетчиков: запретить работу счетчиков 8 в счетном режиме; запомнить информацию, находящуюся на информационных входах счетчиков 8; произвести перезапись запомненной информации.

Формула изобретения

1. Устройство для кодирования формы электрического импульса, содержащее первый, второй, третий компараторы, первые входы первого и третьего из которых соединены с входной шиной устройства, первый источник опорных напряжений, выход которого подключен к второму входу первого компаратора, элемент ИЛИ, генератор квантую1цих импульсов, счетчики импульсов, выходы которых соединены с выходными шинами устройства, инфор-

мационный вход первого счетчика им

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНЫЙ ЦИФРОВОЙ ЧАСТОТНЫЙ ДИСКРИМИНАТОР | 2000 |

|

RU2166773C1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1988 |

|

SU1837323A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Устройство для исследования электрохимических процессов | 1988 |

|

SU1589187A1 |

| Устройство для оценки амплитуды узкополосного случайного процесса | 1987 |

|

SU1515174A1 |

| Устройство для цифрового отображения формы электрического импульса | 1982 |

|

SU1015314A1 |

| Устройство для измерения искажения длительности импульсов | 1988 |

|

SU1559327A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПЛОТНОСТИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНОГО ПРОЦЕССА | 2000 |

|

RU2174706C1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

Изобретение может быть использовано при анализе формы детерминированных и случайных импульсных сигналов. Цель изобретения - повышение надежности устройства. Устройство содержит компараторы 1-3, источник 4 опорного напряжения, элемент ИЛИ 6, генератор 7 квантующих импульсов и источники 8 импульсов. Для достюте- ния поставленной цели введень источник 5 опорного напряжения, резистив- ный делитель 9, формирователи 10 и II импульсов, регистр 12 сдвига, реверсивный счетчик 13 импульсов, делитель 14 частоты с управляемым коэффициентом деления и образованы новые функциональные связи. В описании дан пример выполнения делителя 14 частоты с управляемым коэффициентом деления. 1 3.п. ф-лы, 1 ил. б €

1е N

но, что L 7 7°--. Значение L округIg 2 ляется до ближайшего большего целого .

пульсов подключен к шине логического нуля, информационные входы каждого последующего счетчика импульсов сое-

динены с выходом предыдущего счетчика импульсов, счетные входы всех счетчиков импульсов соединены с выходом генератора квантующих импульсов, отличающееся тем, что, с целью повышения надежности устройства, в него дополнительно введены ре- зистивный делитель, два формирователя импульсов, регистр сдвига, ревер- сивный счетчик импульсов, второй источник опорного напряжения и делитель напряжения с управляемым коэффициентом деления, вход которого соединен с выходом второго источника опорного напряжения, вьгход соединен с первым входом второго компаратора и через резистивный делитель с вторым входом третьего компаратора, а управляющие входы соединены с выхода- ми реверсивного счетчика импульсов, вход установки в О которого подключен к выходу первого компаратора и входу установки в О регистра сдвига, входы сложения и вычитания реверсивного счетчика импульсов соединены соответственно с первым и вторым входами элемента ИЛИ и выходами первого и второго формирователей импульсов, входы которых подключены со- ответственно к выходам второго и третьего компараторов, синхронизирующий вход регистра сдвига соединен с выходом элемента ИЛИ, информационный вход соединен с выходом второго компаратора, второй вход которого подключен к входной шине устройства, а выходы регистра сдвига соединены с соответствующими управляющими входами счетчиков импульсов, синхронизм рующие входы которых подключены к выходу первого формирователя импульсов

| Устройство для цифрового отображения формы электрического импульса | 1981 |

|

SU993159A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-01-30—Публикация

1986-07-07—Подача