Изобретение относится к автоматике и коммутационной технике.

Цель изобретения - повышение быстродействия устройства неординарной разовой коммутации за счет опроса входных шин со скоростью распространения сигнала по цепи логических элементов приоритетного блока.

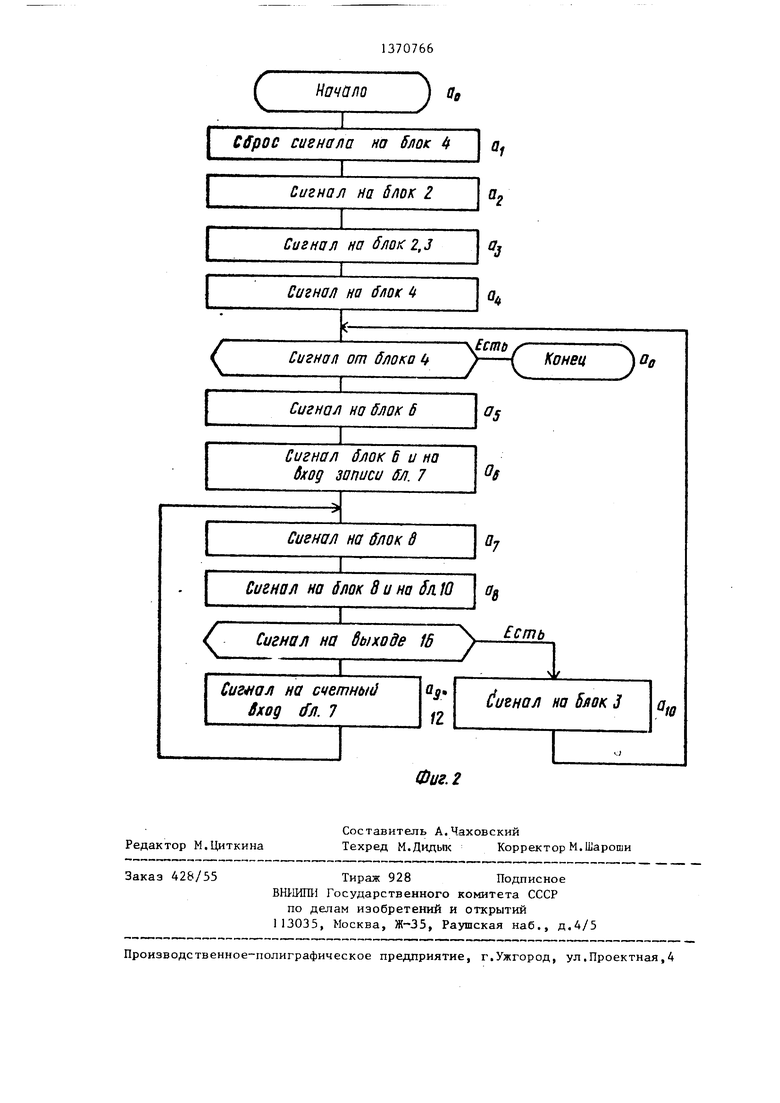

На фиг.1 приведена функциональная схема устройства неординарной разовой коммутации; на фиг. 2 - алгоритм работы блока управления.

Устройство неординарной разовой

дом 25 начальной установки устройства.

Первые входы элементов И 13.1-13. и входы управления элементов ЗАПРЕТ 14.J-14.N соединены с соответствующим информационным входом приоритетного блока 4, второй вход элемента И J3.J и информационный вход элемента ЗАПРЕТ 14. первого разряда соединены с входом разрешения приоритетного блока 4, выход J5 разрешения которого соединен с выходом элемента ЗАПРЕТ 14.N, выходы элементов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1987 |

|

SU1522272A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Конвейерное буферное запоминающее устройство для систем обработки изображений | 1989 |

|

SU1751769A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП ЕДИНИЧНЫХ БИТ И МАКСИМАЛЬНЫХ ГРУПП В БЛОКАХ БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2023 |

|

RU2815502C1 |

| Многоканальный аналого-цифровой преобразователь | 1985 |

|

SU1317658A1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

Изобретение относится к комму тационным устройствам и может быть использовано в автоматике и коммутационной технике. Цель изобретения - повьппение быстродействия устройства неординарной разовой коммутации - достигается путем опроса входных шин со скоростью распространения сигнала по цепи логических элементов приоритетного блока. Для этого в устройство дополнительно введены блок 2 элементов И, блок 3 триггеров, приоритетный блок 4 и шифратор 5. Крюме того, устройство содержит блок 6 памяти адресов, счетчик 7, блок 8 памяти, дешифратор 9, регистр 10, входные шины 11, блок 12 управления, элементы И 13.1-13.N и ЗАЛРЕТ 14.1-14.N, выход 15 разрешения блока 4 и вы- ход 16 блока 8 памяти. Позициями 17-24 отмечены выходы блока управления, а позицией 25 - вход начальной установки устройства. 1 з.п.ф-лы, 2 ил. i (Л со ч О) Од 11 Фи1. 1

20

коммутации содержит входные шины 1.1- -jr ЗАПРЕТ 14.J-J4.N- соединены с вто- 1.N, блок 2 элементов И, блок 3 триггеров, приоритетный блок 4, шифратор 5, блок 6 памяти адресов, счетчик 7, блок 8 памяти, дешифратор 9, регистр 10, выходные шины 11, блок 12 управления, элементы И 13.1-13.N и ЗАПРЕТ l4.i-14.N приоритетного блока 4, выход J5 разрешения приоритетного блока 4 и выход J6 блока 8 памяти. Выходы блока 6 памяти адресов соединены с входами счетчика 7, выходы которого соединены с адресными

рым входом элементов И J3.2-13.N и информационным входом элементов ЗАПРЕТ 14.2-14.Н соответственно.

Устройство неординарной разовой коммутации работает следующим образом.

Перед началом работы в блок 8 памяти вводятся кадры адресов выходных шин 11. В случае неординарной ком- 25 мутации кадр содержит несколько адресов выходных шин 11, при ординарной коммутации в кадре имеется только один адрес выходной шины 11. Каждый кадр адресов выходных шин 11 соответ- шифратора 9, выходы которого соедине- 30 ствует требуемой информационной шины с входами регистра JO, выхо i ко- не Li. Это соответствие определяется

входами блока 8 памяти, группа выходов которого соединена с входами деторого подключены к выходным шинам 11 управляющие входы блоков 8 памяти и 6 памяти адресов, счетный вход и вход записи счетчика 7 и вход записи регистра 10 соединены соответственно с выходами J7-2J (с первого по пятый) блока 12 управления, первый вход которого соединен с выходом 16 блока 8 памяти, информационные входы блока 2 элементов И подключены к входным шинам 1.J-1.N, а выходы - к S-входам триггеров 3.1-3.N блока 3 триггеров, выходы которых соединены с входами приоритетного блока, выходы которого соединены с соответствующими R-входами триггеров 3.1-3.N блока 3 триггеров и с входами шифратора 5, выходы которого соединены с адресными входами блока 6 памяти адресов, вторые входы элементов И 2.1-2.N блока 2 элeмeнtoв И, С-входы триггеров блока 3 триггеров, входы разрешения приоритетного блока соединены соответственно с выходами 22-24 (с шестого по восьмой) блока управления, выход разрешения приоритетного блока 4 соединен с вторым входом блока управления третий вход которого соединен с вхо5

0

занесением в i-ю ячейку блока 6 памяти начального адреса ячейки блока 8 памяти, начиная с которой в блоке 8 памяти записан этот кадр адресов выходных шин 11. Граница кадра адресов выходных шин 11 задается специальным кодированием. В каждом формате адресов выходной шины 11 имеется дополнительный разряд, который кодируется нулем или единицей и выдается по выходу 16 блока 8 памяти в блок 12 управления. Наличие нуля в этом разряде означает, что формат ад5 реса выходной шины 11 входит в кадр, а наличие единицы определяет границу кадра адресов. Кроме того, в блок 6 памяти в соответствующие ячейки памяти производится запись адре-

Q сов - указателей кадров адресов, размещенных в блоке 8 памяти.

При поступлении сигнала на вход/2 5 установки блок 12 управления устанавливается в начальное состояние.

t По сигналам от блока 12 управления, подаваемым на блок 2 элементов И и С-входы блока 3 триггеров, информация с информационных шин 1-1.1.N записывается в блок 3 триггеров. С вы-

ходов блока 3 триггеров информация подается на входы приоритетного блока 4, выделяющего на своих выходах (при поступлении управляющего сигнала от блока 12 управления) лишь один, самый верхний по схеме на фиг.1, сигнал из поступившей информации. Для этого каждый разряд приоритетного бло ка 4 содержит два элемента 13 и 14. Q На выходе элемента И 13 формируется единица, если на один его вход поступает единичный сигнал разрешения с выхода элемента 14 более старшего . разряда блока 4, а на другой вход - J5 единичный сигнал, записанный в блок 3 триггеров. На выходе элемента 14 формируется сигнал разрешения, поступающий в соседний младший разряд, если на один его вход поступает единич-2о С-входы триггеров блока 3. На R-BXOный сигнал разрешения с выхода элемента 14 соседнего старшего разряда блока 4, а на другой вход - нулевой сигнал, записанный в блок 3. Сигнал разрешения на самый старший разряд блока 4 выдает блок 12 управления. Сигнал разрешения из самого младщего разряда блока 4 поступает на второй вход блока 12 управления. Равенство этого сигнала единице означает, что все триггеры блока 3 сброшены в ноль Таким образом, при наличии единичных бит в блоке 3 и сигнала разрешения от блока J2 на выходах блока 4 образуется унитарный код, причем единица возникает в разряде, соответствующем самому старшему разряду в блоке 3. Этот унитарный код поступает на вход шифратора 5, на выходе которого формируется двоичный код номера разряда входного кода, содержащего единицу. Двоичный код с выхода шифратора 5 поступает на адресный вход, блока 6 памяти, из соответствующей

ячейки которого по сигналу, поступаю- старшего разряда блока 4, на выходах

щему на управляющий вход блока 6 памяти от блока 12 управления, выбирается начальный адрес кадра адресов выходных шин JJ в блоке памяти. Этот начальный адрес записывается по сигналу -от блока 12.в счетчик 7, с выходов которого от подается на адресные входы блока 8 памяти. По сигналам, подаваемым от блока J2 на счетный вход счетчика 7, управляющий вход блока 8 памяти и вход записи регистра 10, организуется считывание из блока 8 памяти кадра адресов выходных щий П. Считываемые из блока 8

SO

55

которого снова образуется унитарный код с единицей в разряде, соответствующем самому старшему из оставшихся единичных битов в блоке 3 триггеров. Этот код переводится шифратором 5 в двоичный нормальный код,ко- торый с выходов шифратора 5 поступает на адресный вход блока 6 памяти, из соответствующей ячейки которого выбирается начальный адрес, записываемый в счетчик 7, и начинается счи- тьшаиие из блока 8 памяти нового кадра адресов выходных щин 11. Одновременно триггер блока 3, содержащий обпамяти адреса дешифруются дешифратором 9 и устанавливают соответствующие триггеры регистра 10 в единичное состояние, выполняя таким образом передачу сигналов с информационной шины 1 на выходную шину 1I. Одновременно блок 12 управления анализирует выход 16 блока 8 памяти. Если он равен нулю, то значение счетчика 8 увеличивается на единицу, и осуществляется считывание очередного адреса выходной шины 1 кадра информационной шины 1. Если выделенный разряд равен , то это указывает блоку 12 управления на границу кадра.

После загрузки начального адреса кадра адресов из блока 6 памяти в счетчик 7 блок 12 выдает сигнал на

5

0

5

0

ды триггеров блока 3 поступает унитарный код с выходов приоритетного блока 4. Триггер блока 3, на R-вход которого поступает единица с соответствующего выхода блока 4 (т.е.триггер, содержащий единичный бит, которому соответствует считьгааемый из блока В памяти кадр адресов) при поступлении на его С-вход сигнала от блока 12 сбрасывается в ноль. Остальные триггеры блока 3 сохраняют свое состояние, т.к. на их R- и Б-входы поступают нули (на входы элементов И блока 2 с выхода 12 сразу же после записи битового среза в блок 3 триггера выдается нулевой уровень, сохраняющийся в течение всего цикла работы устройства).,

По окончании считывания кадра, адресов из блока 8 памяти, о чем свидетельствует единичный сигнал на его выходе 16, блок 12 управления в.новь выдает сигнал разрешения на вход

старшего разряда блока 4, на выходах

которого снова образуется унитарный код с единицей в разряде, соответствующем самому старшему из оставшихся единичных битов в блоке 3 триггеров. Этот код переводится шифратором 5 в двоичный нормальный код,ко- торый с выходов шифратора 5 поступает на адресный вход блока 6 памяти, из соответствующей ячейки которого выбирается начальный адрес, записываемый в счетчик 7, и начинается счи- тьшаиие из блока 8 памяти нового кадра адресов выходных щин 11. Одновременно триггер блока 3, содержащий обрабатываемый единичный бит, сбрасывается в ноль.

Далее процедура повторяется для следующего единичного бита в блоке 3 и т.д., пока все триггеры блока 3 не будут сброшены в ноль. При этом на выходе 15 блока 4 возникает единица (при посыпке блоком J2 очередного и сигнала разрешения на старший разряд блока 4). При наличии единицы на выходе 15 блок 12 управления не производит считьшания из блока 6 памяти, а загружает новую информацию с входных шин 1 в блок 3 триггеров через блок 2 элементов И, после чего цикл работы устройства повторяется.

Таким образом, опрос входных шин производится со скоростью распространения сигнала в цепочке логических элементов приоритетного блока 4, что приводит к общему повьщ1ению быстродействия .

Формула изобретения

целью повышения быстродействия, в него введены блок элементов И, блок триггеров, приоритетный блок и шифратор, причем первые входы элементов И из блока элементов И подключены к соответствующим входным шинам, а выходы элементов И из блока элементов И к S-входам соответствующих триггеров

из блока триггеров, выходы которых соединены с соответствующими информационными входами приоритетного блока, выходы которого соединены с Б-входами соответствующих триггеров .

блока триггеров и с входами шифратора, выходы которого соединены с адрес ными входами блока памяти адресов, вторые входы элементов И из блока элементов И, С-входы триггеров из

блока триггеров, входы разрешения приоритетного блока соединены соответственно с выходами с шестого по восьмой блока управления, а выход разрешения приоритетного блока соединен с вторым входом блока управл,ения, третий вход которого является входом начальной установки устройства.

мента ЗАПРЕТ последующего разряда.

С

Начало

(

Сигнал от блока

Сигнал но блок 6

Сигнал блок § и на дход записи ил. 7

Сигнал на блок д

Сигнал на длок 8 и но 6л. Ю

1

/ Сигнал на выходе 16

1 :

Сигнал на счетный 8ход fл. 7

).

Есть

cfmo хч

)Ч

05

Об

8

Есть

п 12

{ иенал на блок 3

10

| Распределитель импульсов | 1976 |

|

SU660255A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство неординарной разовой коммутации | 1981 |

|

SU1001469A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-30—Публикация

1986-06-10—Подача