00

о д

Од

113

Изобретение относится к импульсной технике и предназначено для сопряжения низковольтных схем ТТЛ типа с высоковольтньми схемами или исполнительными устройствами.

Цель изобретения - увеличение надежности путем сокращения аппаратурных затрат и уменьшение времени задержки выключения высоковольтного логического элемента.

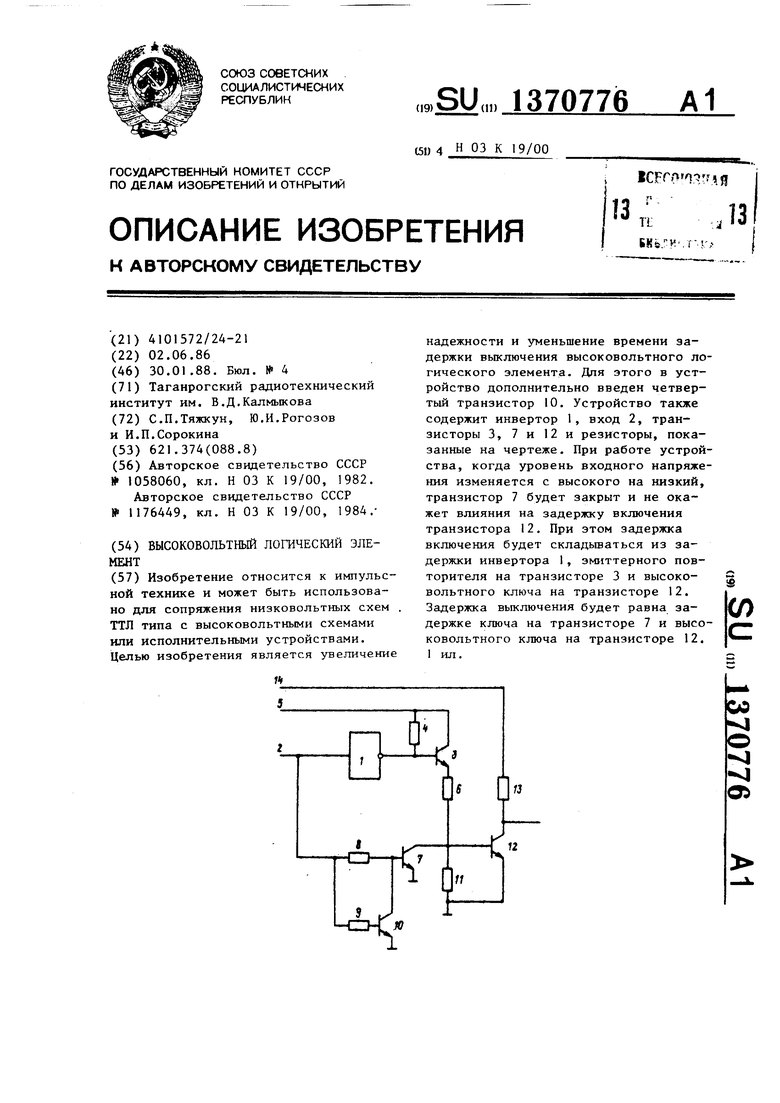

Принципиальная схема высоковольтного логического элемента приведена на чертеже.

Высоковольтный логический элемент содержит инвертор 1, вход которого соединен с входом 2 элемента, выход с базой первого транзистора 3 и через третий резистор 4 - с шиной питания 5 и коллектором транзистора 3, эмиттер которого через пятый резисто 6 соединен с коллектором второго транзистора 7, эмиттер которого соединен с общей шиной, а база через первый резистор 9 с входом 2, который через четвертый резистор 9 соединен с базой четвертого транзистора 10, эмиттер которого соединен с общей шиной, а коллектор - с базой транзистора 7, коллектор которого через второй резистор 1 1 соединен с обш- шиной и подключен к базе третьего транзистора 12, эмиттер которого соединен с общей шиной, коллектор - с выходом и через элемент 13 нагрузки подключен к шине 14 высоковольтного питания.

Высоковольтный логический элемент работает следующим образом.

При напряжении низкого уровня на входе 2 транзисторы 7, 10 закрыты и закрыт выходной транзистор инвертора 1, вьтолненного по схеме с открытым коллектором. Транзистор 3 открыт, и

током через резистор 6 открыт транзис-45 увеличения надежности и уменьшения

тор 12, через нагрузку 13 протекает ток.

При изменении уровня входного напряжения с низкого на высокий переключение элемента происходит следующим образом.

50

времени задержки выключения, введен четвертый транзистор, эмиттер котор го соединен с общей шиной, база чер четвертый резистор соединена с вход элемента и вторым выводом первого резистора, а коллектор соединен с б ЗОЙ второго транзистора, коллектор которого через пятый резистор соеди нен с эмиттером первого транзистора коллектор которого соединен с шиной питания, а база подключена к втором выводу третьего резистора.

Сначала открьшается транзистор 7, что обусловлено соотношением между резисторами 8 и 9 (резистор 9 больше 55 резистора 8 в пределе на коэффициент

li

транзистора 10). Открытый тран

5

0

5

зистор 7 обеспечивает быстрое рассасывание избыточных зарядов в базе транзистора 12 и запирание последнего, причем независимо от того, успел закрыться транзистор 3 низким уровнем на выходе инвертора 1 или нет. Через время задержки, достаточное для переключения инвертора 1 и запирания транзистора 3, открывается транзистор 10 и закрывается транзистор 7. Низкий уровень напряжения на базе транзистора 12 относительно его эмиттера поддерживается резистором 1I,

При изменении уровня входного напряжения с высокого на низкий транзистор 7 уже закрыт и не влияет на задержку включения транзистора 12.

Таким образом, задержка включения элемента складывается из задержки инвертора, эмиттерного повторителя на транзисторе 3 и высоковольтного ключа на транзисторе 12. Задержка выключения равна задержке ключа на транзисторе 7 и высоковольтного ключа на транзисторе 12.

Формула изобретения

Высоковольтный логический элемент, содержащий пять резисторов, инвертор, вход которого соединен с входом элемента, а выход - с базой первого транзистора, эмиттер второго транзис- тора соединен с общей шиной, база - с первым выводом первого резистора, коллектор через второй резистор соединен с общей шиной и подключен к базе третьего транзистора, эмиттер которого соединен с общей шиной, а коллектор подключен к выходу элемента, первый вывод третьего резистора соединен с шиной питания, отличающийся тем, что, с целью

времени задержки выключения, введен четвертый транзистор, эмиттер которого соединен с общей шиной, база через четвертый резистор соединена с входом элемента и вторым выводом первого резистора, а коллектор соединен с ба- ЗОЙ второго транзистора, коллектор которого через пятый резистор соединен с эмиттером первого транзистора, коллектор которого соединен с шиной питания, а база подключена к второму выводу третьего резистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| ТТЛ-элемент | 1985 |

|

SU1274150A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2002 |

|

RU2233022C1 |

| Усилитель-инвертор | 1987 |

|

SU1429310A1 |

| Транзисторный ключ | 1985 |

|

SU1336223A2 |

| Высоковольтный логический элемент | 1989 |

|

SU1690189A1 |

| ПЕРЕДАТЧИК МУЛЬТИПЛЕКСНОЙ МАНЧЕСТЕРСКОЙ ЛИНИИ СВЯЗИ | 2002 |

|

RU2229769C2 |

Изобретение относится к импульсной технике и может быть использовано для сопряжения низковольтных схем . ТТЛ типа с высоковольтными схемами или исполнительными устройствами. Целью изобретения является увеличение надежности и уменьшение времени задержки выключения высоковольтного логического элемента. Для этого в устройство дополнительно введен четвертый транзистор 10. Устройство также содержит инвертор 1, вход 2, транзисторы 3, 7 и 12 и резисторы, показанные на чертеже. При работе устройства, когда уровень входного напряжения изменяется с высокого на низкий, транзистор 7 будет закрыт и не окажет влияния на задержку включения транзистора 12. При этом задержка включения будет складьшаться из задержки инвертора 1, эмиттерного повторителя на транзисторе 3 и высоковольтного ключа на транзисторе 12. Задержка выключения будет равна задержке ключа на транзисторе 7 и высоковольтного ключа на транзисторе 12. 1 ил. i сл

| Высоковольтное логическое устройство | 1982 |

|

SU1058060A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Высоковольтный логический элемент | 1984 |

|

SU1176449A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-01-30—Публикация

1986-06-02—Подача