Изобретение относится к импульсной технике и может быть использовано в цифровых логических схемах, когда требуется повышенное быстродействие и помехоустойчивость.

Целью изобретения является увеличение быстродействия и повышение помехозащищенности ТТЛ-элемента.

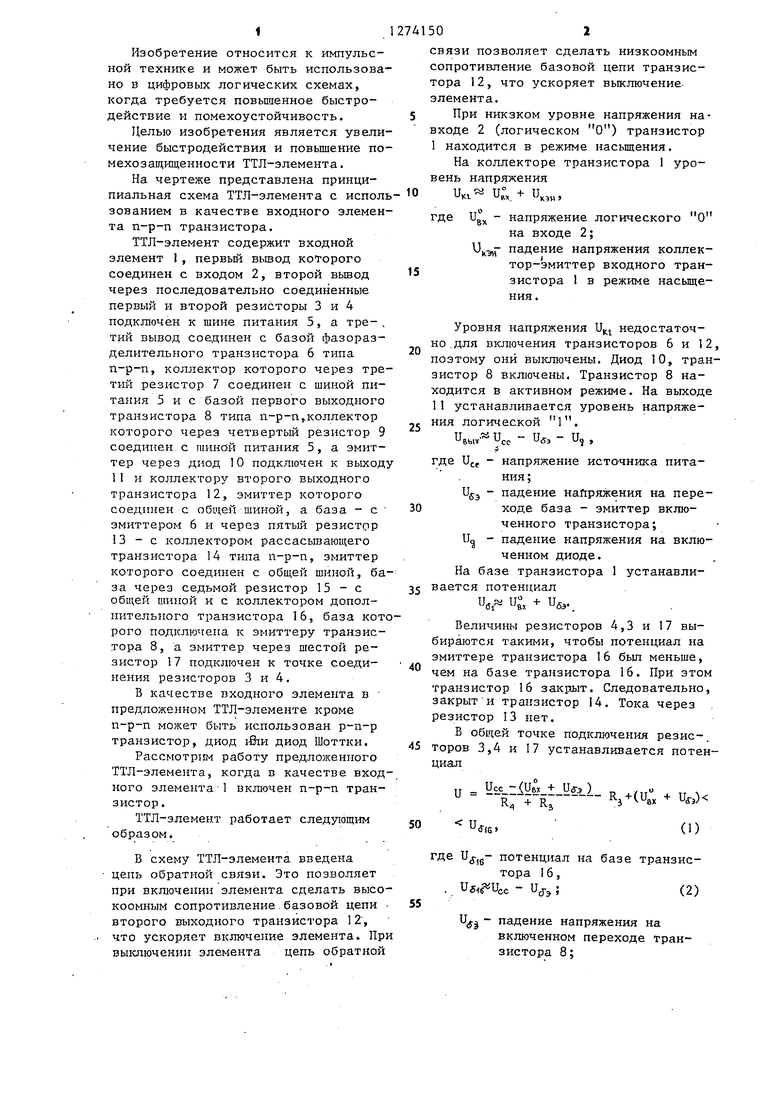

На чертеже представлена принципиальная схема ТТЛ-элемента с использованием в качестве входного элемента п-р-п транзистора.

ТТЛ-элемент содержит входной элемент 1, первый вьшод которого соединен с входом 2, второй вьшод через последовательно соединенные первый и второй резисторы 3 и 4 подключен к шине питания 5, а тре-, тий вывод соединен с базой фазоразделительного транзистора 6 типа п-р-п, коллектор которого через третий резистор 7 соединен с шиной питания 5 и с базой первого выходного транзистора 8 типа п-р-п,коллектор которого через четвертый резистор 9 соединен,с шиной питания 5, а эмиттер через диод 10 подключен к выходу 1I и коллектору второго выходного транзистора 12, эмиттер которого соединен с общей шиной, а база - с эмиттером 6 и через пятый резистор 13 - с коллектором рассасывающего транзистора 14 типа п-р-п, эмиттер которого соединен с общей шиной, база через седьмой резистор 15 - с общей шиной и с коллектором дополнительного транзистора 16, база которого подключена к эмиттеру транзистора 8, а эмиттер через шестой резистор 17 подключен к точке соединения резисторов 3 и 4.

В качестве ззходного элемента в предложенном ТТЛ-элементе кроме п-р-п может быть использован р-п-р транзистор, диод i-0iH диод Шоттки.

Рассмотрим работу предложенного ТТЛ-элемента, когда в качестве входного элемента1 включен п-р-п транзистор.

ТТЛ-элемент работает следующим образом.

В схему ТТЛ-элемента введена цепь обратной связи. Это позволяет при включении элемента сделать высокоомным сопротивление базовой цепи второго выходного транзистора 12, что ускоряет включение элемента. Пр выключении элемента цепь обратной

связи позволяет сделать низкоомным сопротивление базовой цепи транзистора 12, что ускоряет выключение элемента.

При никзком уровне напряжения навходе 2 (логическом О) транзистор 1 находится в режиме насьщения.

На коллекторе транзистора 1 уровень напряжения

UK.« и; + и,,„,

где Up - напряжение логического О

на входе 2;

падение напряжения коллектор-эмиттер входного транзистора 1 в режиме насьщения.

Уровня напряжения недостаточно, для включения транзисторов 6 и 12 поэтому они выключены. Диод 10, транзистор 8 включены. Транзистор 8 находится в активном режиме. На выходе 11 устанавливается уровень напряжения логической 1.

UBb,v« у,, - - и, ,

i

где - напряжение источника питания ;

- падение наЛряжения на переходе база - эмиттер включенного транзистора; Ug - падение напряжения на включенном диоде.

На базе транзистора 1 устанавливается потенциал

S,« + бз-.

Величины резисторов 4,3 и 17 выбираются такими, чтобы потенциал на эмиттере транзистора 16 бьш меньше, чем на базе транзистора 16. При этом транзистор 16 закрыт. Следовательно, закрыт и транзистор 14. Тока через резистор 13 нет.

В общей точке подключения резисторов 3,4 и 17 устанавливается потенциал

IT - Ucc + Ua-э ) ., f..o ,, , и - -R- --g-RjHU,, + U,)

и

(1)

cTlG

где потенциал на базе транзистора 16, ., - U ;(2)

- падение напряжения на

включенном переходе транзистора 8; Ur(. - напряжение на шине питания 5; Rj,R - сопротивление резисторов 3 и 4. При логическом О на входе 2 т потребления равен входному току ло гического О на входе, поскольку при отсутствии нагрузки токами резисторов 7 и 9 можно пренебречь. При Напряжении логического О на входе должно выполняться услови (1), которое с учетом (2) имеет ви Ucc-U.8.. При повышении входного напряжения растет потенциал на коллектор транзистора 1. Транзистор остается в режиме насыщения до тех пор, пока потенциал на его коллекторе н достигнет величины Транзистор 16 закрыт, пока поте циал на его базе не будет ниже вел чины (1) на величину напряжения от крывания перехода база - эмиттер. Поэтому при повьшении входного напряжения до величины 2 УЛ - кэн не ответвляется ток в резистор 13, так как транзистор 14 закрыт и отсу ствует пологий участок передаточной характеристики в диапазоне входных напряжений Urfa- ик, и.эн-. и транзисторы 6 и 12 начинают переключаться одновременно. Схема обладает улучшенной передаточной характеристикой, следовательно, улучшается помехозащищенность в состоянии логического О на входе. При дальнейшем росте входного напряжения и,,- 2 %, - и„„ Происходит переключение ТТЛ-элемента, транзистор 1 переходит в инверс ньй активный режим работы. Транзи торы 6 и I2 переходят в режим насыщения. На выходе 11 устанавливается низкий уровень напряжения логического nэи Где иадн - напряжение коллектор эмиттер транзистора 12 в режиме насыщения. 504 Потенциал на базе напряжения 16 понизится до величины ,« + и,, тт где Uj,o - падение напряжения на включенном диоде 10. Понижение потенциала приводит к включению транзистора 16, который переходит в активньй режим. Включение транзистора 16 приводит к тому, что включается транзистор 14 , появляется ток резистора 13. Причем, чем меньше величина резистора I3, тем меньше базовый ток транзистора 12 и тем меньгае степень насыщения транзистора 12. При включении транзистора 16 и переходе транзистора 1 в инверсный режим в общей точке резисторов 3, 4 и 17 устанавливается некоторьй потенциал и. При этом ток резистора 4 равен сумме токов резисторов 3 и 17: IR IRH CU,,-U)G, (U-(2U, + Uj)) G,+ + (U-(U,,,+ и, + , )) G,, , де G. ,G ,G - проводимость резисторов 3,4 и 17; (2Ujj. + U ) - потенциал базы транзистора 1 при напряжении логическо 1 на входе 2; ( + и,н) потенциал на эмиттере транзистора I6 при напряжении логической 1 на входе 2; Vf - падение напряжения на переходе база коллектор транзистора 1 в инверсном режиме . Из (5) определяем величину U: и §5LUcf J:Gii 2y4 iygj,)iG(y,) G.+ G.G,, Для того, чтобы обеспечивалось ключение транзистора 16, необходимо, тобы в этом режиме между потенциаами и и Uj выполнялось соотношение. и - Uj и, .е. разницы должно хватить для вклюения эмиттерИого перехода транистора 16, с учетом (4) и (6) словие (7), запишем в вице

51274150

(,.)l G Liyb«i-Ui t-yiLl ., G,7 В состоянии логического О на выходе логической 1 на входе резистора 4 равен Т - Uct Ucc Ujj +2 ол R R а N где и определяется из (6), причем не должен превышать ток типо го ТТЛ-элемента, чтобы не увелич лась потребляемая мощность. Ток резистора 3 равен т и - (2 иаэ- ) т RJ-D i где - базовый ток транзистора Ток резистора 7 равен Т - У ее ; (). . М т R где Кб коллекторный ток транз ра 6; |)- питенциал на коллекто э . .транзистора 6 в режим насьп;ения; R-J - сопротивление резисто Поскольку ток резистора 3 явл ся базовым током транзистора 6, его должно хватить для насыщения транзистора 7. Должно вьлолняться условие П.,1.5, где р - коэффициент усиления тра зистора 6; S- минимальная степень насы ния транзистора 6. С учетом (10) и (11) условие выглядит: .)p , U celly i li При логической 1 на входе т резистора 17 определяется из выр ния 1 ...1. , I - ток эмиттера транзисто S(6 . f(8)

и.,„+

Js Транзистор 16 находится в активом режиме. Коллекторньй ток транистора 16 равен Т - - 6 -Мб р+1 Р де р - коэффициент усиления р-п-р транзистора 17. В настоящее время технология изготовления интегральных схем позволяет олучить р-п-р транзисторы с достаточно высокими коэффициентами усиления базового тока в активном режиме. оэтому при включении транзистора 16 основная часть тока эмиттера транзистора 16 идет в коллектор транзистора 16. Транзистор 14 включен и должен находиться в режиме насыщения, его базовьш ток равен 8и М6 Ri5 1 -Ufe -R15 R,s -ток резистора 15; -сопротивление резистора 15, ток (16) должен быть достаточным для насьпчения транзистора 14, При этом коллекторный ток равен I К14 R, гДе и. -падение напряжения перехода база. - эмиттер транзистора 12 в режиме насыщения; -падение напряжения коллектор - эмиттер транзистора 14, Между базовым и коллекторным током транзистора 14 должно выполняться соотнощение WP IK-S Базовый ток выходного транзистора 12 в состоянии логического О на выходе I1 равен I 1 -I RT аъ K-i1 ДеГ„,,1 ,1 определяются из (10), КЛл-..J (11),(17). Базовый ток транзистора 12 должен . обеспечивать насыщение выходного трантранзистора 12, Транзистор 8 при состоянии логического О на выходе 1 закрыт. Таким образом, в состоянии логической 1 на входе 2 на выходе I1 устанавливается состояние логического О, включается обратная связь, что приводит к уменьшению ба зового тока насыщения выходного тра зистора 18, так как величина резист ра 13 выбирается меньше величины ан логичного резистора базовой цепи вы ходного транзистора в типовом элементе. Рассмотрим работу ТТЛ-элемента в импульсном режиме. Когда в состоянии логического О на вход 2 приходит положительны фронт входного импульса, то на вход 2 устанавливается уровень логической 1. Транзисторы 6 и 12 еще не успевают включиться и обратная связ резистор 17 - транзистор 16 не вклю чены. Весь ток резистора 4 идет на включение транзистора 6. Пока не включен транзистор 12, в общей точке подключения резисторов 3,4 и 17 потенциал устанавливается равным и .,) 42 и, +

и .)().,,(,)

G. Vs,r к.„ и« Через низкоомную цепь резистор 13 - транзистор 14 происходит быстрый разряд базового тока насыщенного выходного транзистора, тем быстрее, чем меньше величина резистора 13. Величину резистора 13 можно уменьшать неограничено при условии, чтобы сохранилось насыщение выходного транзистора 12 и транзистора 1 При этом уменьшение величины резистора 13 не влияет на задержку включения схемы. Когда выключается транзистор 12, то потенциал на базе транзистора i 6 повьшается и обратная связь выключа . Таким образом, предложенная схем ТТЛ-элемента позволяет улучшить помехоустойсивость схемы и значител но увеличить быстродействие схемы при сохранении прежней мощности потребления типового ТТЛ-элемента. Возможны различные варианты орга низации обратной связи. Например, база транзистора 16 может подклю(21)

и,

б1б 50 и,, S Величины R должны выбираться с учетом выполнения (20). Пока не работает обратная связь, ток в резистор 13 не ответвляется и весь ток транзистора 6 идет на включение выходного транзистора 12. Таким образом, обеспечивается быстрое включение схемы. После включения выходного транзистора включается обратная связь, начинает идти ток в цепь резистор 13 - транзистор 14. Когда в состоянии логической 1 на входе 2 приходит отрицательный фронт входного импульса, то на входе 2 устанавливается уровень напряжения логического О. Транзисторы 6 и 12 некоторое время сохраняют состояние насыщения. Обратная связь остается включенной и для базового тока транзистора 12 сохраняется низкоомная цепь разряда базового тока. Аналогично (6) в общей точке подключения резисторов 3, 4 и 17 устанавливается (пока остается в насьпцении транзистор 12) чаться к коллектору выходного транзистора 12, в коллекторную и базовую цепь транзистора 16 могут включаться дополнительные элементы: резистор, диод и др. Для регулировки величины задержки включения можно вводить дополнительно резистор между коллектором транзистора 14 и общей шиной. Формула изобретения ТТЛ-элемент, содержащий рассасывающий транзистор типа п-р-п,входной элемент, вьшоды которого соединены соответственно с входом элемента через первый и второй последовательно соединенные резисторы с шиной питания и с базой фазоразделительного транзистора типа п-р-п,коллектор которого соединен с базой первого выходного транзистора типа п-р-п, и через третий резистор - с шиной питания, коллектор первого выходного транзистора через четвертый

9 127415010

резистор подкттючен к шине питания,действия и повышения помехозащищена эмиттер через диод соединен с вы-ности, введены седьмой резистор и

ходом и коллектором второго выход-дополнительный транзистор типа р-п-р,

ного транзистора типа п-р-п, эмиттерэмиттер которого соединен с вторым

которого соединен с общей шиной, а5 выводом шестого резистора, база - с

база подключена к эмиттеру фазоразде- эмиттером первого выходного транзислительного транзистора и первому вы тора, а коллектор - с базой рассаводу пятого резистора, первый выводсывающего транзистора и через седьмой

шестого резистора соединен с точкойрезистор - с общей шиной, которая

соединения вьтодов первого и Btoporo10 соединена с эмиттером рассасьтагощего

резисторов, отличающийсятранзистора, коллектор которого соетем, что, с целью увеличения быстро-динен с вторым вьшодомпятого резистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент транзисторно-транзисторной ложки (его варианты) | 1985 |

|

SU1274149A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТТЛ-элемент | 1985 |

|

SU1277382A1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ТТЛ-вентиль | 1985 |

|

SU1324105A1 |

| ТТЛ-инвертор | 1984 |

|

SU1269252A1 |

| Преобразователь уровня сигналов | 1981 |

|

SU1011025A1 |

| Транзисторный инвертор | 1990 |

|

SU1757069A1 |

| ТТЛ-вентиль | 1985 |

|

SU1324104A1 |

| Интегральный логический элемент и-не | 1978 |

|

SU790333A1 |

Авторы

Даты

1986-11-30—Публикация

1985-07-04—Подача