(21)4130446/24-24

(22)30.06,86

(46) 07.02.88. Бюло № 5

(72) О.Н.Галченков, В.Ф.Чудина

и Н.МоЛауберг

(53) 681.325 (088.8)

(56) Авторское свидетельство СССР

№ 1171783, кл. G 06 F 7/52, 1984.

Процессор ЕС 2060, ТО 2. М, 1977, с.16-17.

О

t.

7,

7 ff

11

(54) УСТРОЙСТВО ДЛЯ ПРИБЛИЖЕННОГО ВЫЧИСЛЕНИЯ ОБРАТНОЙ ВЕЛИЧИНЫ НЕНОРМАЛИЗОВАННЫХ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ

(57) Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машии, а также устройств цифровой обработки сигналов, работающих в системе счисления с плавающей запятой. Цель изобретения состоит в сокращении аппаратурных затрат. Поставленная цель достигается тем, что устройство для приближенного вычисления обратной величины ненормализованных чисел с плавающей запятой, содержащее сумматор 1, блок 2 схем сравнения с нулем, блок 4 элементов НЕ, содержит блок 3 памяти с соответствукяцими связями. 1 Ил., 2 табл.

i

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ УМНОЖИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2137179C1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ ДЕЛИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2130639C1 |

| Устройство для суммирования нормализованных чисел с плавающей запятой | 1987 |

|

SU1418704A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

5

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифметических устройств вычислительных машин, а также в устройствах цифрово обработки сигналов, работающих в системе счисления с плавающей запятой.

Цель изобретения - сокращение ап- паратурных затрат.

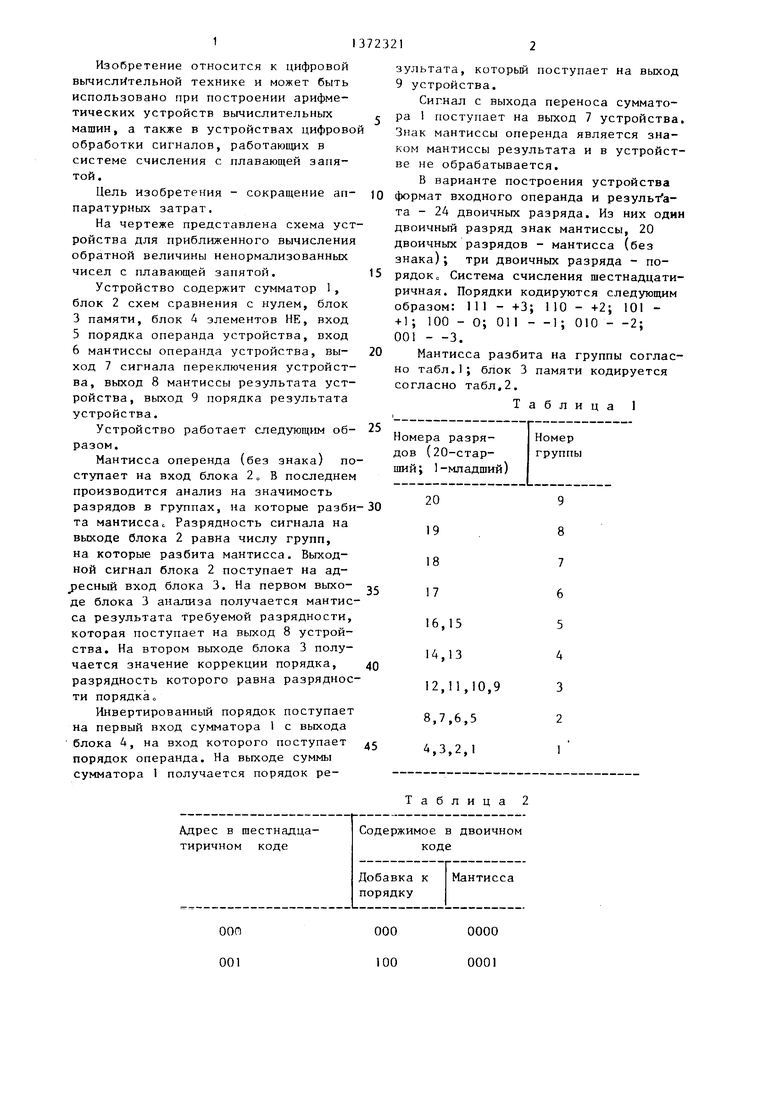

На чертеже представлена схема устройства для приближенного вычисления обратной величины ненормализованных чисел с плавающей запятой.

Устройство содержит сумматор 1 , блок 2 схем сравнения с нулем, блок 3 памяти, блок 4 элементов НЕ, вход

5порядка операнда устройства, вход

6мантиссы операнда устройства, вы- ход 7 сигнала переключения устройства, выход 8 мантиссы результата устройства, выход 9 порядка результата устройства.

Устройство работает следующим об- разом.

Мантисса оперенда (без знака) поступает на вход блока 2 В последнем производится анализ на значимость разрядов в группах, на которые разби та мантисса о Разрядность сигнала на выходе блока 2 равна числу групп, на которые разбита мантисса. Выходной сигнал блока 2 поступает на адресный вход блока 3, На первом выхо- де блока 3 анализа получается мантисса результата требуемой разрядности, которая поступает на выход 8 устройства. На втором выходе блока 3 получается значение коррекции порядка, разрядность которого равна разрядности порядка.

Инвертированный порядок поступает на первый вход сумматора 1 с выхода блока 4, на вход которого поступает порядок операнда. На выходе суммы сумматора 1 получается порядок реООП001

зультата, который поступает на выход 9 устройства.

Сигнал с выхода переноса сумматора 1 поступает на выход 7 устройства Знак мантиссы оперенда является знаком мантиссы результата и в устройстве не обрабатывается,

В варианте построения устройства формат входного операнда и результата - 24 двоичных разряда. Из них один двоичный разряд знак мантиссы, 20 двоичных разрядов - мантисса (без знака); три двоичных разряда - порядок „ Система счисления шестнадцатиричная. Порядки кодируются следующим образом: 111 - +3; 110 - -1-2; 101 - +1; 100 - О; 011 - -1; 010 - -2; 001 - -3,

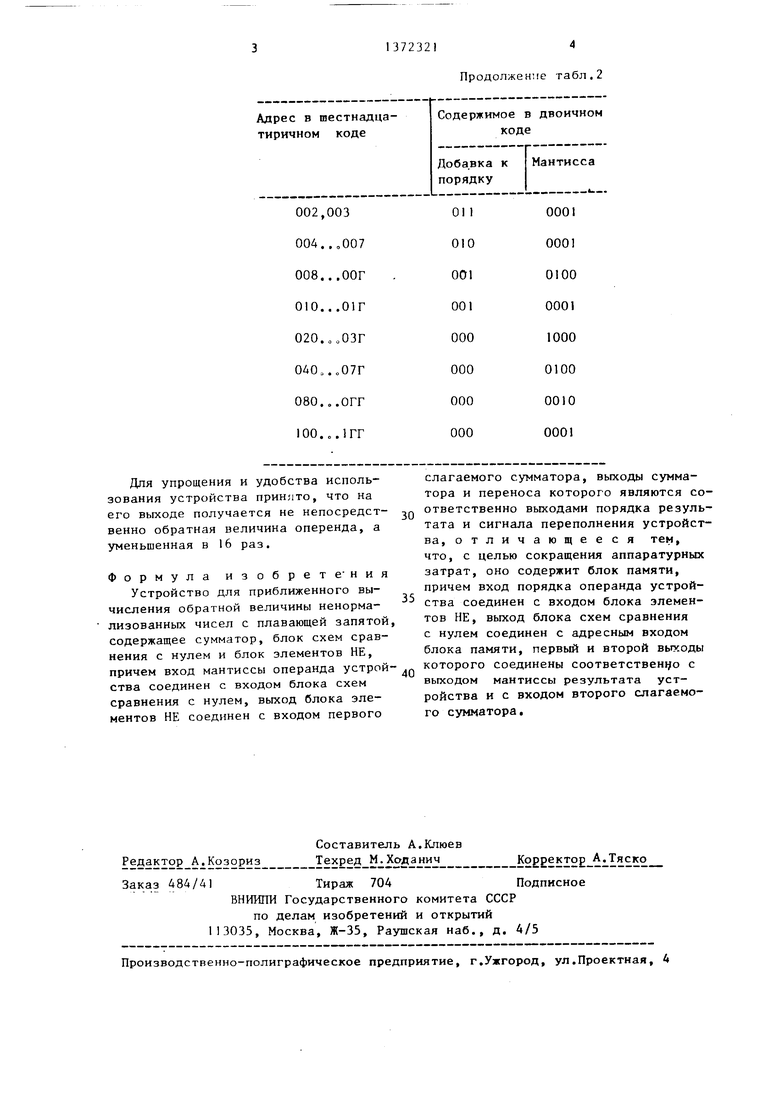

Мантисса разбита на группы согласно табл,1; блок 3 памяти кодируется согласно табл.2,

Таблица 1

Таблиц

000 100

0000 0001

Для упрощения и удобства использования устройства принято, что на его выходе получается не непосредственно обратная величина операнда, а уменьшенная в 16 раз.

Формула изобрете ния

Устройство для приближенного вычисления обратной величины ненормализованных чисел с плавающей запятой содержащее сумматор, блок схем срав- неиия с нулем и блок элементов НЕ, причем вход мантиссы операнда устрой- ства соединен с входом блока схем сравнения с нулем, выход блока элементов НЕ соединен с входом первого

13723214

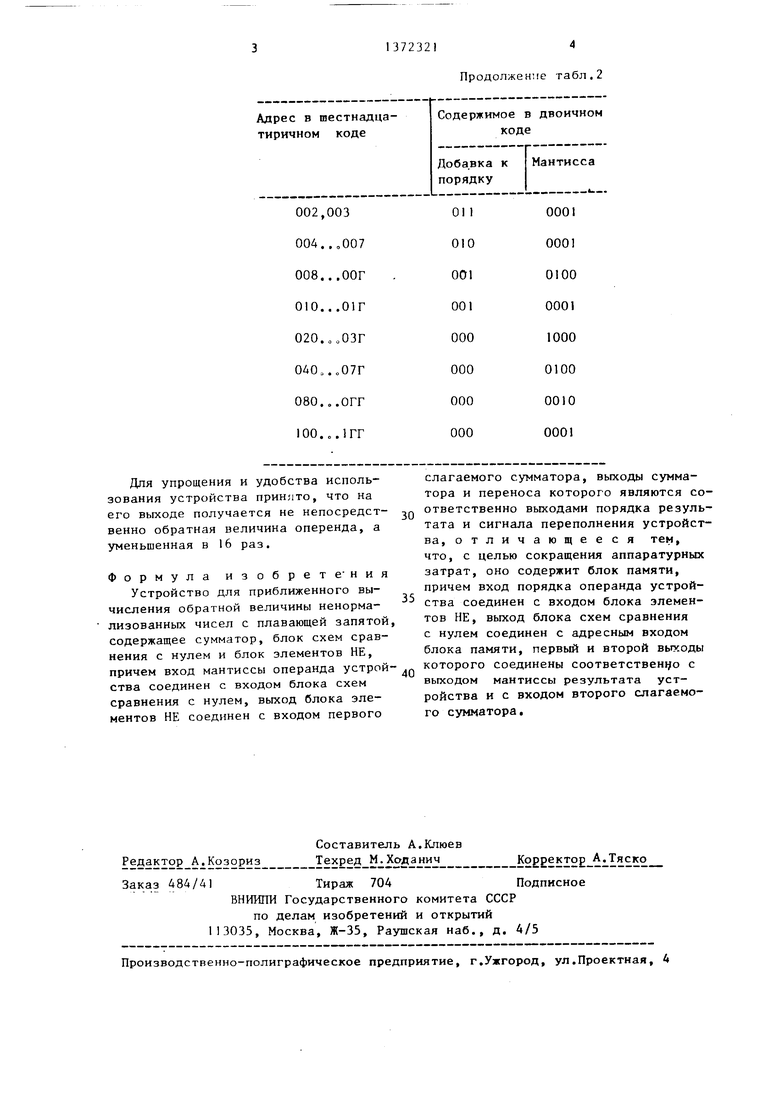

Продолжение табл.2

слагаемого сумматора, выходы сумматора и переноса которого являются соответственно выходами порядка результата и сигнала переполнения устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит блок памяти, причем вход порядка операнда устройства соединен с входом блока элементов НЕ, выход блока схем сравнения с нулем соединен с адресным входом блока памяти, первый и второй вьгкоды которого соединены cooтвeтcтвeнI o с выходом мантиссы результата устройства и с входом второго слагаемого сумматора.

Авторы

Даты

1988-02-07—Публикация

1986-06-30—Подача