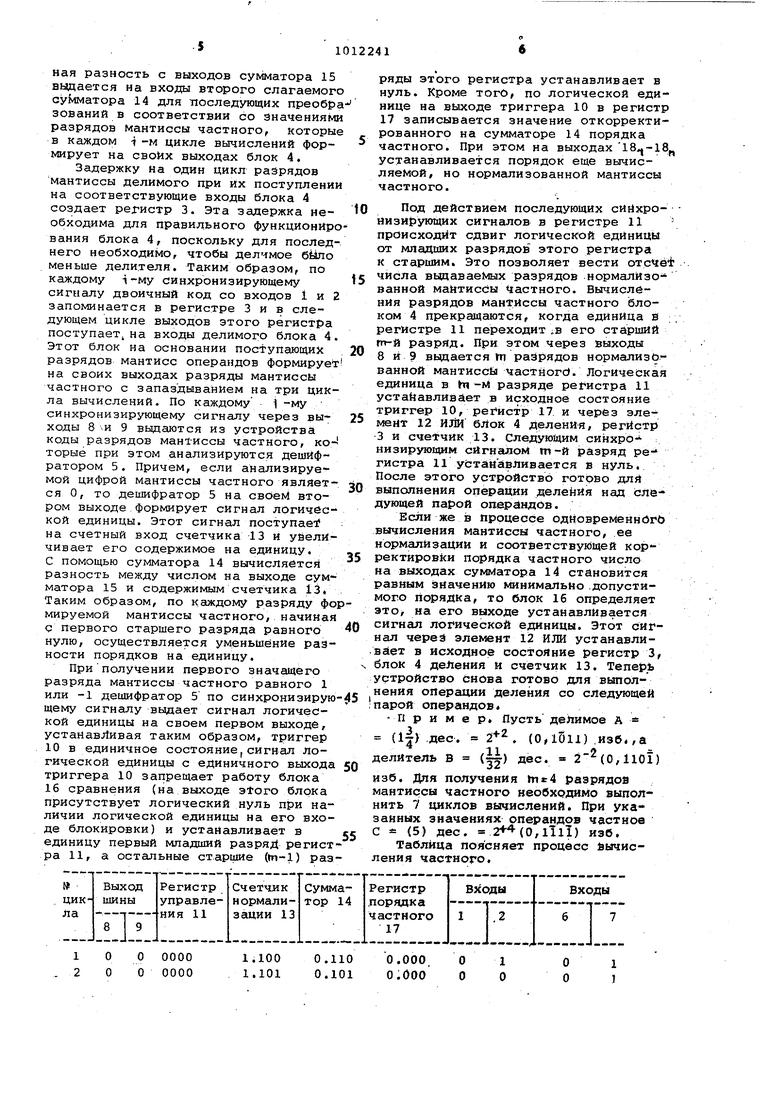

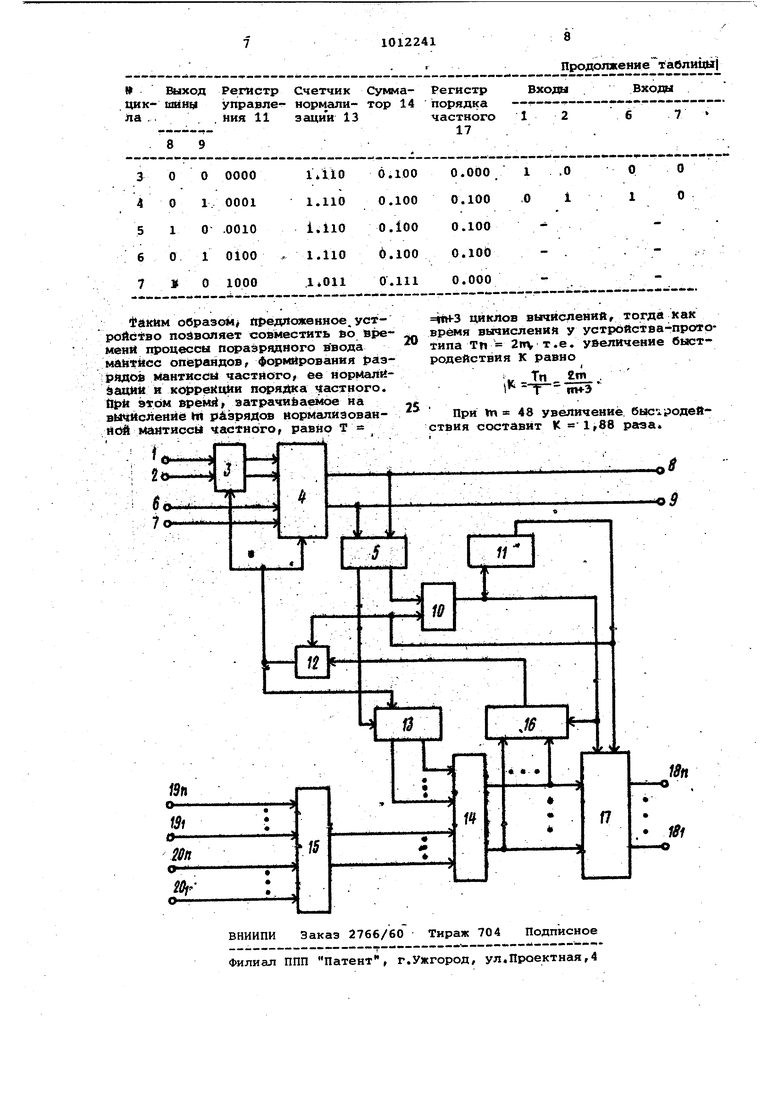

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных машинах для деления чисел в форме с плавающей запятой. Известно устройство для деления чисел, содержащее сумматор делимого регистр делимого, сумматор частного сумматор делителя, два сдвигающих регистра, пять элементов И, элемент ИЛИ, ключ, четыре триггера, два де-. пшфратора, счетчик и блок анализа знаков, позволяющее совместить во времени процессы поразрядного ввода операндов и их обработки, т.е. формирует частное по мере поразрядного поступления (старшими разрядами вперед) делимого .. и делителя на его входы С 1 .. Недостатком этого устройства является невозможность обработки one рандов в форме С плавающей запятой. Наиболее близким к предложенному по техническому решению является арифметическое устройство, содержащее блок деления, два сумматора порядков, три дешифрирующих устройства три фиксирующих схемы, схему Минус 1 и регистры 2. Однако при поразрядном вводе операндов, известное устройство обладает низким г.быстродействием. Объясняется это тем, то для. получения m разрядов (где m - разрядность мантисс опе рандов) мантиссы частного в указанных условиях такому устройству потребуется выполнить по крайней мере 2hi циклов вычислений, причем на протяжении первых tn циклов разряды мантиссы частного не формируются. При рыполнении последующих m циклов устройством осуществляется вычисление мантиссы частного. Кроме того, нормализация мантиссы и соответствую щая коррекция порядка проводится после вычисления мантиссы. Таким образом, известное устройст во - прототип не позволяет совмещать во времени поразрядный ввод операндов и их, обработку. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для деления чисел, содержащее буферный регистр, блок деления, сумматор порядков, де шифратор, триггер, счетчик нормализации, сумматор нормализации, блок сравнения и регистр порядка частного, причем входы порядков делимого и делителя устройства соединены с л первой и второй группами входов сум матора порядков соответственно, выходы счетчика нормализации соединены с первой группой входов сумматора нормализации, выходы которого соеди нены с информационными входами блока сравнения и регистра порядка час ного, выходы которого являются выходами порядка частного устройства, группа входов мантиссы делителя устройства соединена с входами делителя блока деления, выходы которого соединены с входами дешифратора, первый выход которого соединен с входом установки триггера в единичное состояние, введены сдвигающий регистр управления, и элемент ИЛИ, причем единичйый выход триггера соединен с входом разрешения записи регистра порядка частного, входом блокировки блока сравнения и входом установки сдвигающего регистра управления, выход старшего разряда которого соединен с входами установки в нулевое состояние регистра порядка частного и триггера и первым входом элемента ИЛИ, к второму входу которого подключен выход блока сравнения, а вы- ход элемента ИЛИ соединен с установочными входами счетчика нормализации, блока делений и буферного регистра, входы которого являются входами мантиссы делимого устройства, вЫходы соединены со входами делимого блока деления, выходы которого являются выходами мантиссы частного устройства, второй выход дешифратора соединен со счетным входом счетчика нормализации, выходы сумматора порядков соединены с второй группой входов сумматора нормализации. На чертеже представлена схема устройства. Устройство содержит входы 1 и 2 мантиссы делимого, буферный регистр 3, блок деления 4, дешифраФйр 5, входы б и 7 мантиссы ..-делителя, вы- « 8 и 9 мантиссы частного, -триггер 10, сдвигающийрегистр 11 управления, элемент 12 ИЛИ, счетчик 13 нормализации, сумматор 14 нормализации, сумматор 15 порядков, блок 16. сравнения, регистр 17 порядка Частного, выходы 18j-18 порядка частного,, входы и , порядков делимого и делителя соответственно. Входы 1 и 2 разрядов мантиссы делимого соединены с входами буферного регистра 3, выходы которого соедийены с входами делимого блока 4 деления, выходы которого являются выходами 8 и 9 мантиссы частного и соединен ны с входами дешифратора 5, первый выход которого соединен с входом установки в единичное состояние триггера 10, единичный выход которого соединен с входом разрешения записи регистра 17 порядка частного, входом блокировки 16 сравнения и входом установки регистра 11 управления, выход старшего разряда которого соединен с входами установки в нулевое состояние регистра 17 порядка частного, триггера 10 и первым входом элемента 12 ИЛИ, выход которого соединен с установочными входами буфёрного регистра 3, 0лока 4 деления и счетчика 13 нормализации-, выходы которого соеяин.ены с первой группой входов сумматора 14 нормализации, входы , и , порядков делимого и делителя соединены с пердой и второй сруппами входов суюлатора 15 порядков, выходы которого соединены с второй группой входов сумматора 14 нормализации, выходы которого соединены с входами 16 сравнения и регистра 17 порядка частного, выходы которого являются выходами порядка частного устройства, выход блока 16 сравнения . соединение вторым входом элемента 12 ИЛИ, входы 6 и 7 разрядов мантисeta делителя соедИнед1ы с входа ш делителя блока 4 деления.

Буферный регистр 3 представляет собой двухразрядный регистр с параллельиым. приемом и выдачей информации построенный на триггерах.

Блок 4 деления предназначен для деления последовательно поступающих, начиная со старюих разрядов, мантисс операндов, представленных в избыточной двоичнЬй системе счисления с цифра1ми 1,0 и 1. Такой блок деления может быть выполнен, например« по известной схеме, установки исходйого достояния регистров- блока 4 Соединены с его входом установки (управляющие входы и вход синхрони зации этого блока на чертеже не показаны) . Ё каждому t-м цикле вы исленйй (где i 1,2,3..:) этот блок при последовательном поступлении на его входы разрядов мантисс операндов с весом формирует на своих выходах разряды мантиссы частного с весоМ , т.е. разряды Мантиссы част ногО вычисляются с запаздыванием на три Циклам При этом Обеспечивается совмесцение во времени процессов пд разрядного ввода мантисс операндов и их обработки. .

Цифры избыточной двоичной системы с помсйлю которых представляются разряд мёштисс исходных операндов и частного, в свою очередь, изображены коАом канонической двоичной системы. Так, цифре -1 соотвётстйует . Наличие сигнала логической единицы на входах 1 или 6 или на выходе 8« Цифре 1 соответствует наличие сйгнала логической единицы на входах 2 или 7 или на выходе 9. Цифре О соо ветс твует отсутствие сигналов Логической единицы на входах 1, 2, 6 и 7 или на выходах 8 и 9.

Деишфратор 5 предназначен для . распознавания первого значаи его разряда мантиссы частного. Декодировагние кодов цифр этим дешифратором осуществляется по сигналам, синхронизирующих поступление разрядов мантисс

операндов и выдачу разрядов мантиссы частного (вход синхронизации дешифратора 5 не показан).

Регистр 11 управления представляе собой m -разрядный сдвигающий регист

Функционирование регистров 3 и 11, а также блока 4 и дешифратора 5 осуществляется под действием сигналов, синхронизирующих поступление рарядов мантиссы частного (входы синхронизации условно не показаны).

Блок 16 сравнения представляет собой схему сравнения чисел, выполняющую сравнение вычисляемого значейия порядка частного с величиной минимального порядка, при котором формируемое частное можно считать равным нулю. Величина такого минимального П(доядка заранее известна и равна (где h-1 - разрядность порядка без учета знакового разряда)

Для представления порядков операндов и частного используется каноническая двоичная система счисления. Значения Порядков представляются со знаком с помощью дополнительного кода.

В качестве сумматоров 14 и 15 могут быть использованы и -разрядные двоичные сумматоры комбинационного типа. Оба сумматора служат для выполнения операции вычитания с учетом знаков слагаемьк. Сумматсчр 15 вычисляет разность порядков делимого и делителя, для этого его всеп входов второго слагаемого, подключенного к входам , порядка1 делителя, являются инвертирующими, и на вход переноса младшего разряда этого сумматора., подается сигнал логической единицы. Сумматор 14 определяет разность между числом на выходе сумматора 15 и содержимым счетчика 13. Для этого все п входов первого слагаемого сумматора 14 также являются инвертирующими (они подключены к выходам счетчика 13).

Счетчик 13 норма 1изации - это И-разрядный двоичный счетчик, имеющи вход установки исходного состояния в обратном коде.

Устройство работает следующим образом.

Перед выполнением операции деления триггер и регистры устройства устанавливаются в нулевое состояние, а .блок 4 и счетчик 13 - в исходное. С появлением синхронизирукпцих сигналов на входы 1 и 2 и 6 и 7 поразрядно поступают соответственно коды разрядов мантисс делимого и делителя, начиная со старших разрядов. Одновременно с поступлением на входы 1, 2 и 6,7 первых старших разрядов мантисс операндов их порядки подаются на входы 19-j-19j, и 20,-20,. Сумматор 15 вычисляет разность поступивших порядков с учетом их знаков. Полученная разность с выходов сумматора 15 вьадается на входы второго слагаемого суКоиатора 14 для последующих преобра зований в соответствии со значениями разрядов Мантиссы частного, которые в каждом i-м цикле вычислений формирует на своих выходах блок 4. Задержку На один цикл разрядов мантиссы делимого при их поступлении на соответствующие входы блока 4 создает регистр 3. Эта задержка необходима для правильного функциониро вания блока 4, поскольку для последнего необходимо, чтобы делчмое бйпо меньше делителя. Таким образом, по каждому i-му синхронизирующему сигналу двоичный код со входов 1 и 2 запоминается в регистре 3 и в следующем цикле выходов этого регистра поступает, на входы делимого блока 4. Этот блок на основании поступающих разрядов мантисс операндов формирует на своих выходах разряды мантиссы частного с запаздыванием на три цикла вычислений. По каждому -му синхронизирующему сигналу через выходы 8 и 9 выдаются из устройства коды разрядов мантиссы частного, которые при этом анализируются дешифратором 5. Причем, если анализируемой цифрой мантиссы частного является О, то дешифратор 5 на свОеМ втором выходе формирует сигнал логической единицы. Этот сигнал поступает на счетный вход счетчика 13 и уйеличивает его содержимое на единицу. С помощью сумматора 14 вычисляется разность между числом на выходе сумматора 15 и содержимым счетчика 13 Таким образом, по каждому разряду фо мируемой мантиссы частного, начиная С первого старшего разряда равного нулю, осуществляется уменьшение разности порядков на единицу. Приполучении первого значащего разряда мантиссы частного равного 1 или -1 дешифратор 5 по синхронизирую щему сигналу выдает сигнал логической единицы на своем первом выходе, устанавливая таким образом, триггер 10 в единичное состояние,сигнал Логической единицы с единичного выхода триггера 10 запрещает работу блока 16 сравнения (на выходе э±ого блока присутствует логический нуль при наличии логической единицы на его входе блокировки) и устанавливает в единицу первый младший разряЛ регист ра 11, а остальные ст.аршие (т-1) раз ряды этого регистра устанавливает в нуль. Кроме того, по логической единице на выходе триггера 10 в регистр 17 записывается значение откорректированного на сумматоре 14 порядка частного. При этом на выходах 18.|-18д устанавливается порядок еще вычисляемой, но нормализованной мантиссы частного. Под действием последующих синхронизирующих сигналов в регистре 11 происходит сдвиг логической единицы от младших разрядов этого регистра к старшим. Это позволяет вести отсчёт числа вьиаваемых разрядов нормалйзо ванной майтиссы Частного. Вычисления разрядов мантиссы частного блоком 4 прекращаются, когда едИнИца Ef . регистре 11 переходит ,в его старший гп-й разряд. При этом через выходы 8 и 9 выдается tn разрядов нормализованной мантиссй частногс. Логическая единица в hi-М разряде реГИстра 11 устайавлийает в исходное состояние триггерЮ, регистр 17 и через элемент 12 HJlH бЛок 4 Деления, регистр 3 и счетЬчиК 13. Следующим синхро низирующим сигналом m -и разряд ре- гистра 11 устанавливается в нуль. После этого устройство готово дли выполнения операции делеййя над следующей парой операндов. Если же в процессе одйовременнйгй вычисления мантиссы частного, ее нормализации и соответствующей корректировки порядка частного число на выходах сумматора 14 становится равным значению минимально .допустимого порядка, то блок 16 определяет это, на его выходе устанавливается сигнал логической единицы. Этот сигнал черей элемент 12 ИЛИ устанавливает в исходное состояние регистр 3, блок 4 деления и счетчик 13. TeneiJb устройство снова готово для выполнения операции деления со следующей парой операндов пример. Пусть делимое А - (l|) .дес. 2. (0,1011) .изб.,а делитель В (||) две. 2(0,1101) изб. Для получения hi г4 разрядов мантиссы частного необходимо выполнить 7 циклов вычислений. При указанных значениях операндов частное С (5) дес. г«(0,1111) изб. Таблица поясняет процесс вычисления частного.

Продолжение та6лиЫг|

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Вычислительное устройство | 1983 |

|

SU1173411A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

Факим образой гфедяожеиное устройство позволяет совместить &о времени процессы псфазрядного ввода маЬтйес оП1Ёраядов, формирования раэ;РИДОВ мантиссы частного ее нормапйдадйй и коррекции )Я2(ка частного. Йрй этом BpeMfti затрачиваемое на вы ч йсленйё Hrt разрядов нормалиэованйбй мантиссй частного I равно Т

:ПН-3 ЦИКЛОВ вычйсленийг тогда как время вычислений у устройства-прототипа Tti 2п т.е. увеличение быстродействия К равно

т+э

При tn 48 увеличение, быс родействия составит К 1,88 раза.

| Устройство для деления | 1976 |

|

SU590738A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1983-04-15—Публикация

1981-12-08—Подача