J .t .3 .1

./7 ТТ

а

4

00

О

Фи.1

1 U

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении арифмети- еских устройств вычислительных машин, а также в устройствах цифровой обработки сигналов, работающих в системе счисления с плавающей запятой.

Целью изобретения является повьше- ше быстродействия.

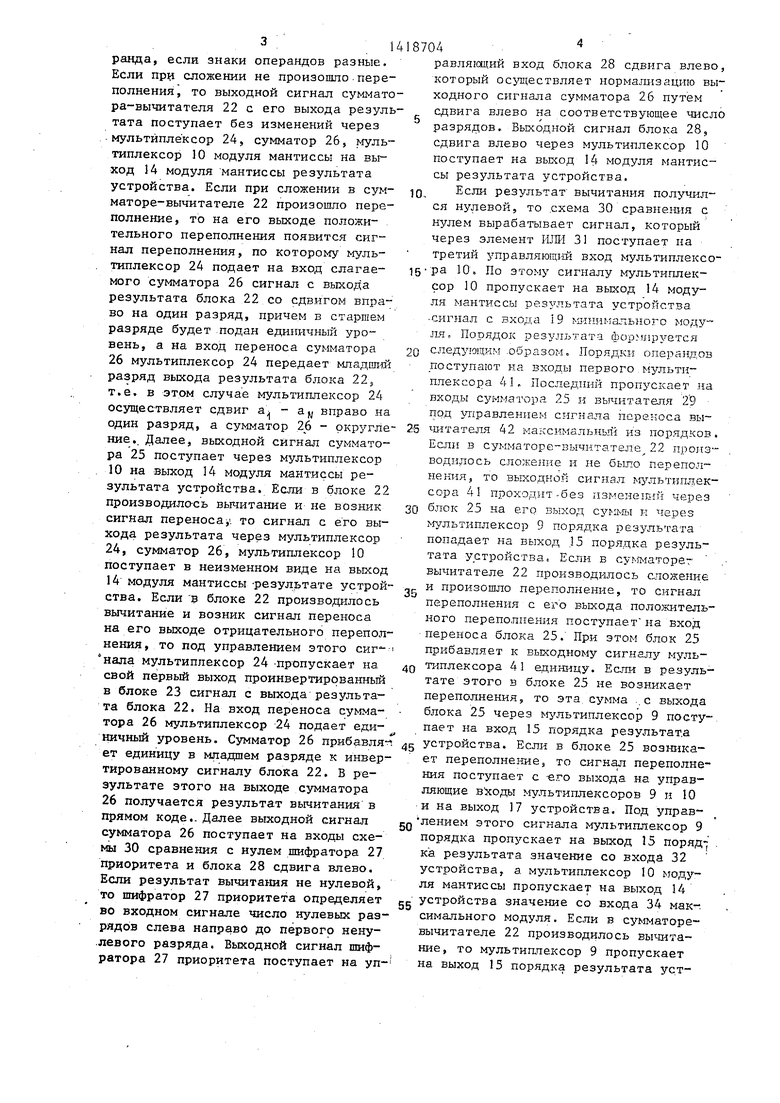

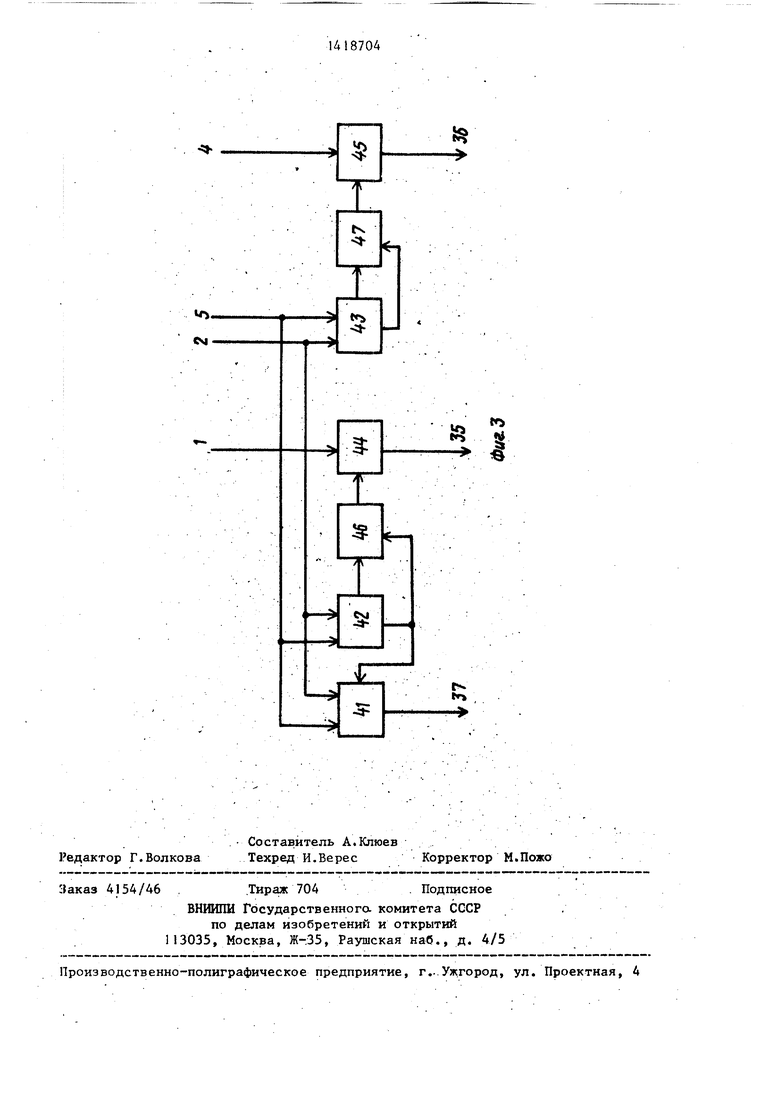

На фиг.1 представлена схема уст- ойства для суммирования двух норма- jjmsoBEHHbix чисел с плавающей запятой; а фиг.2 - схема мультиплексора; на фиг.З - схема блока выравнивания. Устройство (фиг. содержит вход 1 модуля мантиссы первого операнда устройства, вход 2. порядка первого Операнда устройства, вход 3 знака г ервого операнда устройства, вход - 4 Цодупя мантиссы второго операнда уст- 1|ойства, -вход 5 порядка второго опе- авда устройства, вход 6 знака второ- фо операнда устройства, вход 7 сигна 4а смены знака первого операнда уст- 1 ойства, вход 8 сигнала смены знака иторого оперенда устройства, мультиплексор 9 порядка, мультиплексор 10 г одуля мантиссы, элементы ИСКЛЮЧАЮ- |ЕЕ ИЛИ 11 и 12, 13 выравнива- ,, выход 14 модуля мантиссы резуль- т:ата устройства, выход 15. порядка ре- з1ультата устройства, выход 16 знака {результата устройства, выход 17 сиг- Йала переполнения порядка-устройства аыход 18 сигнала исчезновения значи- йости устройства, вход 19 минимально li o модуля устройства, элементы ИСКЛЮ ЧАЩЕЕ или 20 и 21, сумматор-вычита- тель 22, блок 23 элементов НЕ, муль- иплексор 24, первый 25 и второй 26 сумматоры, шифра:тор 27 приоритета, блок 28 сдвига влево, вычитатель 29, схему 30 сравнения с нулем, элемент ИЛИ 31, вход 32 максимального порядка устройства, вход 33 минимального порядка устройства, вход 34 макси. мального модуля устройства, первый 35 и второй 36 выходы мантиссы блока 3 выравнивания, выход 37 порядка блока 13 выравнивания, первый 38 и второй 39 выходы мультиплексора 24.

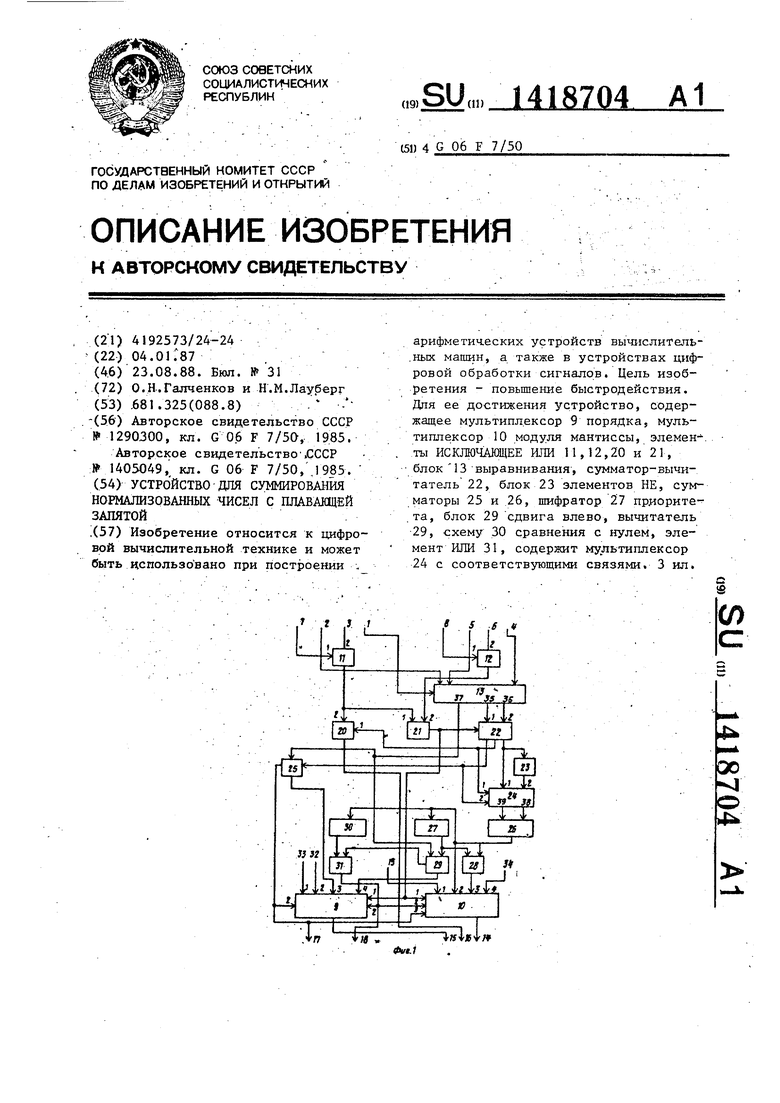

Мультиплексор 24 (фиг.2) содержит одноразрядные мультиплексоры 40.0- 40 N (N - разрядность модуля мантиссы) .

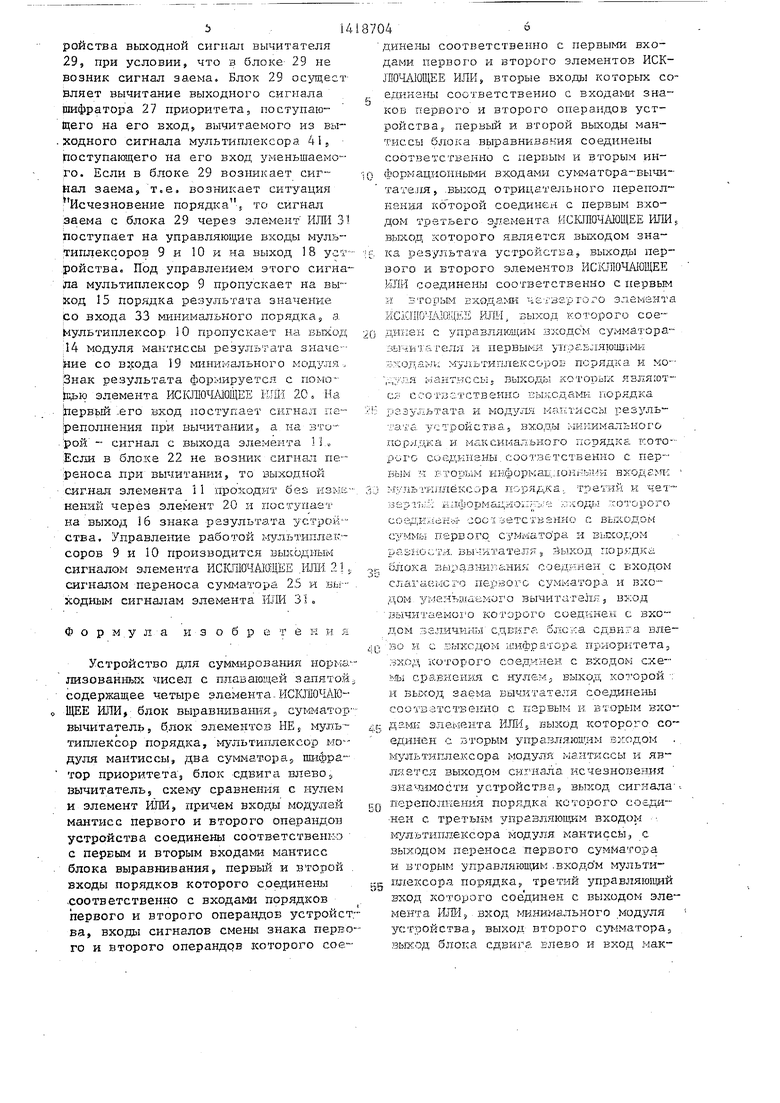

Блок 13 выравнивания (фиг.З) содержит мультиплексор 41, вычИтатели

7042

42 и 43, сдвигатели 44 и 45 вправо, группы 46 и 47 элементов запрета.

Устройство (фиг.1) работает сле- дукщим образом.

На входы 1-3 устройства подается, первый операнд в форме с плавающей запятой, на входы 4-6 устройства подается второй операнд в форме с п,паQ вакяцей запятой. При необходимости знак мантиссы операнда может быть изменен, на противоположный. Для этого на входы 7 и 8 подаются соответственно сигнал смены знака в первом

5 операнде и сигнал смены знака во втором операвде. В этом случае на выходах элементов ИСКШОЧАЩЕЕ ИЛИ 11 и . . 12 соответственно формируются противоположные знаки операндов. Сигналы

0 с выходов элементов ИСКЛЮЧАНЩЕЕ ИЛИ II и 12 поступают на входы элемента ИСКЛЮЧАЩЕЕ ИЛИ 21, выходной сигнал которого поступает на сумматор-вычи- татель 22 и определяет вид операции

5 (суммирование или вычитание), которая производится над модулями мантисс. Порядки операндов поступают на вычитатели 42 и 43 и на входы мультиплексора 41. Вычитатель 42 вычитает

0 из порядка второго операнда порядок первого операнда. Если эта разность неотрицательна, то сигнал с выхода разности вычитателя 42 поступает через группу элементов 46 запрета на управлякщий вход с;цвигателя . 44 вправо. В противном случае, на выходе вычитателя 42 появляется сигнал переноса, который блокирует группу элементов 46 запрета таким образом, что

- выдается управляющий сигнал на сдви- гатель 44 вправо, соответствующий пропусканию модуля мантиссы первого операвда без сдвига. Вычита тепь 44 и группа 47 элемен тов запрета работают аналогично блокам 42 и 46, за

5

5

0

5

исключением того, что вычитатель 43 из порядка первого операнда вычитает порядок второго операйда. Модули мантисс первого и второго операнда с .соответствующих входов 1 и 4 первого и второг;о операндов поступают - через сдвигатели 44 и 45 вправо на первый и второй входы суммато- ра-вычитателя 22 соответственно.

Сумматор-вычитатель 22 либо скла- , дывает модули мантисс операндов, если знаки операндов совпадают, либо из модуля мантиссы первого операнда вычитает модуль майтиссы второго one3 ; ,141

анда, если знаки операндов разные. сли при сложении не произошло переолнения , то выходной сигнал суммато- а-вычитателя 22 с его выхода результата поступает без изменений через

мультиплексор 24, сумматор 26, мультиплексор 10 модуля мантиссы на выод 14 модуля мантиссы результата стройства. Если при сложении в сум- аторе-вычитателе 22 произошло переполнение, то на его выходе положительного переполнения появится сигнал переполнения, по которому мультиплексор 24 подает на вход слагаемого сумматора 26 сигнал с выхода результата блока 22 со сдвигом вправо на один разряд, причем в старшем разряде будет подан единичный уровень, а на вход переноса сумматора 26 мультиплексор 24 передает младппш разряд выхода результата блока 22, т.е. в этом случае мультиплексор 24 осуществляет сдвиг а ajj вправо на один разряд, а сумматор 26 - округление. Далее, выходной сигнал сумматора 25 поступает через мультиплексор 10 на выход 14 модуля мантиссы результата устройства. Если в блоке 22 производилась вычитание и не возник сигнал переноса , то сигнал с его выода результата через мультиплексор 24, сумматор 26, мультиплексор 10 поступает в неизменном виде на выход 14 модуля мантиссы -результате устройства. Если блоке 22 производилось вычитание и возник сигнал переноса на его выходе отрицательного переполнения, то под управлением этого сиг нала мультиплексор 24 -пропускает на свой первый выход проинвертиррванный в блоке 23 сигнал с выхода результата блока 22. На вход переноса сумматора 26 мультиплексор 24 подает единичный уровень. Сумматор 26 прибавля-i ет единицу в младшем разряде к инвертированному сигналу блока 22. В результате этого на выходе сумматора 26 получается результат вычитания в прямом коде.. Далее выходной сигнал сумматора 26 поступает на входы схемы 30 сравнения с нулем шифратора 27 приоритета и блока 28 сдвига влево. Если результат вычита шя не нулевой, то шифратор 27 приоритета определяет во входном сигнале число нулевых разрядов слева направо до первого нену- евого разряда. Выходной сигнал шифратора 27 приоритета поступает на уп4

равля а ций вход блока 28 сдвига влево, который ос тцествляет нормализацию выходного сигнала сумматора 26 путем сдвига влево на соответствующее число разрядов. Выходной сигнал блока 28, сдвига влево через мультиплексор 10 поступает на выход 14 модуля мантиссы результата устройства.

Если результат вычитания получился нулевой, то .схема 30 сравнения с нулем вырабатывает сигнал, который через элемент ИЖ 31 поступает на третий управляющий вход мультиплексора 10. По этому сигналу мультиплексор 10 пропускает на выход 14 модуля мантиссы результата устройства сигнал с входа i 9 мнинмгдльного модуля. Порядок результата форМ1 руется

следующим .образом. Порядки операндов поступают на входы первого мультиплексора 41, Последний пропускает .на входы сумматора 25 и вычитателя 29 пр.д управлением сигнала пореыоса вы штателя 42 максимальньш из порядков. Если в суыматоре-вычитателе 22 производилось сложение и не было перепел- некия, то выходной сигнал .нплек- сора 41 проходит-без изменений через

блок 25 на его выход суммы к через гультиплексор 9 порядка результата попадает на выход .15 поря.дка результата уртройства. Если в су. 5маторег вычитателе 22 прокзводршось сложение

и произошло переполнение, то сигнал переполнения с его выхода положительного переполнения поступает на вход переноса блока 25. При этом блок 25 прибавляет к выходному сигналу мультиплексора 41 единицу. Если в результате этого в блоке 25 не возникает переполнения, то эта. сумма ., с выхода блока 25 через мультиплексор 9 посту-, пает на вход 15 порядка результата

устройства. Если в блоке 25 возника- ет переполнение 3 то сигнал переполнения поступает с -его выхода на управляющие в:ходы мультиплексоров 9 и 10 и на выход 17 устройства. Под управ лением этого сигнала мультиплексор 9 порядка пропускает на выход 15 поряд- . ка результата значение со входа 32 устройства, а мультиплексор 10 модуля мантиссы пропускает на выход 14

устройства значение со входа 34 мак-, симального модуля. Если в сумматоре™ вычитателе 22 производилось ние, то мультиплексор 9 пропускает на выход 15 порядка результата усть141

ройства выходной сигншт вычитателя 29, при условии, что в блоке 29 не возник сигнал эаема. Блок 29 ос;,пдест вляет вычитание выходного сигнала шифратора 27 приоритета, поступаю- цего на его вход вычитаемого из вы- .ходного сигнала мультиплексора 41, поступающего на его вход уменьшаемого. Если в блоке 29 возникает сиг- Нал заема, т,е, возникает ситуация Исчезновение порядка, то сигнал эаема с блока 29 через элемент liJDi 31 поступает на управляю цие входы муль- Типлексорозз 9 и 10 и на выход 18 устройства. Под управлением этого сигнала мультиплексор 9 пропускает на вы- код 15 порядка результата значение со входа 33 минимального порядкаэ а. Мультиплексор 10 пропускает на выход 14 модуля мантиссы результата значе-- Йие со входа 19 шнимaльнoгo модуля,. Знак результата формируется с ью элемента ИСЮТЮЧАЮЩЕЕ ИТШ 20, На 1ервь1Й .его вход поступает сигнал переполнения при вычитании, а на зто- рой - сигнал с выхода элемента ГГ„ Если в блоке 22 не возник сигнал переноса лри вычитании, то выходной Сигнал элемента 11 прокодит без изый.-- нений через элемент 20 и поступает на выход 16 знака результата устройства. Управление работой мультиплексоров 9 и 10 производится выходным сигналом элемента ИCICГiIO Ч.AjG ДEE .ИЛИ 2 ,. сигналом переноса сумматора 25 и вы- . ходным сигналам элемента ИЛИ 31 .

Ф о р :м, у л а изобретения

Устройство д,ля суммирования норма - fiHSOBaHtn ix чисел с плавающей запятой,; содержащее четыре элемента.PICI liO lA-lO ЩЕЕ ИЛИ, блок выравнивания5 вычитатель, б.лок элементо а НЕ s ль -- типлексор порядка. Мультиплексор мо-- дуля мантиссы, два cyi iMSTopaj шифра тор приоритетаэ блок сдвига влево вычитатель, схему сравнения с нулем и элемент ИШ, причем входы модулей мантисс первого и второго операндов устройства соединены соответственко с первым и вторым входами мантисс

блока выравнивания, первый и второй , входы порядков которого соединены .соответственно с входами порядков первого и второго операндов устройст; - ва, входы сигналов смены знака первого и второго операндов которого сое46

инены соответственно с первыми входами первого и второго элементов ИСК- JW-L UOniEE ИЛИ, вторые входы которых со- единеш соответственно с входам- знаков первого и второго операндов устройства j, первый и второй выходы мантиссы блока выравнивания соединены соответственно с первым и вторым информационньгми входами сумматора-вычи- тателя, ,выход отрицательнох о переполнения которой соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ выход которо го ,является вькодом знака результата устройства, выходр первого и второго элементов ИСКШОЧАЮЩЕЕ )ЖИ соединены соответственно с первым и вторым входами че гзерто.го элемента ИСКПЮ -ШОЩЕЕ ШШ, выход которого соедикеы с управляющим зходо м сумматора- иычи гагеля и первыми утгоавляющамк о: ;;ода;- 1; мультиплексороЕ порядка и мо-- , мантиссыJ выходы которых являют- с;; ссствгтственно Еы,асдами порядка

раэультата и модуля каь;тиссы резуль- л ата, устройства, входы микимальногс/ порядка и макси1- ального порядка которого соедкнены,соотзетственно с первым я вторым инфоркац,:1О1-1ЯЫ и вкoдг iк

мупь 1 К шёксора порядка, третий к чет- вap гь,/: илформацио;: ;, ;. которого соэдил1.;ко(- сос г зетствйныо с вьжодом первого сумматсгра и вькодом рааности. вычнтателя-, йыход порядка

блока зыразниУ &ния соединен с входом

слагаемоГ О перзогс сумматора и входом уменьшаемого вычитателя, вход Бычитаемо1 о которого соединен с входом величины сдвига блока сдвига влево и с выходом шифратора приорктета, зход которого соединен с входом схе- ;Ф1 сравнения с нулемj выход которой ; и вькод заема вычктателя соотвзтственно с первым к вторым входгмЕ элемента выход которого со единен с вторым управляющим входом мультиплексора модуля мантиссы и является выходом св;г нала исчезновения ,зна,чз5мости устройства J выход сигнала переполнения порядка котооого соеди

ней с третьим управляющим входом ,т-.{ультиплексора модуля мантиссы, с выходом переноса первого сумматора и вторым управляюа|;им .вкодо м мульти- шхексора порядка, третий управляющий вход которого соединен с выходом элемента ИЖ, вход минимального модуля ус тройства S выход второго суг-шатораэ выход блока сдвига влево и вход мак 714

симального модуля устройства соединены соответственяо с информационными входами с первого по четвертый мультиплексора модуля мантиссы, отличающееся тем, что, с целью повьпаения быстродействия, оно содержит мультиплексор, причем выход результата сумматора-вычитателя соединен с первым информационным входом мультиплексора и через блок элементов НЕ,- с вторым информационным входом мультиплексора, первый и второй выходы которого соединены соответственно с входом слагаемого и входом

48

переноса второго сумматора, выход суммы которого соединен с входом шифратора приоритета и информационным входом блока сдвига влево, выход отрицательного переполнения сумматора- вычитателя соединен с первым управ- лягацим входом мультиплексор, второй управляющий вход которого соединен

с входом переноса первого сумматора и выходом положительного переполнения сумматора-вычитателя, -выход первого элемента ИСКЛЮЧАЩЕЕ ИЛИ соединен с вторым входом третьего элбмента ИСКЛЮЧАЮЩЕЕ ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования двух чисел с плавающей запятой | 1985 |

|

SU1405049A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| Устройство для выравнивания порядков чисел,представленных в системе остаточных классов | 1973 |

|

SU781812A1 |

| Устройство для сложения операндов с плавающей точкой с контролем | 1986 |

|

SU1310826A1 |

| Устройство для обработки данных | 1987 |

|

SU1513443A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1991 |

|

SU1784971A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-04—Подача