Изобретение относится к области вычислительной техники и может быть использовано в сверхбольших интегральных схемах (СБИС) при реализации арифметических и логических устройств.

Известна реализация последовательного сумматора на основе парафазных динамических КМДП схем с предзарядом (Патент США 5491653, G 06 F 7/50, НКИ 364-784 от 13.02.1996). Особенностью данного технического решения является реализация функций сложения в каждом разряде в виде схемных КМДП макроэлементов, логическая часть которых выполняется только на транзисторах n-типа. Это сокращает число простейших последовательно включенных логических элементов, необходимых для выполнения функций суммирования. Недостатком данного устройства является невысокое быстродействие, что обусловлено необходимостью противофазного трехтактного тактирования соседних разрядов. Поэтому каждый последующий разряд функционирует только после полного срабатывания предыдущего, что увеличивает длительность тактов и снижает быстродействие.

Наиболее близким техническим решением к предлагаемому является сумматор на основе каскадного логического устройства на КМДП транзисторах (Патент РФ 2132591, фиг.1 и 2, НО 3 К 19/00 от 24.04.1998). Это устройство, принятое за прототип, содержит последовательно включенные каскады - разряды сумматора, работающие под общим однофазным тактированием с асинхронной последовательной передачей сигнала переноса и поразрядным суммированием при наличии парафазных входных и выходных сигналов. Логическая часть реализована на ключевых цепях только из транзисторов n-типа с раздельным выполнением функций суммы и переноса. Недостаток этого устройства - ограниченное быстродействие, что обусловлено избыточными емкостными нагрузками в цепях последовательного распространения переноса. В частности выход переноса логического блока имеет в качестве нагрузки КМДП инвертор, т.е. затворы транзисторов р- и n-типов. Вторая ступень переноса - сам инвертор нагружен на два транзистора р-типа в предзарядовой части и на два транзистора n-типа в логическом блоке последующего разряда. Наличие нескольких емкостных нагрузок увеличивает задержки распространения сигнала переноса и снижет быстродействие устройства.

Технической задачей, решаемой в изобретении, является повышение быстродействия устройства.

Поставленная цель достигается тем, что сумматор на КМДП транзисторах, содержащий тактовый транзистор n-типа и в первом разряде - два инвертора, триггер-фиксатор, четыре транзистора р-типа и логический блок, содержащий восемнадцать транзисторов n-типа, из которых соединены последовательно парами в цепи первый и второй транзисторы n-типа, третий и четвертый, пятый и шестой, седьмой и восьмой, девятый и десятый, одиннадцатый и двенадцатый, тринадцатый и четырнадцатый, пятнадцатый и шестнадцатый транзисторы n-типа, образуя соответствующие ключевые цепи, средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены, первая и вторая ключевые цепи соединены параллельно и подключены общими стоками первого и третьего транзисторов n-типа к первому выходу логического блока, а общими истоками второго и четвертого транзисторов через семнадцатый транзистор n-типа - к нулевой шине, третья и четвертая ключевые цепи соединены параллельно и подключены общими стоками пятого и седьмого транзисторов n-типа к второму выходу логического блока, а общими истоками шестого и восьмого транзисторов через восемнадцатый транзистор n-типа - к нулевой шине, первый и второй выходы логического блока соединены соответственно через первый и второй транзисторы р-типа с шиной питания и подключены непосредственно к соответствующим входам триггера-фиксатора, выходы которого являются выводами результата суммирования в данном разряде, пятая и шестая ключевые цепи объединенными стоками девятого и одиннадцатого транзисторов n-типа подключены к третьему выходу логического блока, который соединен с логическим входом первого инвертора непосредственно, а через третий транзистор р-типа - с шиной питания, седьмая и восьмая ключевые цепи объединенными стоками тринадцатого и пятнадцатого транзисторов n-типа подключены к четвертому выходу логического блока, который соединен с логическим входом второго инвертора непосредственно, а через четвертый транзистор р-типа - с шиной питания, затворы первого, пятого и одиннадцатого транзисторов n-типа подключены к прямому входу, а затворы третьего, седьмого и пятнадцатого транзисторов n-типа - к дополнительному входу, на которые подаются парафазные сигналы первой переменной разряда, затворы второго, шестого и шестнадцатого транзисторов n-типа подключены к прямому входу, а затворы четвертого, восьмого и двенадцатого транзисторов n-типа - к дополнительному входу, на которые попадаются парафазные сигналы второй переменной разряда, затворы семнадцатого и восемнадцатого транзисторов n-типа являются парафазными входами переноса, затворы транзисторов р-типа и затвор тактового транзистора n-типа, который включен между шиной земли и нулевой шиной, подключены к тактовому входу сумматора, выходы первого и второго инверторов подключены к соответствующим входам переноса последующего разряда, содержит дополнительный инвертор и тактовый транзистор р-типа, затвор которого соединен с выходом дополнительного инвертора, вход которого подключен к тактовому входу сумматора, причем все разряды сумматора выполнены идентично с первым разрядом, в логический блок которого введены девятнадцатый и двадцатый транзисторы n-типа, первый из которых включен между средней точкой шестой ключевой цепи и нулевой шиной, а второй - между средней точкой восьмой ключевой цепи и нулевой шиной, истоки десятого и двенадцатого транзисторов n-типа подключены к общей точке второго и семнадцатого транзисторов n-типа, а истоки четырнадцатого и шестнадцатого транзисторов n-типа соединены с общей точкой шестого и восемнадцатого транзисторов n-типа, затворы тринадцатого и девятого транзисторов n-типа подключены соответственно к прямому и дополнительному входам первой переменной разряда, затворы десятого и девятнадцатого транзисторов n-типа подключены к прямому входу, а затворы четырнадцатого и двадцатого транзисторов n-типа - к дополнительному входу второй переменной разряда, первый и второй инверторы выполнены тактируемыми, причем затвор транзистора р-типа каждого инвертора является его логическим входом, а затвор транзистора n-типа - его тактовым входом, который подключен к выходу дополнительного инвертора, клеммы положительного питания обоих инверторов соединены с шиной питания через тактовый транзистор р-типа.

Существенными отличительными признаками в указанной совокупности признаков является наличие в устройстве дополнительного инвертора и связанного с ним тактового транзистора р-типа, введение в логический блок первого разряда дополнительно двух транзисторов n-типа в сочетании с новой конфигурацией ключевых цепей, выполнение инверторов тактируемыми с разделением функций управления затворами их транзисторов и стробированием питания через тактовый транзистор р-типа, а также выполнение всех разрядов сумматора идентичными с первым.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - повышение быстродействия устройства. Действительно, благодаря введению в логический блок дополнительно двух транзисторов n-типа ключевые цепи, реализующие функции суммы и переноса объединены таким образом, что каждый вход переноса из предыдущего разряда фиксируется на затворе только одного транзистора n-типа, что при отсутствии других нагрузок со стороны транзисторов р-типа минимизирует емкостную нагрузку на выходах инверторов и уменьшает задержку их переключения. Выполнение самих инверторов тактируемыми в сочетании с тактовым транзистором р-типа и, в том числе, использование в качестве логического входа инвертора только затвора его транзистора р-типа, уменьшает емкостную нагрузку на выходе логического блока при формировании сигнала переноса. Таким образом, в критической цепи распространения сигнала переноса, определяющей быстродействие сумматора в целом, число нагрузок на каждой ступени сводится к минимуму - к емкости затвора одного транзистора. А минимизация числа нагрузок позволяет реализовать разряд сумматора на транзисторах с минимальными технологическими размерами и, таким образом, величину самой единичной нагрузки свести к минимуму. При этом сохраняется однотактовый принцип функционирования многоразрядного сумматора в асинхронном режиме, когда за счет одновременной работы нескольких разрядов сокращается время такта суммирования.

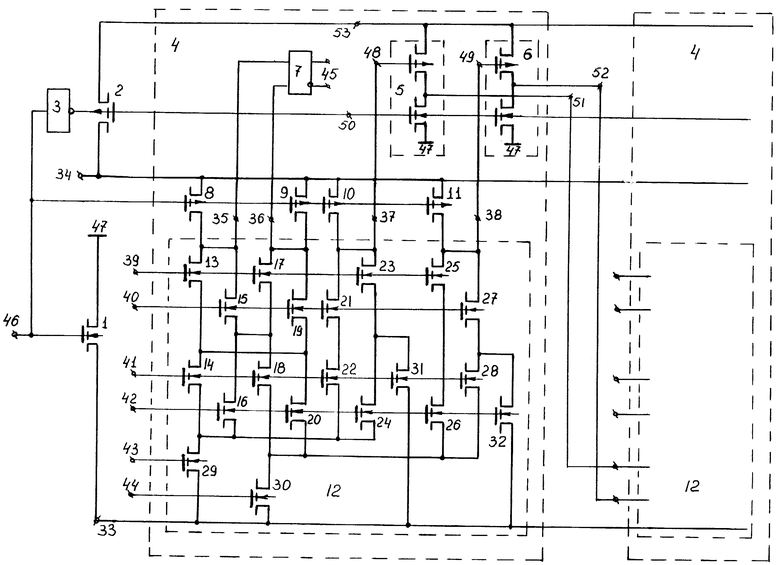

На чертеже приведена принципиальная схема заявляемого сумматора на КМДП транзисторах.

Сумматор на КМДП транзисторах содержит тактовый транзистор 1 n-типа, тактовый транзистор 2 р-типа, дополнительный инвертор 3 и разряды 4. Каждый разряд 4 сумматора содержит первый 5 и второй 6 инверторы, триггер-фиксатор 7, четыре транзистора 8-11 р-типа и логический блок 12, выполненный на двадцати транзисторах 13-32 n-типа.

В логическом блоке 12 транзисторы n-типа с первого 13 по шестнадцатый 28 соединены парами последовательно, образуя соответствующие ключевые цепи, первый 13 - со вторым 14, третий 15 - с четвертым 16, пятый 17 - с шестым 18, седьмой 19 - с восьмым 20, девятый 21- с десятым 22, одиннадцатый 23 - с двенадцатым 24, тринадцатый 25 - с четырнадцатым 26 и пятнадцатый 27- с шестнадцатым 28. Средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены. Объединенные между собой истоки второго 14, четвертого 16, десятого 22 и двенадцатого 24 транзисторов n-типа соединены через семнадцатый 29 транзистор n-типа с нулевой шиной 33, а объединенные между собой истоки шестого 18, восьмого 20, четырнадцатого 26 и шестнадцатого 28 транзисторов n-типа соединены через восемнадцатый 30 транзистор n-типа также с нулевой шиной 33. Девятнадцатый 31 транзистор n-типа включен между общей точкой одиннадцатого 23 и двенадцатого 24 транзисторов n-типа и нулевой шиной 33, а двадцатый транзистор n-типа включен между общей точкой пятнадцатого 27 и шестнадцатого 28 транзисторов n-типа и нулевой шиной 33.

Первая и вторая ключевые цепи объединенными стоками первого 13 и третьего 15 транзисторов n-типа подключены через первый 8 транзистор р-типа к шине питания 34 и соединены непосредственно с первым 35 выходом логического блока 12, а третья и четвертая ключевые цепи объединенными между собой стоками пятого 17 и седьмого 19 транзисторов n-типа подключены через второй 9 транзистор р-типа к шине питания 34 и соединены непосредственно с вторым 36 выходом логического блока 12. Пятая и шестая ключевые цепи объединенными между собой стоками девятого 21 и одиннадцатого 23 транзисторов n-типа подключены через третий 10 транзистор р-типа с шиной питания 34 и соединены непосредственно с третьим 37 выходом логического блока 12, а седьмая и восьмая ключевые цепи объединенными между собой стоками тринадцатого 25 и пятнадцатого 27 транзисторов n-типа подключены через четвертый 11 транзистор р-типа с шиной питания 34 и соединены непосредственно с четвертым 38 выходом логического блока 12.

Затворы первого 13, пятого 17, одиннадцатого 23 и тринадцатого 25 транзисторов n-типа подключены к прямому входу 39, а затворы третьего 15, седьмого 19, девятого 21 и пятнадцатого 27 транзисторов n-типа - к дополнительному входу 40 первой переменной разряда. Затворы второго 14, шестого 18, десятого 22, шестнадцатого 28 и девятнадцатого 31 транзисторов n-типа подключены к прямому входу 41 второй переменной разряда, а затворы четвертого 16, восьмого 20, двенадцатого 24, четырнадцатого 26 и двадцатого 32 транзисторов n-типа подключены к дополнительному входу той же переменной. Затворы семнадцатого 29 и восемнадцатого 30 транзисторов n-типа подключены соответственно к парафахным 43 и парафазному 44 входам переноса.

Первый 35 и второй 36 выходы логического блока 12 подключены к входам триггера-фиксатора 7, выходы 45 которого являются выходами результата суммирования в данном разряде.

Затвор тактового транзистора 1 n-типа, вход дополнительного инвертора 3 и затворы транзисторов 8-11 р-типа в каждом разряде 4 подключены к тактовому входу 46 сумматора. Тактовый транзистор 1 n-типа включен между шиной земли 47 и нулевой шиной 33.

Первый 5 и второй 6 инверторы включены как обычно между клеммами положительного питания 53 и шиной земли 47 и выполнены тактируемыми, причем затворы транзисторов р-типа инверторов являются их логическими входами, а затворы транзисторов n-типа - их тактовыми входами. Логические входы 48 первого 5 и 49 - второго 6 инверторов подключены соответственно к третьему 37 и четвертому 38 выходам логического блока 12. Тактовые входы 50 первого и второго инверторов соединены с затвором тактового транзистора 2 р-типа и подключены к выходу дополнительного инвертора 3. Выходы 51 первого 5 и 52 второго 6 инверторов подключены соответственно к парафазным 43 и 44 входам переноса последующего разряда 4. Клеммы положительного питания 53 обоих инверторов 5 и 6 соединены с шиной питания 34 через тактовый транзистор 2 р-типа.

Триггер-фиксатор 7 может быть выполнен на двух КМДП элементах 2И-НЕ, первые входы которых являются входами триггера-фиксатора, а вторые - входами обратной связи с выхода парного элемента 2И-НЕ.

Сумматор на КМДП транзисторах работает следующим образом. В исходном состоянии - на первом полутакте, при отсутствии положительного сигнала на тактовом входе 46 сумматора тактовые транзисторы 1 и 2 закрыты, а транзисторы р-типа 8-11 - открыты. От шины питания 34 через транзисторы 8-11 р-типа происходит процесс предзаряда узловых емкостей, связанных с выходами 35-38 логического блока 12 до уровня логической 1. Клеммы 53 положительного питания первого 5 и второго 6 инверторов изолированы от шины питания 34 и, благодаря открытым транзисторам n-типа этих инверторов на выходах 51 и 52 инверторов поддерживаются состояния логического 0. Триггеры-фиксаторы 7 во всех разрядах 4 находятся при этом в режиме хранения результата предыдущего такта суммирования, поскольку на их входах присутствуют сигналы логической 1. На первом полутакте на прямые 39, 41 и дополнительные 40, 42 входы первой и второй переменных всех разрядов от внешнего устройства подаются соответствующие сигналы в прямом и дополнительном (парафазном) виде. Например, когда суммируются числа А=1 и В=0, на входы 39 и 42 подаются сигналы логической 1, а на входы 40 и 41 - сигналы логического 0. На входы 43 и 44 переноса первого разряда от того же внешнего устройства одновременно поданы сигналы отложенного переноса С, например, при С=1 - соответственно логической 1 и логического 0. На входах переноса 43 и 44 остальных разрядов присутствуют только сигналы логического 0, что гарантирует суммирование всех трех переменных в каждом разряде только после поступления значимого взаимно дополняющего (0-1 или 1-0) сигнала переноса с выходов инверторов 5 и 6 предыдущего разряда, поскольку транзисторы 29 и 30 n-типа до этого момента - закрыты. Закрытый тактовый транзистор 1 n-типа на первом полутакте исключает протекание сквозных токов между шиной питания 34 и шиной земли 47 независимо от значений переменных. Входные сигналы, соответствующие суммируемым переменным в каждом разряде, удерживаются в течение всего второго рабочего полутакта.

После подачи положительного сигнала на тактовый вход 46 сумматора тактовые транзисторы 1 и 2 открываются, а транзисторы 8-11 р-типа запираются. Закрываются также транзисторы n-типа инверторов 5 и 6, что подготавливает формирование сигнала логической 1 на одном из выходов 51 или 52 инверторов 5 и 6, соответствующего значению переноса в следующий разряд. При любом наборе взаимно дополняющих сигналов на входах 39-42 первого каскада в логическом блоке 12 существуют только две проводящие ключевые цепи - одна между первым 35 или вторым 36 выходом логического блока и нулевой шиной 33, и другая - между третьим 37 или четвертым 38 выходами логического блока и нулевой шиной 33. Первая из указанных цепей для конкретного набора значений переменных реализует функцию суммы, а вторая - функцию переноса. Аналогично происходит во всех других разрядах сумматора по мере поступления значимого сигнала на входы 43 и 44, отличного от исходного логического состояния 0-0 на этих входах. Наличие проводящей ключевой цепи при указанном выше наборе сигналов - первый 13, шестой 18 и семнадцатый 29 транзисторы n-типа - при открытом тактовом транзисторе 1 n-типа ведет к разряду узловой емкости, связанной с первым выходом 35 логического блока 12 до уровня логического 0. Появление нулевого сигнала на одном из входов триггера-фиксатора 7 ведет к его переключению, либо подтверждению предыдущего состояния, соответствующего сумме, равной 0. Одновременно в логическом блоке 12 первого разряда благодаря проводящей цепи, состоящей из одиннадцатого 23, двенадцатого 24 и семнадцатого 29 транзисторов n-типа, разряжается узловая емкость, связанная с третьим выходом 37 логического блока 12. На логическом входе 48 первого инвертора 5 формируется сигнал логического 0, который открывает транзистор р-типа этого инвертора и его выход 51 принимает значение логической 1, что свидетельствует о логическом значении переноса в данном разряде, равном 1. Формирование сигнала логической 1 на прямом входе 43 переноса второго разряда приводит (например, при том же наборе переменных - А=1, В=0) к открыванию семнадцатого транзистора 29 n-типа в логическом блоке 12 второго разряда и протеканию тех же процессов, что и в первом разряде. Таким образом, сигнал переноса распространяется волнообразно последовательно с одновременным поразрядным суммированием.

При суммировании в каком-либо разряде одинаковых значений переменных (А-В-1, или А-В-0) результат переноса формируется непосредственно в данном разряде до появления на входах 43 или 44 переноса сигнала логической 1 с выходов 51 или 52 инверторов предыдущего разряда. При наличии на входах 39-42 разряда сигналов, соответствующих переменным A=B=1 на третьем выходе 37 логического блока формируется сигнал логического 0 благодаря открытым одиннадцатому 23 и девятнадцатому 31 транзисторам n-типа. При сигналах соответствующих суммированию переменных А=В=0 открыты пятнадцатый 27 и двадцатый 32 транзисторы n-типа и сигнал логического 0 формируется на четвертом выходе 38 логического блока, далее сигнал логической 1 формируется на выходе 52 второго инвертора данного разряда. Транзисторы n-типа 21-32, реализующие функции переноса, связаны между собой таким образом, что никак не влияют на процесс суммирования в данном разряде, т.к. один из транзисторов n-типа в каждой из пар двенадцатый 24 - девятнадцатый 31 и шестнадцатый 28 - двадцатый 32 всегда закрыт.

Повышенное быстродействие сумматора обусловлено минимальным числом нагрузок в цепях распространения сигнала переноса. Это позволяет реализовать разряд сумматора на транзисторах минимальных технологических размеров, но при этом получить быстродействие, характерное для цепочки простейших инверторов. При этом каждый разряд представляется в виде двух эквивалентных инверторов Причем емкостная нагрузка, переключаемая эквивалентным инвертором соответствует емкости затвора одного МДП транзистора минимальных размеров, что в трое меньше, чем емкостная нагрузка простейшего статического КМДП инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ КАСКАДНЫХ УСТРОЙСТВ НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209508C1 |

| ПАРАФАЗНОЕ КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 2002 |

|

RU2209507C1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| ТАКТИРУЕМЫЙ ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2382490C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| УСТРОЙСТВО СРАВНЕНИЯ НА КМДП ТРАНЗИСТОРАХ | 2003 |

|

RU2236696C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА КМДП ТРАНЗИСТОРАХ | 2007 |

|

RU2355104C1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 2009 |

|

RU2393631C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в КМДП интегральных схемах при реализации арифметических и логических устройств. В устройство введены дополнительный инвертор (3) и связанный с его выходом тактовый транзистор (2) р-типа, включенный между шиной питания (34) и клеммами положительного питания (53) инверторов (5) и (6), которые выполнены тактируемыми с использованием затворов транзисторов р-типа инверторов в качестве их логических входов (48) и (49), подключенных к выходам (37) и (38) логического блока (12), и затворов транзисторов n-типа инверторов - в качестве тактового входа (50), соединенного с выходом дополнительного инвертора (3), а также введены в логический блок (12) каждого разряда сумматора два транзистора (31) и (32) n-типа в совокупности с новыми связями между ключевыми цепями и логическим блоком (12), выполненными на транзисторах n-типа. Технический результат - повышение быстродействия. 1 ил.

Сумматор на КМДП транзисторах, содержащий тактовый транзистор n-типа и в первом разряде - два инвертора, триггер-фиксатор, четыре транзистора р-типа и логический блок, содержащий восемнадцать транзисторов n-типа, из которых соединены последовательно парами первый и второй транзисторы, третий и четвертый, пятый и шестой, седьмой и восьмой, девятый и десятый, одиннадцатый и двенадцатый, тринадцатый и четырнадцатый, пятнадцатый и шестнадцатый, образуя соответствующие ключевые цепи, средние точки первой и четвертой, второй и третьей ключевых цепей попарно объединены, первая и вторая ключевые цепи соединены параллельно и подключены общими стоками первого и третьего транзисторов n-типа к первому выходу логического блока, а общими истоками второго и четвертого транзисторов через семнадцатый транзистор n-типа - к нулевой шине, третья и четвертая ключевые цепи соединены параллельно и подключены общими стоками пятого и седьмого транзисторов к второму выходу логического блока, а общими истоками шестого и восьмого транзисторов n-типа через восемнадцатый транзистор n-типа - к нулевой шине, первый и второй выходы логического блока соединены соответственно через первый и второй транзисторы р-типа с шиной питания и подключены непосредственно к соответствующим входам триггера-фиксатора, выходы которого являются выводами результата суммирования в данном разряде, пятая и шестая ключевые цепи объединенными стоками девятого и одиннадцатого транзисторов n-типа подключены к третьему выходу логического блока, который соединен с логическим входом первого инвертора непосредственно, а через третий транзистор р-типа - с шиной питания, седьмая и восьмая ключевые цепи объединенными стоками тринадцатого и пятнадцатого транзисторов n-типа подключены к четвертому выходу логического блока, который соединен с логическим входом второго инвертора непосредственно, а через четвертый транзистор р-типа - с шиной питания, затворы первого, пятого и одиннадцатого транзисторов n-типа подключены к прямому входу, а затворы третьего, седьмого и пятнадцатого транзисторов n-типа - к дополнительному входу, на которые подаются парафазные сигналы первой переменной разряда, затворы второго, шестого и шестнадцатого транзисторов n-типа подключены к прямому входу, а затворы четвертого, восьмого и двенадцатого транзисторов n-типа - к дополнительному входу, на которые подаются парафазные сигналы второй переменной разряда, затворы семнадцатого и восемнадцатого транзисторов n-типа являются парафазными входами переноса, затворы транзисторов р-типа и затвор тактового транзистора n-типа, который включен между шиной земли и нулевой шиной, подключены к тактовому входу сумматора, выходы первого и второго инверторов подключены к соответствующим входам переноса последующего разряда, отличающийся тем, что содержит дополнительный инвертор и тактовый транзистор р-типа, затвор которого соединен с выходом дополнительного инвертора, вход которого подключен к тактовому входу сумматора, причем все разряды сумматора выполнены идентично с первым разрядом, в логический блок которого введены девятнадцатый и двадцатый транзисторы n-типа первый из которых включен между средней точкой шестой ключевой цепи и нулевой шиной, а второй - между средней точкой восьмой ключевой цепи и нулевой шиной, истоки десятого и двенадцатого транзисторов n-типа подключены к общей точке второго и семнадцатого транзисторов n-типа, а истоки четырнадцатого и шестнадцатого транзисторов n-типа соединены с общей точкой шестого и восемнадцатого транзисторов n-типа, затворы тринадцатого и девятого транзисторов n-типа подключены соответственно к прямому и дополнительному входам первой переменной разряда, затворы десятого и девятнадцатого транзисторов n-типа подключены к прямому входу, а затворы четырнадцатого и двадцатого транзисторов n-типа - к дополнительному входу второй переменной разряда, первый и второй инверторы выполнены тактируемыми, причем затвор транзистора р-типа каждого инвертора является его логическим входом, а затвор транзистора n-типа - его тактовым входом, который подключен к выходу дополнительного инвертора, клеммы положительного питания обоих инверторов соединены с шиной питания через тактовый транзистор р-типа.

| КАСКАДНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО НА КМДП ТРАНЗИСТОРАХ | 1998 |

|

RU2132591C1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| RU 94007826 А1, 27.02.1996 | |||

| US 5491653 А, 13.02.1996 | |||

| МЕХАНИЗМ КАЛЕНДАРЯ К НАСТОЛЬНЫМ И НАСТЕННЫМ ЧАСАМ | 0 |

|

SU332415A1 |

Авторы

Даты

2002-07-20—Публикация

2001-02-19—Подача