со

о

о со

4

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении матричных коммутационных структур.

Цель изобретения - расширение функциональных возможностей коммутатора за счет реализации произвольного вида коммутаций и программируемых величин задержек по четырем направлениям передачи информации.

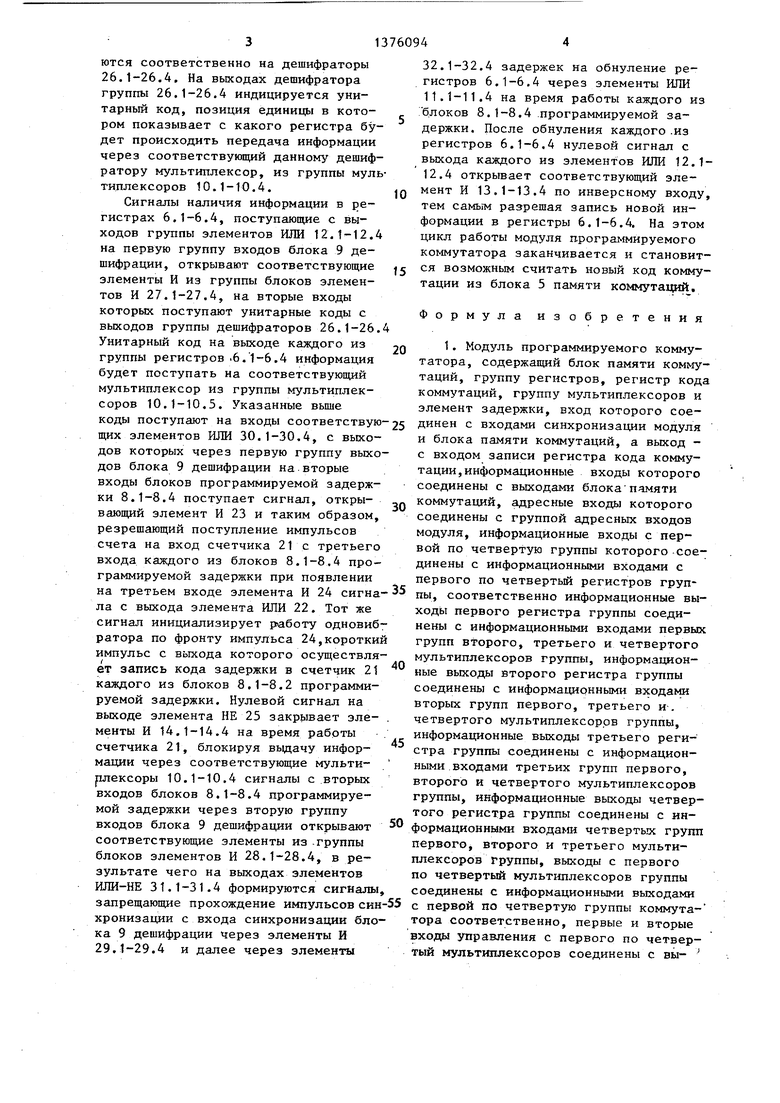

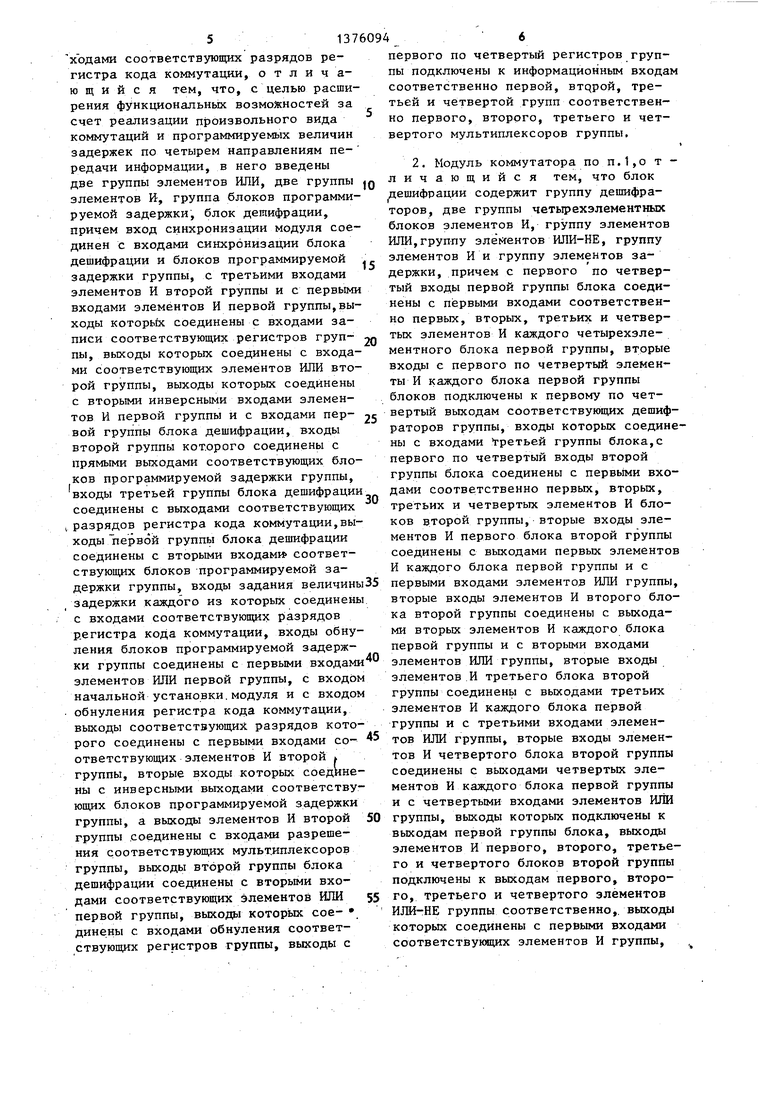

На фиг. 1 показан пример реализации матричной коммутационной структуры на основе предлагаемого коммута

60942

Перед началом работы на вход 16 обнуления подается сигнал, приводящий модуль программируемого коммутатора в исходное Состояние. Далее на группу адресных входов 18 подается адрес, а на вход 19 синхронизации сигнал,по которому происходит считывание кода коммутации из блока 5 памяти коммутаций. Тот же сигнал с входа 19 синхронизации, пройдя через элемент 15 задержки, определяющий время считывания кода коммутации из блока 5 памяти коммутаций, осуществляет запись кода

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка однородной вычислительной среды | 1986 |

|

SU1386987A1 |

| Модуль матричного коммутатора | 1985 |

|

SU1280596A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1319029A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1354192A1 |

| Адаптивный модуль микропрограммного устройства управления | 1984 |

|

SU1273926A1 |

| МОДУЛЬ КОММУНИКАЦИОННОЙ СЕТИ, ПРЕДНАЗНАЧЕННЫЙ ДЛЯ ПЕРЕДАЧИ СООБЩЕНИЙ, ОБМЕНА СООБЩЕНИЯМИ И ОРГАНИЗАЦИИ ВЕЩАТЕЛЬНЫХ РЕЖИМОВ ОБМЕНА СООБЩЕНИЯМИ | 2000 |

|

RU2178584C1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1280627A1 |

| Процессорный модуль | 1985 |

|

SU1343421A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении матричных коммутаторов информации, а также в системах коммутации данных многопроцессорных вычислительных структур. Целью изобретения является расширение функциональных возможностей модуля программируемого коммутатора, а именно реализация произвольных коммутаций типа с любого входа - на любой выход при условии несмешивания информации с разных входов. Кроме того, реализована возможность создания программируемой задержки на каждом маршруте прохождения информации. Поставленная цель достигнута за счет дополнительного введения двух групп элементов ШШ, двух групп элементов И, группы блоков программируемой задержки и блока дешифрации; 1 з.п. ф-лы, 4 ил. i СЛ

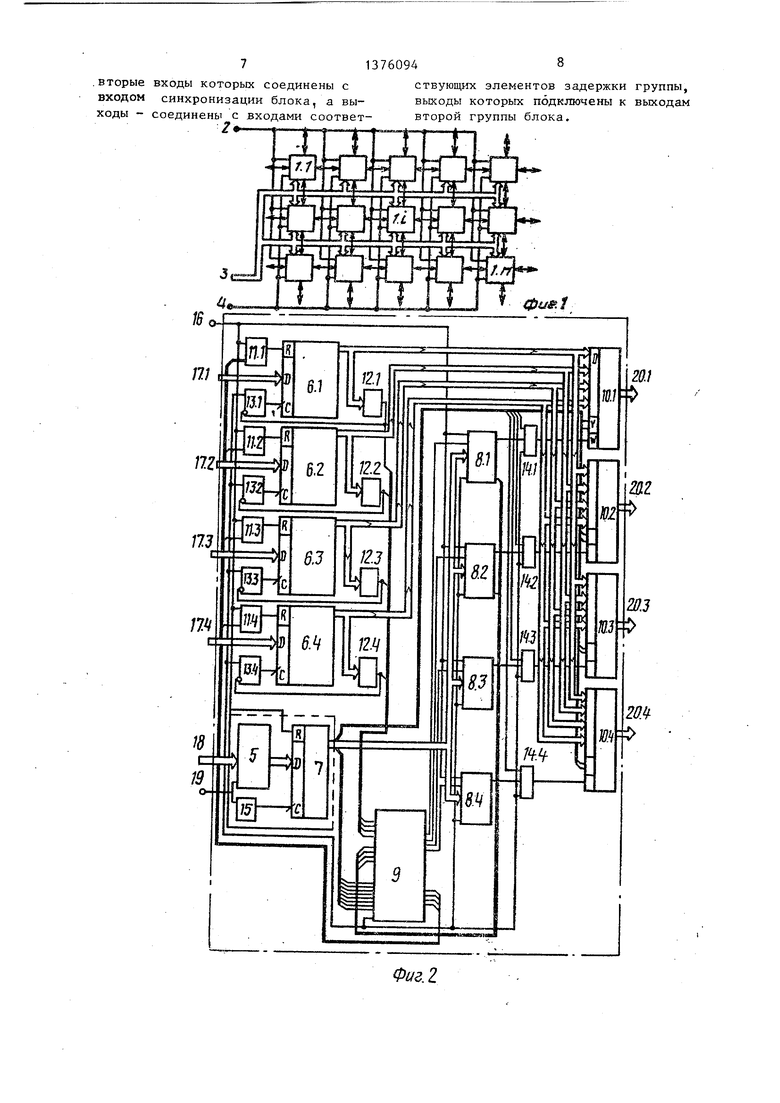

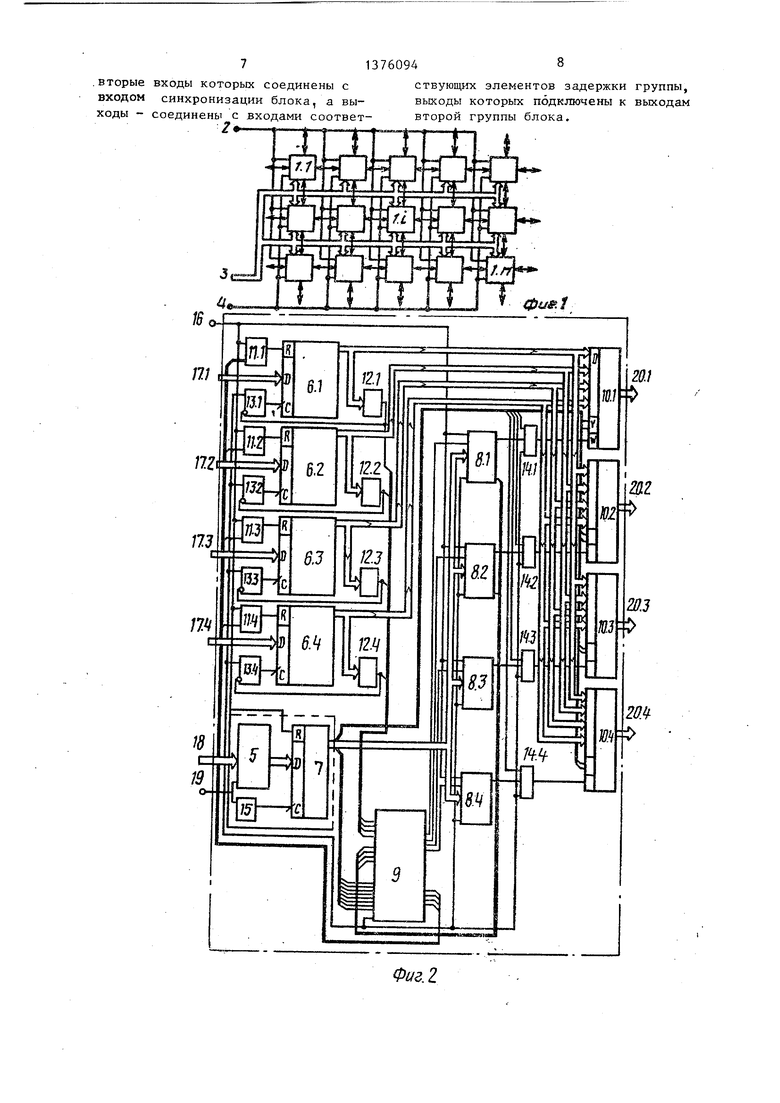

тора; на фиг. 2 - функциональная коммутации в регистр 7 кода коммутации. Информационное слово на входах регистра 7 кода коммутации содержит четыре кода задержек по соответствующим направлениям для группы блоков программируемой задержки 8.1-8.4, четыре кода мультиплексирования, поступающие на управляющие входы группы мультиплексоров 10.1-10.4, четыре разряда разрешения мультиплексирования, открывающие соответствующий элемент И из группы элементов И 17.1- 17.4.и непосредственно код коммутации определяющий взаимосвязь между группой информационных входов 17.1-17.4 зп и группой информационных выходов

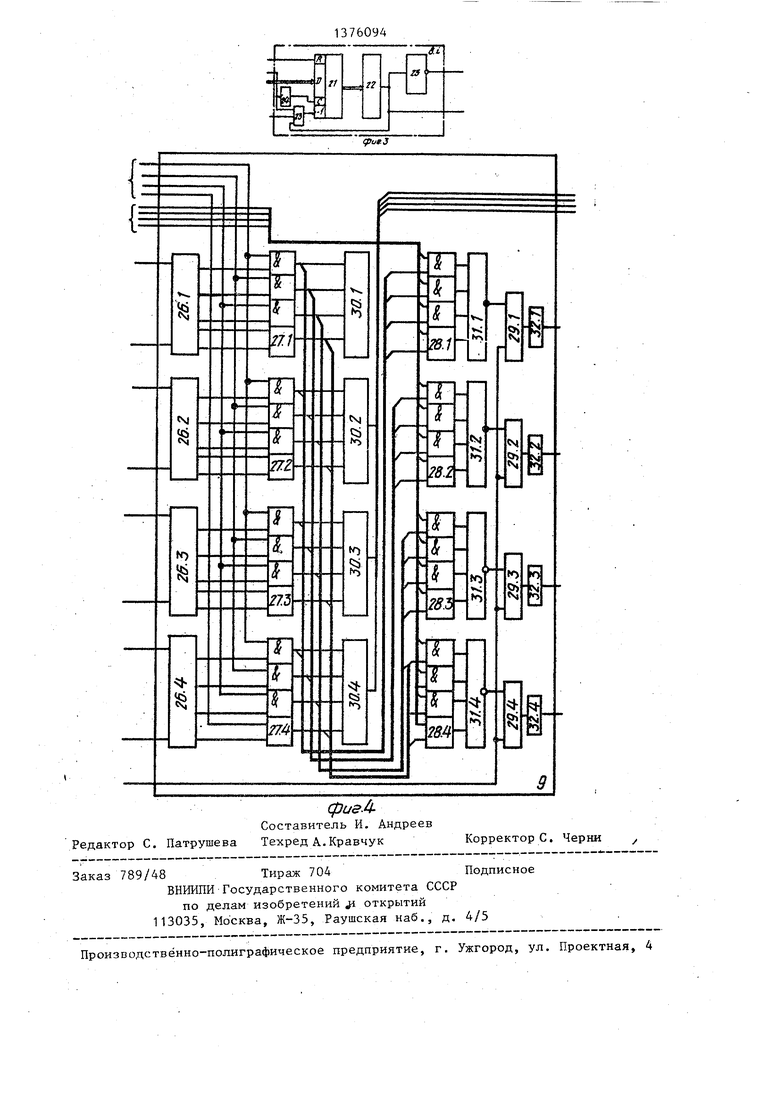

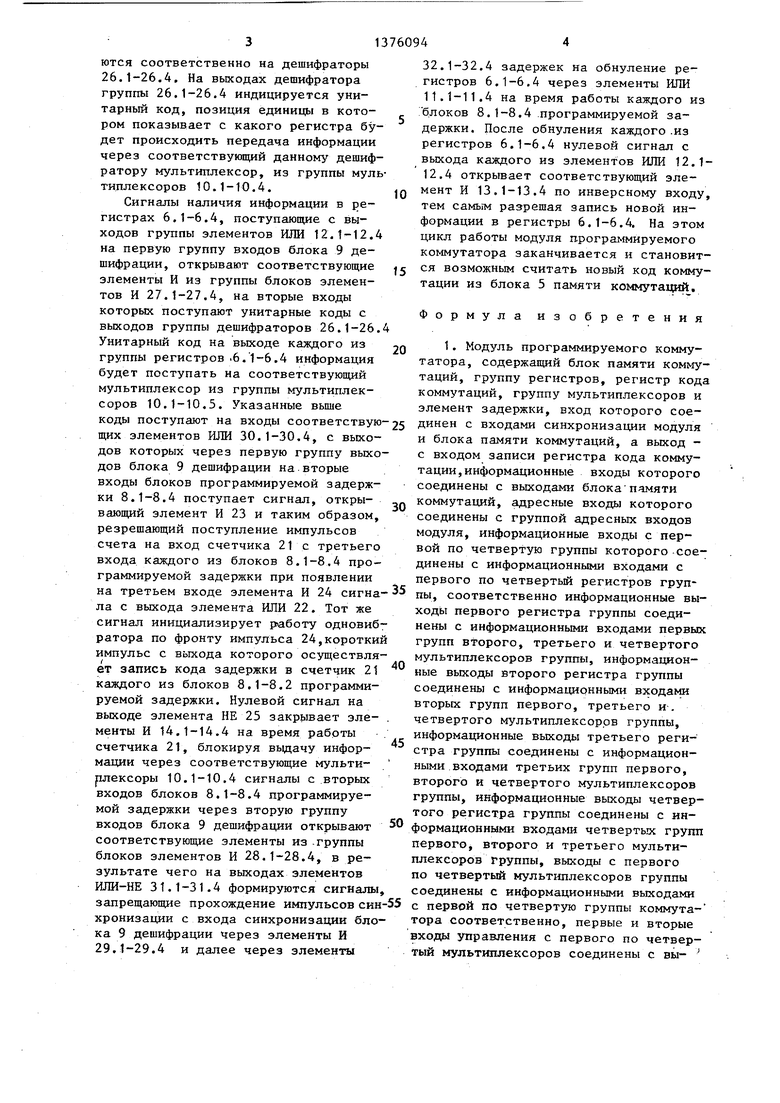

ма модуля программируемого коммутатора; на фиг. 3 - функциональная схема блока программируемой задержки; на фиг. 4 - функциональная схема блока дешифрации.

Матричная коммутационная структура (фиг. 1) состоит из группы модулей программируемого коммутатора 1.1-l.n и имеет вход 2 обнуления, группу адресных входов 3 и вход 4 синхрониза- ции.

Модуль программируемого коммутатора содержит блок 5 памяти коммутаций группу 6.1-6.4 регистров, регистр 7 кода коммутации, группу блоков 8.1- 8.4 программируемой задержки, блок 9 дешифрации, группу мультиплексоров 10.1-10.4, первую группу элементов ИЛИ 11.1-11.4, вторую группу элементов ИЛИ 12.1-11.4, вторую группу элементов ИЛИ 12.1-12.4, первую 13.1- 13.4 и вторую 14.1-14.4 группы элементов И, элемент 15 задержки и имеет вход 16 обнуления, группу информационных входов 17.1-17.4, группу адресных входов 18, вход 19 синхронизации и группу информационных выходов 20.1-20.4.

Блок 8 программируемой задержки содержит вычитающий счетчик 21с занесением, элемент ИЛИ 22, элемент И23,одноБибратор по фронту импульса 24 и элемент НЕ 25.

Блок дешифрации 9 содержит группу дешифраторов 26.1-26.4 первую 27.1- 27.4 и вторую 28.1-28.4 группы четы- рехэлементных блоков элементов И, группу элементов И 29.1-29.4, группу элементов ИЛИ 30.1-30.4, группу элементов ИЛИ-НЕ 31.1-31.4, группу элементов ИЛИ-НЕ 31.1-31.4, группу элементов задержки 32.1-32,4.

Модуль программируемого коммутатора работает следующим образом.

коммутации в регистр 7 кода коммута

ции. Информационное слово на входах регистра 7 кода коммутации содержит четыре кода задержек по соответствующим направлениям для группы блоков программируемой задержки 8.1-8.4, четыре кода мультиплексирования, поступающие на управляющие входы группы мультиплексоров 10.1-10.4, четыре разряда разрешения мультиплексирования, открывающие соответствующий элемент И из группы элементов И 17.1- 17.4.и непосредственно код коммутации, определяющий взаимосвязь между группой информационных входов 17.1-17.4 и группой информационных выходов

Для подачи информации на входы 17.1-17.4 модуля программируемого коммутатора регистры 6.1-6.4 находятся в нулевом состоянии, вследствие чего на выходе элементов ИЛИ 12.1- 12.4 индицируются нулевые сигналы, которые, поступая на вторые инверсные входы элементов И 13.1-13.4, разрешают прохождение синхроимпульсов с входа 19 на синхровходы записи регистров 6.1-6.4. При появлении информации на одном или нескольких входах 17.1-17.4 происходит ее запись в соответствующие регистры 6.. 1-6.4, что приводит к появлению единичного сигнала на выходах определенных элементов ИЛИ 12.1-12.4, который запрещает синхронизацию записи информации в соответствующие регистры 6.1-6.4. Выходы элементов ИЛИ 12.1-12.4 соединены соответственно с первым, вторым, третьим и четвертым входами блока 9 дешифрации, на деишфраторы 26.1-26.4 которого по его девятому-шестнадца- Тому входам подается информация о кодах мультиплексирования с выхода регистра 7. Эти пары разрядов пода

ются соответственно на дешифраторы 26.1-26,4, На выходах дешифратора группы 26.1-26.4 индицируется унитарный код, позиция единицы в котором показывает с какого регистра будет происходить передача информации через соответствующий данному дешифратору мультиплексор, из группы мультиплексоров 10.1-10.4,

Сигналы наличия информации в регистрах 6.1-6,4, поступающие с выходов группы элементов ИЛИ 12.1-12,4 на первую группу входов блока 9 дешифрации, открывают соответствующие элементы И из группы блоков элементов И 27.1-27.4, на вторые входы которых поступают унитарные коды с выходов группы дешифраторов 26.1-26.4 Унитарный код на выходе каждого из группы регистров .6.1-6,4 информация будет поступать на соответствующий мультиплексор из группы мультиплексоров 10.1-10.5. Указанные вьш1е коды поступают на входы соответствующих элементов ИЛИ 30.1-30.4, с выходов которых через первую группу выходов блока 9 дешифрации на вторые входы блоков программируемой задержки 8,1-8.4 поступает сигнал, откры- вающий элемент И 23 и таким образом, резрешающий поступление импульсов счета на вход счетчика 21 с третьего входа каждого из блоков 8.1-8.4 программируемой задержки при появлении на третьем входе элемента И 24 сигна- ла с выхода элемента ИЛИ 22. Тот же сигнал инициализирует работу одновиб- ратора по фронту импульса 24,короткий импульс с выхода которого осуществляет запись кода задержки в счетчик 21 каждого из блоков 8.1-8.2 программируемой задержки. Нулевой сигнал на выходе элемента НЕ 25 закрывает эле- менты И 14,1-14.4 на время работы счетчика 21, блокируя выдачу информации через соответствующие мульти- рлексоры 10,1-10.4 сигналы с вторых входов блоков 8.1-8,4 программируемой задержки через вторую группу входов блока 9 дешифрации открывают соответствующие элементы из -группы блоков элементов И 28.1-28,4, в результате чего на выходах элементов ИЛИ-НЕ 31.1-31.4 формируются сигналы запрещающие прохождение импульсов син хронизации с входа синхронизации блока 9 дешифрации через элементы И 29.1-29.4 и далее через элементы

0 5

5

32,1-32.4 задержек на обнуление регистров 6.1-6.4 через элементы ИЛИ 11.1-11.4 на время работы каждого из блоков 8. 1-8.4 .программируемой задержки. После обнуления каждого .из регистров 6,1-6.4 нулевой сигнал с выхода каждого из элементов ИЛИ 12,1- 12.4 открывает соответствующий элемент И 13.1-13.4 по инверсному входу, тем самым разрешая запись новой информации в регистры 6.1-6.4. На этом цикл работы модуля программируемого коммутатора заканчивается и становится возможным считать новый код коммутации из блока 5 памяти коммутаций.

Формула изобретения

ходами соответствующих разрядов регистра кода коммутации, отличающийся тем, что, с целью расширения функциональных возможностей за счет реализации произвольного вида коммутаций и программируемых величин задержек по четырем направлениям передачи информации, в него введены две группы элементов ИЛИ, две группы элементов И, группа блоков программируемой задержки, блок дешифрации, причем вход синхронизации модуля соединен с входами синхронизации блока дешифрации и блоков программируемой задержки группы, с третьими входами элементов И второй группы и с первыми входами элементов И первой группы,выходы KOTopbfx соединены с входами записи соответствующих регистров груп- пы, выходы которых соединены с входами соответствующих элементов ИЛИ второй группы, выходы которых соединены с вторыми инверсными входами элемен

тов И первой группы и с входами пер- 25 вертый выходам соответствующих дешифвой группы блока дешифрации, входы второй группы которого соединены с прямыми выходами соответствующих блоков программируемой задержки группы, входы третьей группы блока дешифрации соединены с выходами соответствующих разрядов регистра кода коммутации,выходы первой группы блока дешифрации соединены с вторыми входами- соответствующих блоков программируемой за30

раторов группы, входы которых соединены с входами третьей группы блока,с первого по четвертый входы второй группы блока соединены с первь1ми входами соответственно первых, вторых, третьих и четвертых элементов И блоков второй группы, вторые входы элементов И первого блока второй группы соединены с выходами первых элементов И каждого блока первой группы и с

держки группы, входы задания величиныЗЗ первыми входами элементов ИЛИ группы.

40

задержки каждого из которых соединены с входами соответствующих разрядов регистра кода коммутации, входы обнуления блоков программируемой задержки группы соединены с первыми входами элементов ИЛИ первой группы, с входом начальной установки.модуля и с входом обнуления регистра кода коммутации, выходы соответствующие разрядов которого соединены с первыми входами со- ответствующих элементов И второй группы, вторые входы которых соединены с инверсными выходами соответствующих блоков программируемой задержки группы, а выходы элементов И второй 50 группы соединены с входами разрешения соответствующих мультиплексоров группы, выходы второй группы блока дешифрации соединены с вторыми входами соответствующих элементов ШШ 55 первой группы, выходы которых сое- динены с входами обнуления соответствующих регистров группы, выходы с

O

п

5

первого по четвертый регистров группы подключены к информационным входам соответственно первой, втцрой, третьей и четвертой групп соответственно первого, второго, третьего и четвертого мультиплексоров группы,

раторов группы, входы которых соединены с входами третьей группы блока,с первого по четвертый входы второй группы блока соединены с первь1ми входами соответственно первых, вторых, третьих и четвертых элементов И блоков второй группы, вторые входы элементов И первого блока второй группы соединены с выходами первых элементов И каждого блока первой группы и с

0

0 5

вторые входы элементов И второго блока второй группы соединены с выходами вторых элементов И каждого блока первой группы и с вторыми входами элементов ИЛИ группы, вторые входы элементов И третьего блока второй группы соединены с выходами третьих элементов И каждого блока первой группы и с третьими входами элементов ИЛИ группы, вторые входы элементов И четвертого блока второй группы соединены с выходами четвертых элементов И каждого блока первой группы и с четвертыми входами элементов ИЛИ группы, выходы которых подключены к выходам первой группы блока, выходы элементов И первого, второго, третьего и четвертого блоков второй группы подключены к выходам первого, второго, третьего и четвертого элементов ИЖ-НЕ группы соответственно,, выходы которых соединены с первыми входами соответствующих элементов И группы.

.вторые входы которых соединены с входом синхронизации блока, а выходы - соединены с входами соответ

2

1д

с

ю

ствующих элементов задержки группы, выходы которых подключены к выходам второй группы блока.

r3Jr

фит1

Фиг.г

| УСТРОЙСТВО ДЛЯ ИГРЫ ШАРАМИ ТИПА БИЛЛИАРДА | 1930 |

|

SU21778A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Модуль матричного коммутатора | 1985 |

|

SU1280596A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-23—Публикация

1986-05-27—Подача