W ГЩ

тг

W

со

к

0

сл

10 и 11, первую, вторую и третью схемы сравнения 12, 13 и 14, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, первый и второй элементы ИЛИ-НЕ 16 и 17, первый,второй, третий, четвертьй, пятый и шестой элементы И 18, 19, 20, 21, 22 и 23,, первый и второй элементы И-НЕ 24 и 25, первый, второй и третий элементы НЕ 26, 27 и 28, одновибра- тор 29, триггер 30 запоминающий блок 31, входы 32 и 33 сигнала-делимого и сигнала-делителя источник 34 первого опорного напряжения, шину 35 нулевого потенциала, источник 36 второго опор76105

ного напряжения,вход 37 запуска устройства, выход 38 устройства,сигнальный выход 39 окончания операции деления.Работа устройства основана на сравнении сформированного первого экспоненциально убывающего напряжения с уровнями входных сигналов и опорного напряжения и запоминании мгновенного значения величины второго экспоненциального убывающего напряжения в моменты сравнения первого экспоненциального убывающего напряжения с входными сигналами и опорным напряжением. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1983 |

|

SU1111179A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| Устройство для измерения отношения двух напряжений | 1983 |

|

SU1147991A1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Логарифмический преобразователь амплитуды импульсов | 1980 |

|

SU903906A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU855737A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| Узловой элемент сеточной модели для решения задач тепломассопереноса | 1988 |

|

SU1562942A1 |

| Интегратор | 1984 |

|

SU1161963A1 |

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности и быстродействия.Устройство для деления двух напряжений содержит первый, второй,третий, четвертый и пятый ключи 1,2,3,4 и 5, первый, второй, третий и четвертый масштабные резисторы 6,7,8 и 9, первый и второй накопительные конденсаторы

1

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения - повьщ1ение точности и быстродействия.

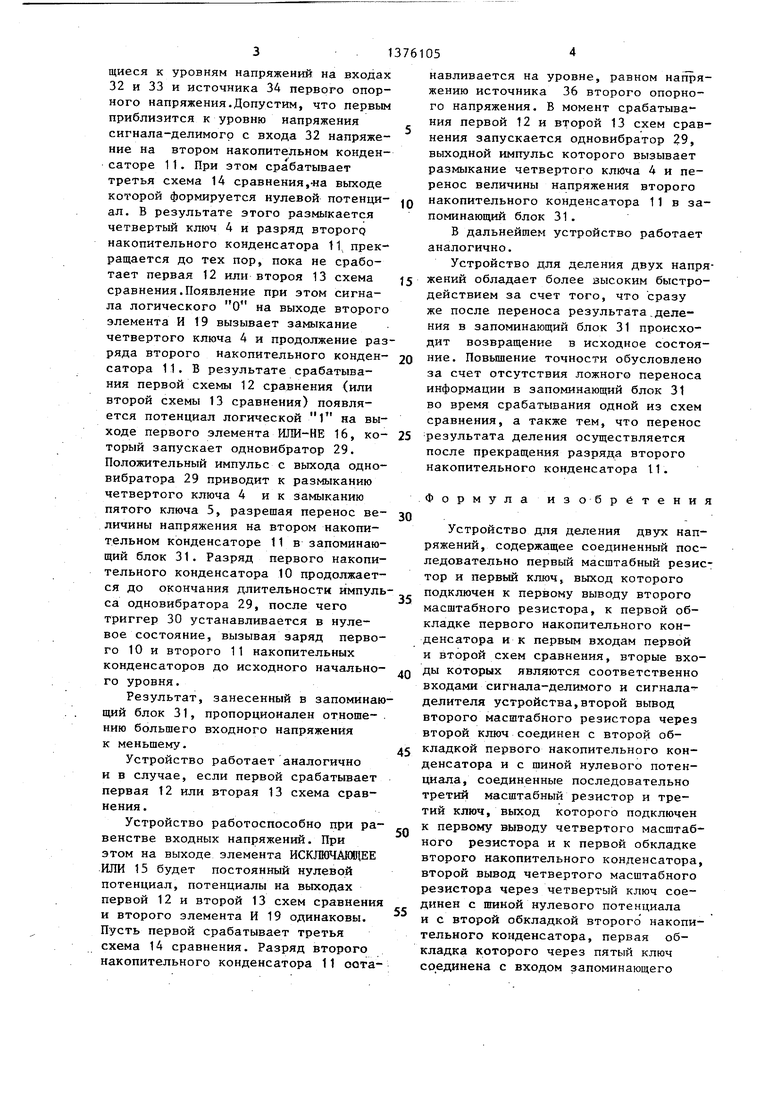

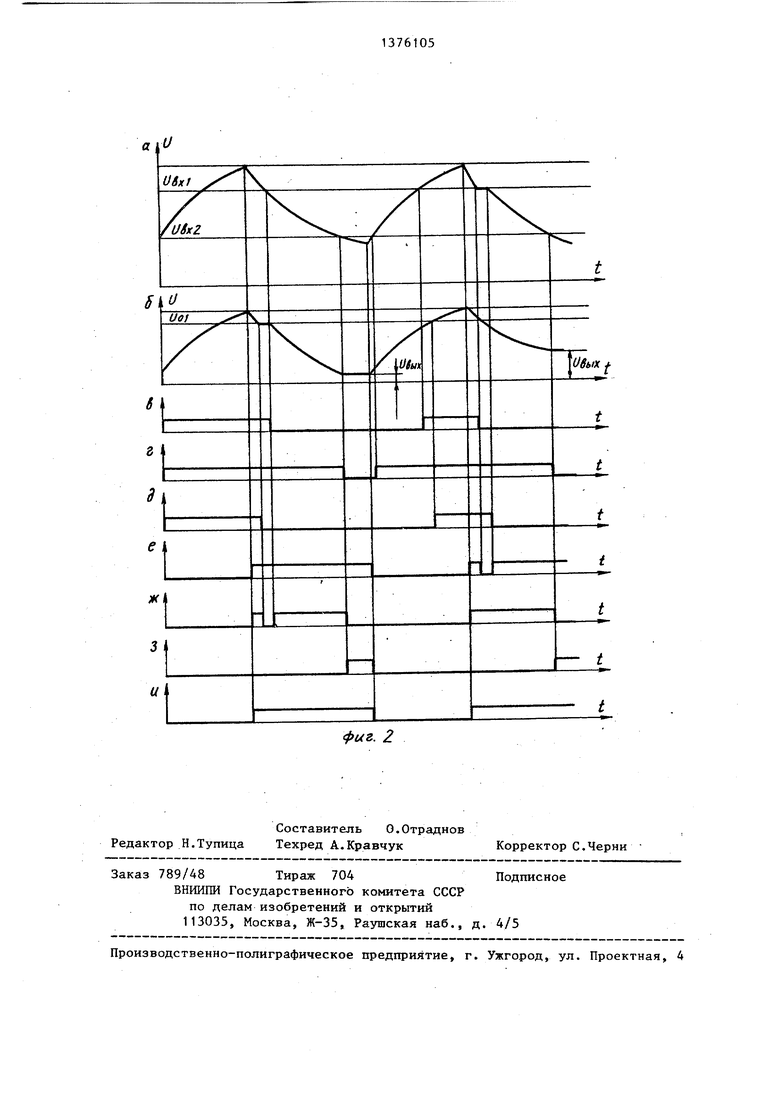

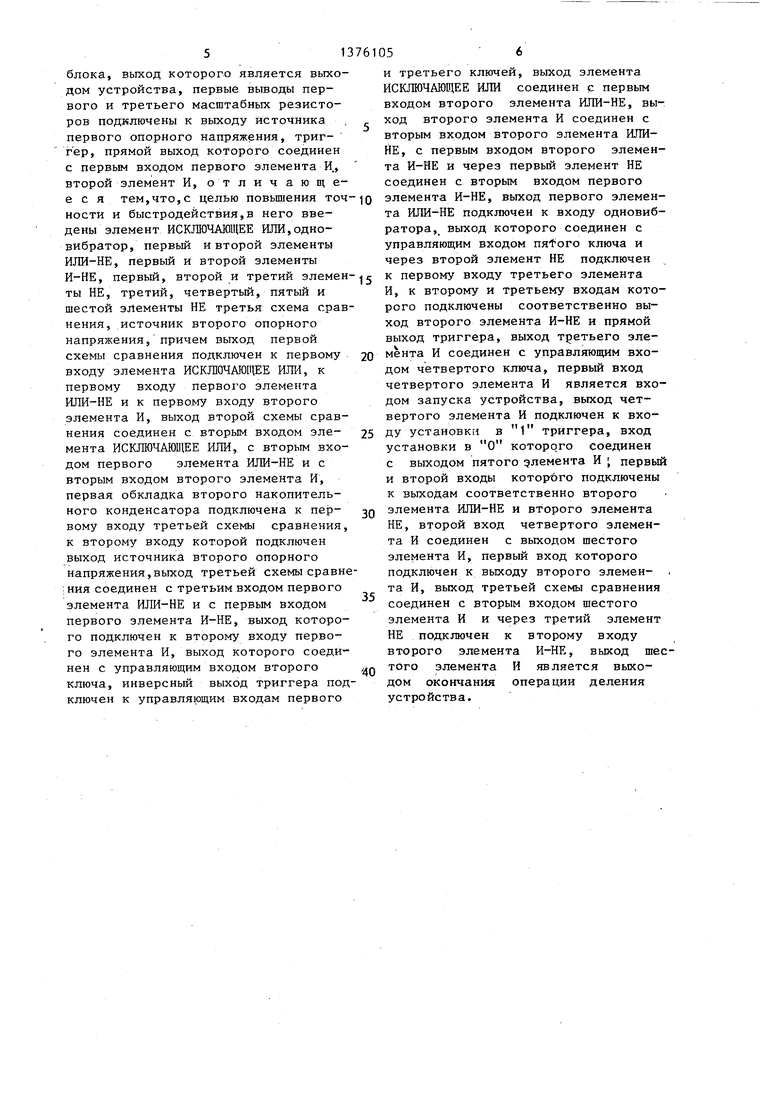

На фиг. 1 изображена функциональная схема устройства для деления двух напряжений;на фиг. 2 - временные диаграммы сигналов. ,,

Устройство содержит первый 1, второй 2,третий 3,четвертый 4 и пятый 5 ключи,первый 6,второй 7,третий 8 и четвертый 9 масштабные резисторы,первый 10 и второй 1i накопительные конденсаторы, первую 12, вторую 13 и третью 14 схемьг сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, первый 16 и второй 17 элементы ИЛИ-НЕ, первый 18, второй 19,- третий 20, четвертый 21, пятый 22 и шестой 23 элементы И,первый 24 и второй 25 элементы И-НЕ, первый 26,второй 27 и третий 28 элементы НЕ, одновибратор 29, триггер 30, запоминающий блок 31, входы 32 и 33 сигнала-делимого и сигнала- делителя устройства,источник 34 первого опорного напряжения, шину 35 нулевого потенциала,источник 36 второго опорного напряжения, вход 37 запуска устройства, выход 38 устройства, сигнальный выход 39 окончания операции деления.

На фиг. 2 приведены диаграммы напряжений: а - два цикла экспоненциально убывающего напряжения на

0

5

0

5

0

5

первом накопительном конденсаторе 10; б - на втором накопительном конденсаторе 11; в - на входе первой схемы 12 сравнения; г-на выходе второй схемы 13 сравнения; д - на выходе третьей схемы 14 сравнения; е - на управляющем входе второго ключа 2;ж - на управляющем входе четвертого ключа 4;з - на выходе од- новибратора - на выходе триггера 30.

Устройство для деления двух напряжений работает следующим образом.

В исходном состоянии триггер 30 находится в нулевом состоянии.Второй 2 и четвертый 4 ключи разомкнуты, первый 1 и третий 3 ключи замкнуты. На первом 10 и втором 11 накопительных конденсаторах присутствуют началь- ные напряжения,превышающие максимально возможные значения напряжений с входов 32 и 33 и источника 34 первого опорного напряжения.На выходы первой 12, второй 13 и третьей 14 схем сравнения установлен положительный потенциал напряжения.

Начало цикла задается путем подачи импульса с входа 37 запуска.При этом триггер 30 устанавливается в состояние 1, что приводит к размыканию первого 1 и третьего 3 ключей и замыканию второго 2 и четвертого 4 ключей.На первом 10 и втором 1 Т накопительных конденсаторах на- , чинают формироваться экспоненциально убывающие напряжения, приближающиеся к уровням напряжений на входах 32 и 33 и источника 34 первого опорного напряжения.Допустим, что первым приблизится к уровню напряжения сигнала-делимого с входа 32 напряжение на втором накопительном конденсаторе 11. При этом срабатывает третья схема 14 сравнения,-на выходе которой формируется нулевой потенциал. В результате этого размыкается четвертый ключ 4 и разряд второго накопительного конденсатора 11 прекращается до тех пор, пока не сработает первая 12 или второя 13 схема сравнения.Появление при этом сигнала логического О на выходе второго элемента И 19 вызывает замыкание четвертого ключа 4 и продолжение разряда второго накопительного конденсатора 11. В результате срабатывания первой схемы 12 сравнения (или второй схемы 13 сравнения) появляется потенциал логической 1 на выходе первого элемента ИЛИ-НЕ 16, который запускает одновибратор 29. Положительный импульс с вьтхода одно- вибратора 29 приводит к размыканию четвертого ключа 4 и к замыканию пятого ключа 5, разрешая перенос величины напряжения на втором накопительном конденсаторе 11 в запоминающий блок 31. Разряд первого накопительного конденсатора 10 продолжается до окончания длительности импульса одновибратора 29, после чего триггер 30 устанавливается в нулевое состояние, вызывая заряд первого 10 и второго 11 накопительных конденсаторов до исходного начального уровня.

Результат, занесенный в запоминающий блок 31, пропорционален отноше- нию большего входного напряжения к меньшему.

Устройство работает аналогично и в случае, если первой срабатывает первая 12 или вторая 13 схема сравнения.

Устройство работоспособно при равенстве входных напряжений. При этом на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 будет постоянный нулевой потенциал, потенциалы на выходах первой 12 и второй 13 схем сравнения и второго элемента И 19 одинаковы. Пусть первой срабатывает третья схема 14 сравнения. Разряд второго накопительного конденсатора 11 оота

5

0

5

0

5

0

5

0

5

навливается на уровне, равном напряжению источника 36 второго опорного напряжения. В момент срабатывания первой 12 и второй 13 схем сравнения запускается одновибратор 29, выходной импульс которого вызывает размыкание четвертого ключа 4 и перенос величины напряжения второго накопительного конденсатора 11 в запоминающий блок 31.

В дальнейшем устройство работает аналогично.

Устройство для деления двух напряжений обладает более высоким быстродействием за счет того, что сразу же после переноса результата.деления в запоминающий блок 31 происходит возвращение в исходное состояние. Повьшение точности обусловлено за счет отсутствия ложного переноса информации в запоминающий блок 31 во время срабатывания одной из схем сравнения, а также тем, что перенос результата деления осуществляется после прекращения разряда второго накопительного конденсатора 11.

Формула изобретения

Устройство для деления двух напряжений, содержащее соединенный последовательно первый масштабный резистор и первый ключ, выход которого подключен к первому выводу второго масштабного резистора, к первой обкладке первого накопительного конденсатора и к первым входам первой и второй схем сравнения, вторые входы которых являются соответственно входами сигнала-делимого и сигнала- делителя устройства,второй вывод второго масштабного резистора через второй ключ соединен с второй обкладкой первого накопительного конденсатора и с шиной нулевого потенциала, соединенные последовательно третий масштабный резистор и третий ключ, выход которого подключен к первому выводу четвертого масштабного резистора и к первой обкладке второго накопительного конденсатора, второй вывод четвертого масштабного резистора через четвертый ключ соединен с шиной нулевого потенциала и с второй обкладкой второго накопительного конденсатора, первая обкладка которого через пятый ключ соединена с входом запоминающего

блока, выход которого является выходом устройства, первые выводы первого и третьего масштабных резисторов подключены к выходу источника первого опорного напряжения, триггер, прямой выход которого соединен с первым входом первого элемента И., второй элемент И, отличающееся тем,что,с целью повышения точ ности и быстродействия,в него введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,одно- вибратор, первый и второй элементы ИЛИ-НЕ, первый и второй элементы И-НЕ, первый, второй и третий элемен ты НЕ, третий, четвертый, пятый и шестой элементы НЕ третья схема сравнения, источник второго опорного напряжения, причем выход первой схемы сравнения подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, к первому входу первого элемента ИЛИ-НЕ и к первому входу второго элемента И, выход второй схемы сравнения соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с вторым входом первого элемента ИЛИ-НЕ и с вторым входом второго элемента И, первая обкладка второго накопительного конденсатора подключена к первому входу третьей схемы сравнения, к второму входу которой подключен выход источника второго опорного напряжения,выход третьей схемы сравн ;ния соединен с третьим входом первого элемента ИЛИ-НЕ и с первым входом первого элемента И-НЕ, выход которого подключен к второму входу первого элемента И, выход которого соеди нен с управляющим входом второго ключа, инверсный выход триггера подключен к управляющим входам первого

0

5

0

5

0

и третьего ключей, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с первым входом второго элемента ИЛИ-НЕ, выход второго элемента И соединен с вторым входом второго элемента ИЛИ- НЕ, с первым входом второго элемента И-НЕ и через первый элемент НЕ соединен с вторым входом первого элемента И-НЕ, выход первого элемента ИЛИ-НЕ подключен к входу одновиб- ратора, выход которого соединен с управляющим входом пятого ключа и через второй элемент НЕ подключен к первому входу третьего элемента И, к второму и третьему входам которого подключены соответственно выход второго элемента И-НЕ и прямой выход триггера, выход третьего элемента И соединен с управляющим входом четвертого ключа, первый вход четвертого элемента И является входом запуска устройства, выход четвертого элемента И подключен к входу установк: в 1 триггера, вход установки в О которого соединен с выходом пятого элемента И ; первый и второй входы которого подключены к выходам соответственно второго элемента ИЛИ-НЕ и второго элемента НЕ, второй вход четвертого элемента И соединен с выходом шестого элемента И, первый вход которого подключен к выходу второго элемен- . та И, выход третьей схемы сравнения соединен с вторым входом шестого элемента И и через третий элемент НЕ подключен к второму входу второго элемента И-НЕ, выход шестого элемента И является выходом окончания операции деления устройства.

USxt

т

ц

фиг. Z

Шык

ивых

t

t t

-L t

| Устройство для деления напряжений | 1980 |

|

SU894725A1 |

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления напряжений | 1982 |

|

SU1057962A1 |

Авторы

Даты

1988-02-23—Публикация

1986-06-18—Подача