модулю два, к второму входу.которого сумматора по модулю два подключен к подключен выход третьего коммутатора второму входу первого сумматора по мообъединения ветвей, а выход третьего дулю два.

1035819

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство имитостойкого кодирования и декодирования информации избыточными систематическими кодами | 2016 |

|

RU2634201C1 |

| Пороговый декодер сверточного кода | 1982 |

|

SU1078654A1 |

| Сверточный кодек с алгоритмом порогового декодирования | 1985 |

|

SU1327296A1 |

| Декодер сверточного кода | 1986 |

|

SU1388998A1 |

| Пороговый декодер сверточного кода | 1986 |

|

SU1443180A1 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| Пороговый декодер сверточного кода | 1984 |

|

SU1185629A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| СПОСОБ СИНДРОМНОГО ДЕКОДИРОВАНИЯ ДЛЯ СВЕРТОЧНЫХ КОДОВ | 2004 |

|

RU2282307C2 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ СВЕРТОЧНЫМИ КОДАМИ, содержащее на передающей стороне первый канал кодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректЪра ошибок, к второй группе входов которого подключены выходы анализатора синдромной последовательности, к входу которого пбдключен выход первого сумматора по модулю два, при этом выходы корректора ошибок подключены к .входам коммута тора объединения ветвей, отличающееся тем, что, с целью повышения помехоустойчивости передачи двоичной информации, на передающей стороне введены преобразователь входной информации, второй канал кодирования и сумматор по модулю два, при этом выходы преобразователя входной информации подключены к входам коммутаторов разделения ветвей первого и второго каналов кодирования, причем выход кодера второго канала кодирования подключен к соответствующему входу коммутатора объединения ветвей второго канала кодирования, выход которого подключен к первому входу сумматора по модулю два, к второкГу входу которого подключен выход кодера первого канала кодирования, а выход сумматора по модулю два подкш)чен к соответствующему входу коммутатора объединения ветвей первого канала кодирования, а на приемной стороне введены второй канал декодирования и преобразователь выходной информации, к входам которого подключены выходы коммутаторов объединения.ветвей первого и второго каналов декодирования, а также второй и третий сумматоры по модулю два, первый и второй буферные накопители, третий кодер и третий коммутатор объединения ветвей при этом выход кодера первого канала декодиро(Л вания подключен через первый буферный накопитель к первому входу первого сумматора по модулю два и через вто рой сумматор по модулю два - к входу коммутатора разделения ветвей второго канала декодирования, выход кодера второго канала декодирования подключен к первому входу первого суммато сд ра по модулю два второго канала декодирования, а к второму входу, первого 00 сумматора по модулю два второго канала декодирования подключен соответствуюсо щий выход коммутатора разделения-ветвей второго канала декодирования, выходы корректора ошибок второго канала декодирования подключены к входам третьего коммутатора объединения ветвей непосредственно и через третий кодер, при этом соответствующий выход коммутатора разделения ветвей первого канала декодирования подключен к втог рому входу сумматора по модулю два и через второй буферный накопитель - к первому входу третьего сумматора по

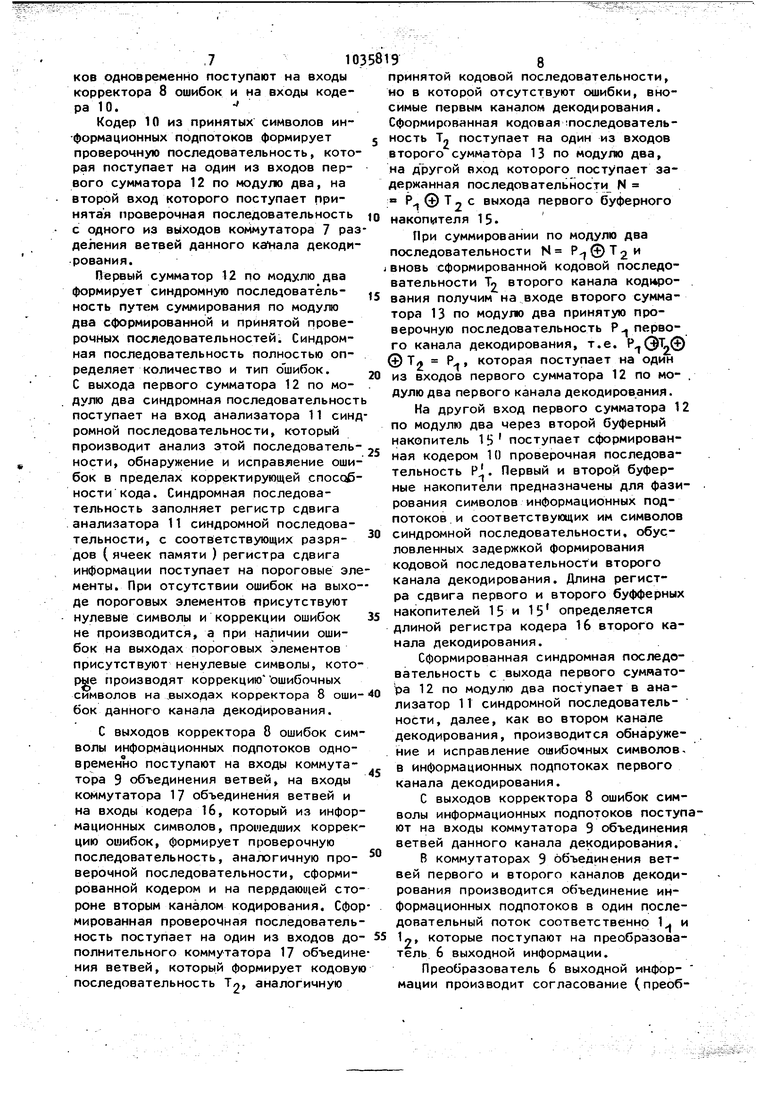

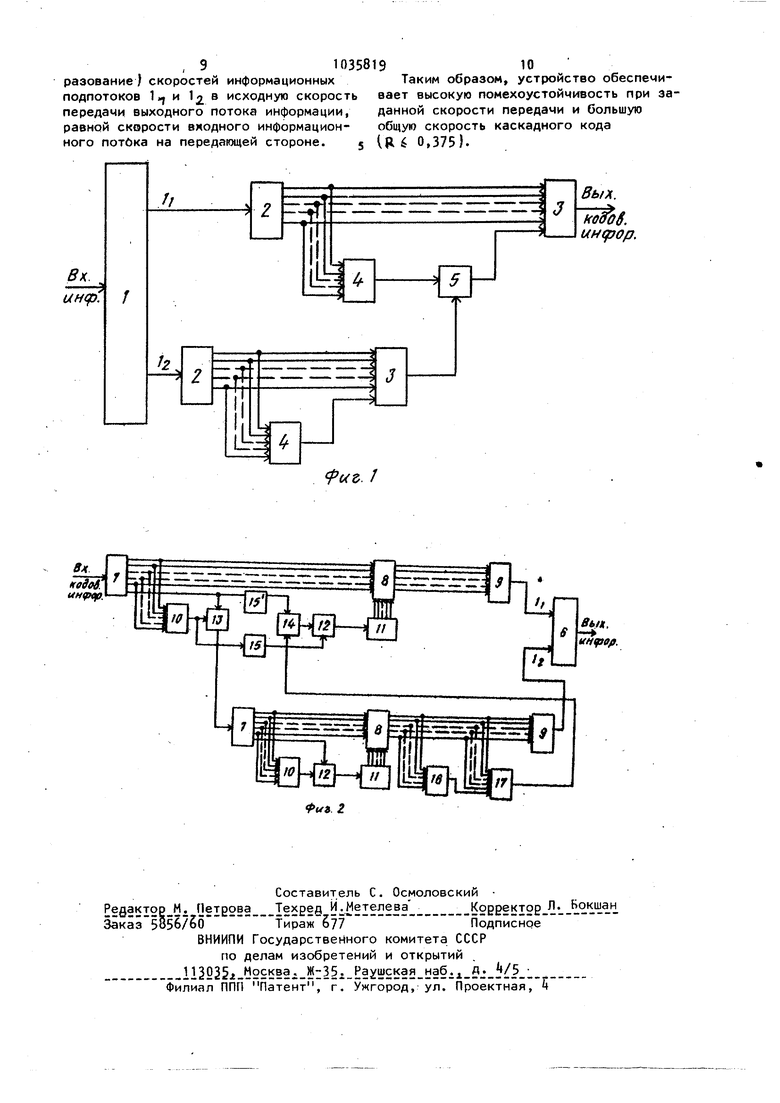

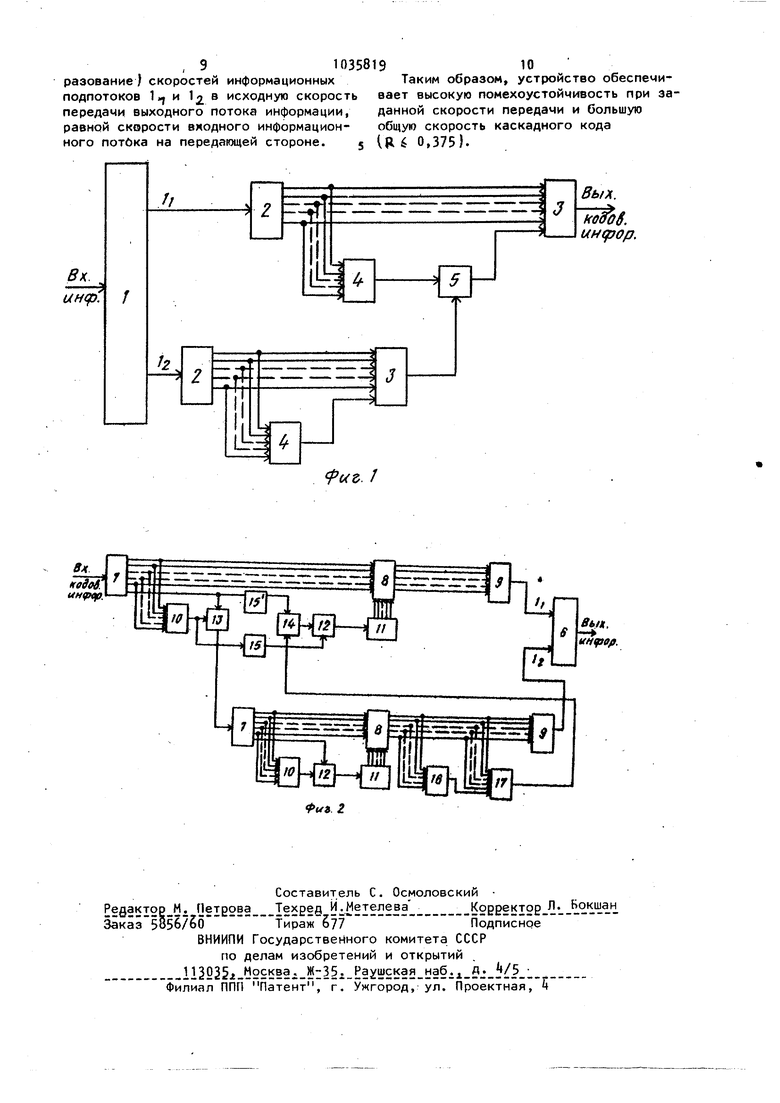

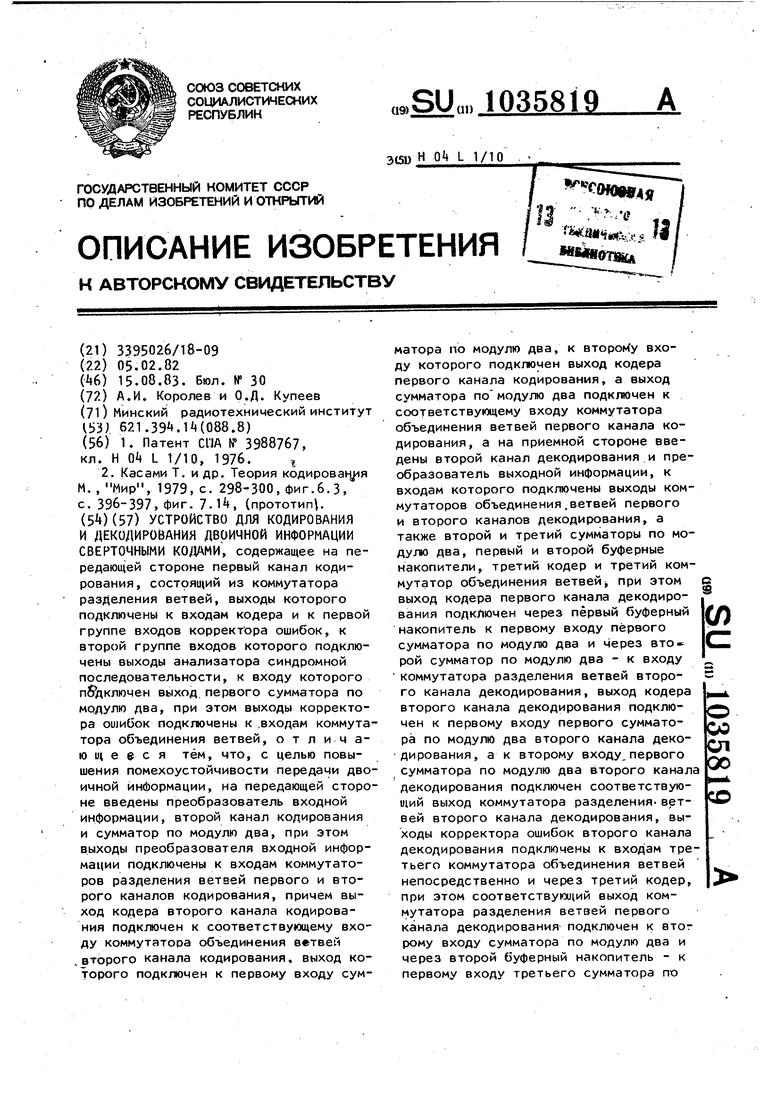

Изобретение относится к электросвя зи и может использоваться для повышения достоверности при передаче данных цифровых сигналов радиовещания, цифровых телевизионных сигналов по космическим каналам связи при кодировании и декодировании их сверточными кодами., Известен способ и устройство помехоустойчивого кодирования и декодиррвания дискретной информации, содержащее на передающей стороне последовательно соединенные источник информации, блок информации, первый кодирующий блок, второй кодирующий блок, MO дулятор или передатчик, а на приемной стороне - два разнесенных друг от дру га демодулятора- приемника и последо вательно соединенные с ними первый де кодирующий блок, приемный перемножитель,второй декодирующий блок,демультиплексор и получатель информации П Недостатками данного устройства являются низкая помехоустойчивость при заданной скорости передачи, малая об-, щая скорость каскадного кода (Р40,375 Наиболее близким к изобретению является устройство для помехоустойчивого кодирования vi декодирования двоичной информации сверточными кодами, содержащее на передающей стороне первый канал кодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера , и коммутатора объединения ветвей, а на приемной стороне - первый канал декодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректора , к второй группе входов которого подключены выходы анализатора синдром ной последовательности, к входу которого подключен выход первого сумматора по модулю два, при этом выходы корректора ошибок подключены к входам коммутатора объединения ветвей f. . Недостатком известного устройства также является низкая помехоустойчивость передачи двоичной информации при заданной скорости. Цель изобретения - повышение помехоустойчивости-передачи двоичной информации. Поставленная цель достигается тем, что в устройство для кодирования и декодирования двоичной информации сверточными кодами, содержащее на передающей стороне первый каналкодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и коммутатора .объединения ветвей, а на приемной стороне - первый канал декодирования, состоящий из коммутатора разделения ветвей, выходы которого подключены к входам кодера и к первой группе входов корректора ошибок, к второй группе входов которого подключены выходы анализатора синдромной последовательности, к входу которого подключен выход первого сумматора по моР(пую два, при этом выходы корректора ошибок подключены к входам коммутатора объединения ветвей, на передающей стороне введены преобразователь входной информации, второй канал кодирования и сумматор по модулю два, при этом выходы преобразователя входной информации подключены к входам коммутаторов разделения ветвей первого и второго каналов кодирования, причем выход кодера второго канала кодирования подключен к соответствующему входу коммутатора объединения ветвей второго канала кодирования, выход которого подключен к первому входу сумматора по модулю два, к второму входу которого .подключен выход кодера первого канала кодирования, а выход сумматора по модулю два подклю- чен к соответствующему входу коммутатора объединения ветвей первого канала кодирования,, а на приемной стороне введены второй канал декодирова31Пнйя и Преобразователь выходной информации, к входам которого подключены выходы коммутаторов объединения ветвей первого и второго каналов де.кодирования, а также второй и третий сумматоры по модулю два, первый и вто рой буферные накопители, третий кодер и третий коммутатор объединения ветвей, при этом выход кодера первого ка нала декодирования подключен через первый буферный накопитель к первому входу первого сумматора по модулю два и через второй сумматор по модулю два к входу коммутатора разделения ветвей второго канала декодирования, выход кодера второго канала декодирования подключен к первому входу первого сум матора по модулю два второго канала декодирования, а к второму входу первого сумматора, по модулю два второго канала декодирования подключен соответствуищий выход коммутатора разделения ветвей второго канала декодирования, выходы корректора ошибок второ го канала декодирования подключены к входам третьего коммутатора объединения ветвей непосредственно и через .третий кодер, при этом соответствующий выход коммутатора разделения ветвей первого канала декодирования подключен к второму входу второго сумматора по модулю два и через второй буферный накопитель - к первому входу третьего сумматора по модулю два, к второму входу которого подключен вы ход третьего коммутатора объединения 35 ветвей, а выход третьего сумматора помодулю два подключен к в орому входу .первого сумматора по модулю два. / На фиг. 1 приведена струкурная электрическая схема передающей части; до на.фиг. 2 - структурная схема приемной, части. Устройство содержит на передающей части преобразователь 1 входной информации, два канала кодирования, каждый из которых содержит коммутатор 2 разделения ветвей, коммутатор объединения ветвей и кодер 4, а также сумматор 5 по модулю два, и на приёмной стброне устройство содержит преобразователь 6 выходной информации и два канала декодирования, кажд из которых содержит коммутатор 7 разделения, ветвей, корректор 8 ошибок, коммутатор 9 объединения ветвей .кодер 10, анализатор 11 синдромной последовательности, первый сумматор 12 по модулю два, кроме того, пе вый канал декодирования содержит вто 9 рой и третий сумматоры 13 и I по моду ло два, первый и второй.буферные накопители 15 и 15 , а второй канал декодирования содержит дополнительно объединенные по входу и последовательно соединенные кодер 1б и коммутатор 17 объединения ветвей. Устройство работает следующим образом., . Входная информация в преобразователе 1 входной информации преобразуется в два ( / параллельных потока информации (при числе вложенных кодеков п 2 входной поток преобразуется в П7/. параллельных потока, при этом информационные скорости потоков 1 и 1 различны, а именно Ц 12В коммутаторе 2 разделения ветвей каждый информационный поток 1 - и 1 л разделяется на К и К 2 информационных подпотоков (в соответствии, со т.е. К скоростями сверточных кодов. К. / п. - первого канала кодирования второго канала кодирования ). С выхода каждого коммутатора 2 разделения ветвей информационные подпо токи поступают на входы коммутаторов 3 объединения ветвей и на входы кодеров k каждого канала кодирования. В кодерах из и-нформа ц ионных символов формируются проверочные символы, которые объединяются в проверочные последовательности. Формирование проверочных последовательностей производится в соответствии с выбранными порождающими полиномами сверточных кодов каждого канала кодирования. Во втором канале кодирования сформированная проверочная последовательность поступает на один из входов коммутатора 3 объединения ветвей, который формирует кодовую,последовательность путем объединения информационных подпотоков и подпотока проверочной последовательности. С выхода коммутатора 3 объединения ветвей второго канала кодирования кодовая последовательность поступает на один из входов сумматора 5 по модулю два, на второй вход которого поступает проверочная последовательность, сформированная кодером первого канала кодирования. В сумматоре 5 по модулю два произт водится суммирование по модулю два кодовой последовательности второго канала кодирования с проверочной последовательностью первого канала кодирования. В результате суммирования указанных последовательностей достигается уменьшение избыточности информации, поступающей в канал связи, с входа Коммутатора 3 объединения ветвей первого канала кодирования. Если скорость сверточного кода первого канала кодирования R . то избыточность информации составляет г 1/п а если скорость сверточного кода второго канала кодирования 2 2 2 ° избыточность информации второго канала кодирования составляет 2 l/n. В результате сум мирования по модулю два проверочной последовательности первого канала кодирования и кодовой последовательности второго канала кодирования общая избыточность информации, передаваемой в канал связи, определяется произведением избыточностей исходных сверточных кодов, т.е. г -рг Т как 1 и f 1 то их npdii3Beдение %удет меньше наименьшего из -jrТаким образом, общая скорость свер точного кода на выходе первого канала кодирования равна 2 ° эквивалентно увеличению скорости передачи информации или увеличению информационной про пускной способности канала (системы ) связи при избыточном кодировании дво.ичной информации сверточными кодами. С выхода сумматора 5 по модулю два сформированная последовательность поступает на один из входов коммутатора 3 объединения ветвей первого канал кодирования, который формируют выходную кодовую последовательность из информационных подпотоков и последовательности поступающей с сумматора. С выхода коммутатора 3 объединения ветвей кодовая последовательность поступает в канал связи. На приемной стороне принятая кодоёая последовательность поступает на вход коммутатора 7 разделения ветвей первого канала декодирования, с выхода которого символы информационных подпотоков поступают одновременно на входы корректора 8 ошибок и на входы кодера 10, а последовательност сформированная на передающей стороне путем суммирования по модулю два проверочной последовательности первого канала кодирования и кодовой последовательности второго канала кодирования, с выхода коммутатора 7 разделения ветвей поступает одновременна на вход первого буферного накопителя 15 и на один из входов третьего сумматора 1 по модулю два, на второй вход которого поступает проверочная последовательность, сформированная кодеррм 10 из принятых символов информационных подпотоков. При суммировании по модулю два указанных последовательностей производится снятие проверочной последовательности с принятой и формирование кодовой последовательности для второго канала декодирования. Так, если обозначим через Р проверочную последовательность, сформированную на передающей стороне кодером , и через Tg - кодовую последовательность второго канала кодирования, асуммированную по модулю два этих последовательностей через N . Если через Р-| обозначим проверочную последовательность, сформированную на приемной стороне кодером 10 первого канала декодирования, то при суммировании по моду/да два PI@ N получим р;© N р; ® PI© о I . ч- . 1 yjy I ч - 1 I 10 - 1о или точную копию кодовой последовательности второго канала декодирования в случае отсутствия помех в канале связи ). При наличии помех в канале связи сформированная проверочная последовательность Р JJ кодером 1 О первого канала декодирования отличается от проверочной последовательности Р-, сформированной кодером k первого канала кодирования на передающей стороне В этом случае при формировании кодовой последовательности Т наблюдается трансформирование или внесение ошибок в кодовую последовательность Количество ошибок в этой последовательности определяется количеством и типом ошибок в канале связи, а также типом порождающих полиномов кодеров k и 10 первого канала кодирования и декодирования. Это учитывается выбором исправляющей способности сверточного кода второй ступени кодирования и декодирования, т.е. исправляющая способность второго кодера выше первого кодера. Второй кодер должен исправлять максимальное количество ошибок, вносимых в кодовую последовательность пераым кодером при расчетной исправляющей способности первого кодера Сформированная кодовая последовательность fy поступает на вход коммутатора 7 разделения ветвей второго канала декодирования, с выходов которого символы информационных подпотоков одновременно поступают на входы корректора 8 ошибок и на входы кодера 10. Кодер 10 из принятых символов информационных подпотоков формирует проверочную последовательность, которая поступает на одии из входов первого сумматора 12 по модулю два, на второй вход которого поступает принятая проверочная последовательность с одного из выходов коммутатора 7 раз деления ветвей данного декодирования. Первый сумматор 12 по модулю два формирует синдромную последовательность путем суммирования по модулю два сформированной и принятой проверочных последовательностей Синдромная последовательность полностью определяет количество и тип ошибок. С выхода первого сумматора 12 по модулю два синдромная последовательност поступает на вход анализатора 11 синд ромной последовательности, который производит анализ этой последовательности, обнаружение и исправление ошибок в пределах корректирующей спосс ности кода. Синдромная последовательность заполняет регистр сдвига анализатора 11 синдромной последовательности, с соответствующих разрядов ( ячеек памяти ) регистра сдвига информации поступает на пороговые эле менты. При отсутствии ошибок на выхо де пороговых элементов присутствуют нулевые символы и коррекции ошибок не производится, а при наличии ошибок на выходах пороговых элементов присутствуют ненулевые символы, кото рые производят коррекцию ошибочных символов на выходах корректора 8 оши бок данного канала декодирования. С выходов корректора 8 ошибок сим волы информационных подпотоков одновременно поступают на входы коммутатора 9 объединения ветвей, на входы коммутатора 17 объединения ветвей и на входы кодера 16, который из инфор мационных символов, прошедших коррек цию ошибок, формирует проверочную последовательность, аналогичную проверочной последовательности, сформированной кодером и на передающей сто роне вторым каналом кодирования. Сфо мированная проверочная последователь ность поступает на один из входов до полнительного коммутатора 17 объедин ния ветвей, который формирует кодову последовательность Тл, аналогичную принятой кодовой последовательности, о в которой отсутствуют ошибки, вносимые первым каналом декодирования. Сформированная кодовая ;последовательность Т поступает на один из входов второго сумматора 13 по модулю два, на другой вход которого поступает заержанная последовательности N Р ® Т- с выхода первого буферного накопителя 15. При суммировании по модулю два последовательности N Р-|0Т2И вновь сформированной кодовой последовательности Тп второго канала коднрования получим на входе второго сумматора 13 по модулю два принятую проверочную последовательность Р первого канала декодирования, т.е. Р,0Т-0 Tj Р.,, которая поступает на один из входов первого сумматора 12 по мо- . дулю два первого канала декодирования. На другой вход первого сумматора 12 по модулю два через второй буферный накопитель 15 поступает сформирован я кодером И) проверочная последовательность Р . Первый и второй буферные накопители предназначены для фазирования символов информационных подпотоков и соответствующих им символов синдромной последовательности, обус ловленных задержкой формирования кодовой последовательности второго канала декодирования. Длина регистра сдвига первого и второго буфферных накопителей 15 и 15 определяется длиной регистра кодера 16 второго канала декодирования. Сформированная синдромная последовательность с выхода первого сумиатоР 12 по модулю два поступает в анализатор 11 синдромной последовательности, далее, как во втором канале декодирования, производится обнаружение и исправление ошибочных символов, в информационных подпотоках первого канала декодирования. С выходов корректора 8 ошибок символы информационных подпотоков поступают на входы коммутатора 9 объединения ветвей данного канала декодирования. В коммутаторах 9 объединения ветвей первого и второго каналов декодирования производится объединение информационных подпотоков в один последовательный поток соответственно 1. и 2 которые поступают на преобразователь 6 выходной информации. Преобразователь 6 выходной информации производит согласование (преоб, 91035819

разование ) скоростей информационных подпотоков 1 и 12 в исходную скорость передачи выходного потока информации, равной скорости входного информационного потока на передающей стороне. s Я ).

Таким образом, устройство обеспечивает высокую помехоустойчивость при заданной скорости передачи и большую общую скорость каскадного кода

kooot UHqjop.

ff(t. /

| К Патент CUA № 3988767, кл | |||

| Н 0 L 1/10, 1976 | |||

| ,; 2 | |||

| Касами Т | |||

| и др | |||

| Теория кодирова у я М | |||

| , Мир, 1979, с | |||

| РАССЕИВАЮЩИЙ ТОПЛИВО МЕХАНИЗМ | 1920 |

|

SU298A1 |

| Приспособление для подъема падающих гребней в машинах льнопрядильного, джутового и т.п. производств | 1913 |

|

SU396A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-08-15—Публикация

1982-02-05—Подача