элементов И с первого по (2 - размерность преобразования), 2 блоков элементов ИЛИ, регистры с первого по , сумматоры с пер10

15

20

Изобретение относится к автоматике и вычислительной технике и может быть использовано при цифровой обработке сигналов.

Целью изобретения является повышение быстродействия устройства.

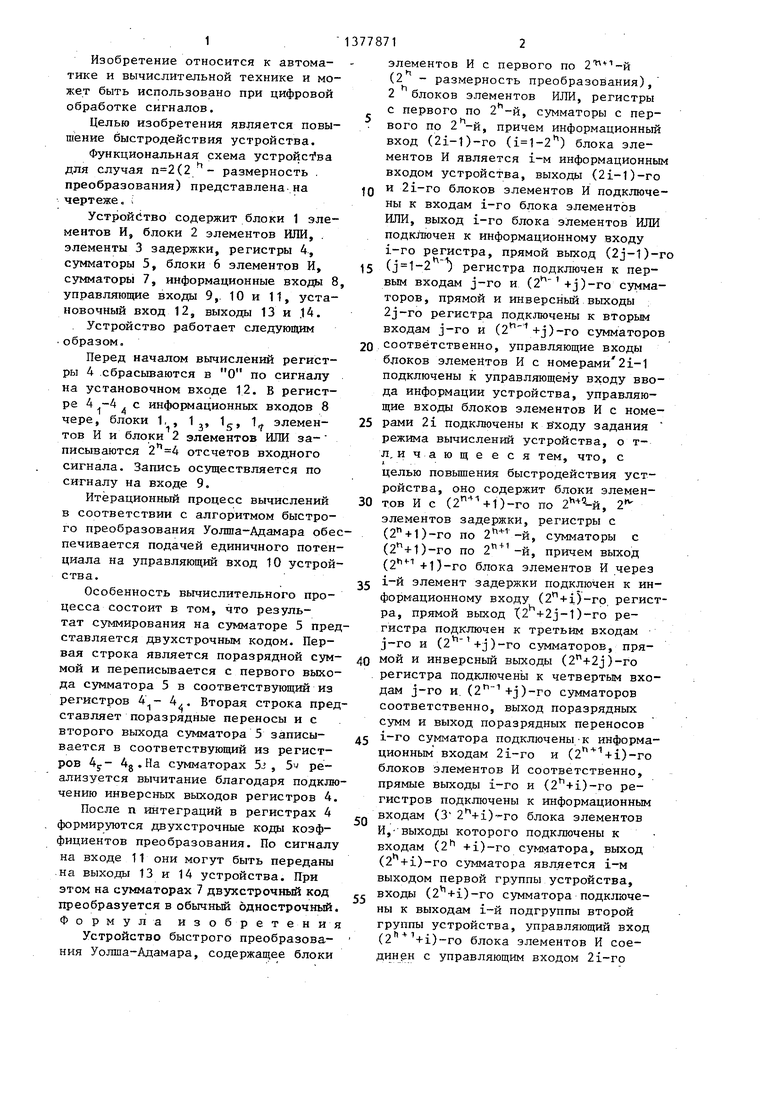

Функциональная схема ycTponcfBa для случая (2/- размерность . преобразования) представлена на чертеже. :

Устройство содержит блоки 1 элементов И, блоки 2 элементов ИЛИ, . элементы 3 задержки, регистры 4, сумматоры 5, блоки 6 элементов И, сумматоры 7, информационные входы 8, управляющие входы 9,. 10 и 11, установочный вход 12, выходы 13 и .14. . Устройство работает следующим .образом.

Перед началом вычислений регистры 4 сбрасываются в О по сигналу на установочном входе 12. В регистре 4 -4 с информационных входов 8 чаре, блоки 1, , 1 ,, 1, 1 элементов И и блоки 2 элементов ИЛИ за- писываются отсчетов входного сигнала. Запись ос тцествляется по сигналу на входе 9.

Итерационный процесс вычислений в соответствии с алгоритмом быстрого преобразования Уолша-Адамара обеспечивается подачей единичного потенциала на управляющий вход 10 устройства.

Особенность вычислительного процесса состоит в том, что результат сзгммирования на сумматоре 5 представляется двухстрочным кодом. Первая строка является поразрядной сум- д мой и инверсный выходы ()-го мой и переписьгоается с первого выхо- регистра подключены к четвертым вхового по , причем информационный вход (21-1)-го () блока элементов И является i-M информационным входом устройства, выходы (21-1)-го и 21-го блоков элементов И подключены к входам 1-го блока элементов ИЛИ, выход 1-го блока элементов ИЛИ подключен к информационному входу 1-го регистра, прямой выход (2j-1)-ro ( j регистра подключен к первым входам д-го и ()-ro сумматоров, прямой и инверсный выходы 2j-ro регистра подключены к вторым входам j-ro и ( +j)-ro сумматоров соответственно, управляющие входы блоков элементов И с номерами 21-1 подключены к управляющему входу ввода информации устройства, управляющие входы блоков элементов И с номе25 рами 21 подключены к в ходу задания режима вычислений устройства, о т- л, ичающееся тем, что, с целью повышения быстродействия устройства, оно содержит блоки элемен30 тов И с ()-ro по , 2 элементов задержки, регистры с (2 + 1)-го по -и, сумматоры с (2 + 1)-го по , причем выход ( )-го блока элементов И через

35 элемент задержки подключен к информационному входу (2 + 1)-го, регистра, прямой выход Т2 +2j-l)-ro регистра подключен к третьим входам J-го и (2 )-ro сумматоров, пряэлементов И с первого по (2 - размерность преобразования), 2 блоков элементов ИЛИ, регистры с первого по , сумматоры с пер

мой и инверсный выходы ()-го регистра подключены к четвертым вхового по , причем информационный вход (21-1)-го () блока элементов И является i-M информационным входом устройства, выходы (21-1)-го и 21-го блоков элементов И подключены к входам 1-го блока элементов ИЛИ, выход 1-го блока элементов ИЛИ подключен к информационному входу 1-го регистра, прямой выход (2j-1)-ro ( j регистра подключен к первым входам д-го и ()-ro сумматоров, прямой и инверсный выходы 2j-ro регистра подключены к вторым входам j-ro и ( +j)-ro сумматоров соответственно, управляющие входы блоков элементов И с номерами 21-1 подключены к управляющему входу ввода информации устройства, управляющие входы блоков элементов И с номерами 21 подключены к в ходу задания режима вычислений устройства, о т- л, ичающееся тем, что, с целью повышения быстродействия устройства, оно содержит блоки элементов И с ()-ro по , 2 элементов задержки, регистры с (2 + 1)-го по -и, сумматоры с (2 + 1)-го по , причем выход ( )-го блока элементов И через

элемент задержки подключен к информационному входу (2 + 1)-го, регистра, прямой выход Т2 +2j-l)-ro регистра подключен к третьим входам J-го и (2 )-ro сумматоров, пря

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО БЫСТРОГО ПРЕОБРАЗОВАНИЯ УОЛША-АДАМАРА | 1991 |

|

RU2023299C1 |

| Устройство для выполнения дискретных ортогональных преобразований | 1984 |

|

SU1233168A1 |

| Устройство для вычисления произведения векторов (его варианты) | 1984 |

|

SU1280389A1 |

| Устройство для выбора упорядоченной последовательности данных | 1983 |

|

SU1109738A1 |

| Устройство для вычисления многочленов | 1980 |

|

SU960806A1 |

| Устройство для умножения п-разряд-НыХ чиСЕл | 1978 |

|

SU813417A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Процессор быстрого преобразования уолша-адамара | 1989 |

|

SU1795471A1 |

| Устройство для выделения экстремального числа из @ @ -разрядных двоичных чисел | 1982 |

|

SU1070543A1 |

| Цифровой генератор базисных функций | 1980 |

|

SU968796A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при цифровой обработке сигналов. Цель изобреIff 9 атения - повьппение быстродействия устройства. Устройство содержит блоки 1.ц элементов И, блоки 2,- 2„ элементо в ИЛИ, элементы задержки 3,-3 , регистры , сумматоры 5,блоки ,,элементов И, сумматоры 7 -7 , информационные входы управляющие входы 9, 10, 11, установочный вход 12, выходы , 14 -14 . Введение дополнительных блоков элементов И, элементов задержки, регистров и сумматоров позволило повысить быстродействие устройства благодаря использованию двухстрочных кодов операндов, не требующих междуразрядных перекосов в операциях суммирования. 1 ил. 12 (Л Сдд 1 00 |

да сумматора 5 в соответствующий из регистров 4у. Вторая строка представляет поразрядные переносы и с второго выхода сумматора 5 записывается в соответствующий из регистров 4у - 4g . На сумматорах , 5w реализуется вычитание благодаря подключению инверсных выходов регистров 4. После п интеграции в регистрах 4 формируются двухстрочные коды коэффициентов преобразования. По сигналу на входе 11 они могут быть переданы на выходы 13 и 14 устройства. При этом на сумматорах 7 двухстрочный код преобразуется в обычный однострочньй. Формула изобретения

Устройство быстрого преобразования Уолша-Адамара, содержащее блоки

дам j-ro и. ()-ro сумматоров соответственно, выход поразрядных сумм и выход поразрядных переносов 5 1-го сумматора подключены-к информационным входам 21-го и ( + 1)-го блоков элементов И соответственно, прямые выходы 1-го и ()-го регистров подключены к информационным входам (3 )- -го блока элементов И,- выходы которого подключены к входам (2 +1)-го сумматора, выход (2 + 1)-го сумматора является 1-м выходом первой группы устройства, входы ()-го сумматора подключены к выходам 1-й подгруппы второй группы устройства, управляющий вход ()-ro блока элементов И сое- с управляющим входом 21-го

0

5

313778714

блока элементов И, входы установкиментов И с ( ) -го по

в О всех регистров подключены подключены к управлятоустановочному входу устройства, уп-шему входу вьдачи информации

равляющие входы блоков эле- устройства.

| Устройство для преобразования по функциям Уолша | 1980 |

|

SU918952A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ изготовления сверхминиатюрных ламп накаливания | 1981 |

|

SU957320A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1985-12-09—Подача