сл

оо

оо

о

О) С5

IPI/if

и 14, элемент 2-2И-ИЛИ 6, блоки 12 и 10 памяти, схему 13 сравнения,, информационные входы 23, вход 24 наличия информации, информационные выходы 25, выход 26 ошибки. Устрой1378066

ство для преобразования кодов исклю чает прием и преобразование ложного или искаженного кода, чем достигается достоверность преобразуемой информации. 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый генератор ступенчатого напряжения | 1983 |

|

SU1095368A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| Программируемый генератор импульсов | 1985 |

|

SU1287254A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Генератор систем базисных функций Аристова | 1988 |

|

SU1599850A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство контроля состояния объектов | 1985 |

|

SU1366993A1 |

| Устройство для определения характеристик связности ориентированного графа | 1983 |

|

SU1133596A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и преобразования информации. Целью изобретения является повышения достоверности преобразования путем предварительной проверки принятого кода. Устройство для преобразования кодов содержит триггеры 7,19,20 и 21, счетчики 5,16 и 11, коммутатор 1, регистр 22, управляемый генератор 2, элементы НЕ 17 и 18, элементы И 3,4, элементы И-НЕ 9 и 15, р-вхо- довый и (р+1)-входовый элементы И 8

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля и преобразования информации.

Цель изобретения - повьппение достоверности преобразования кода путем предварительной проверки принятого кода.

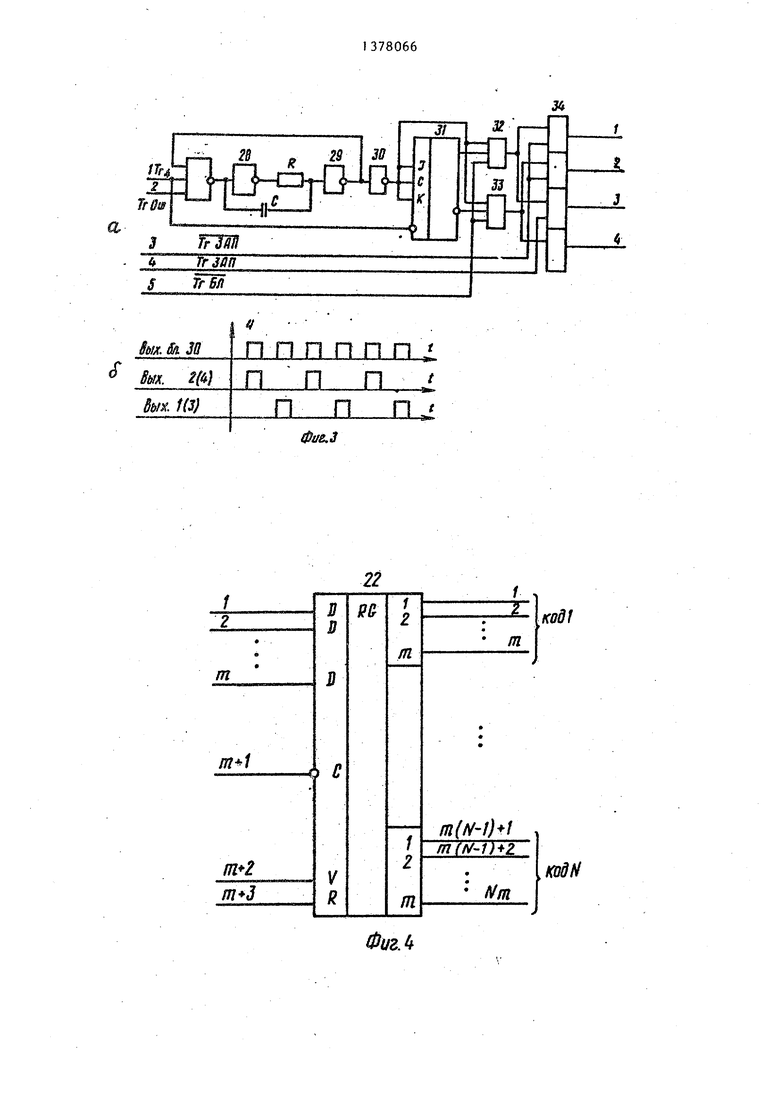

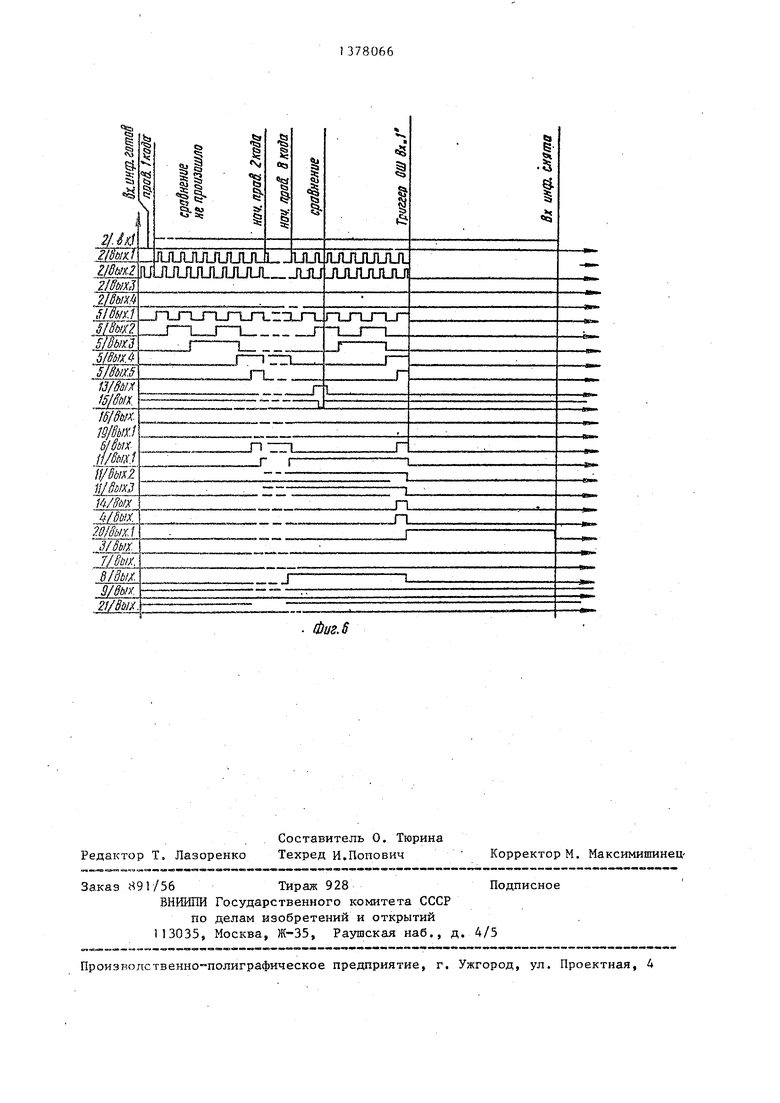

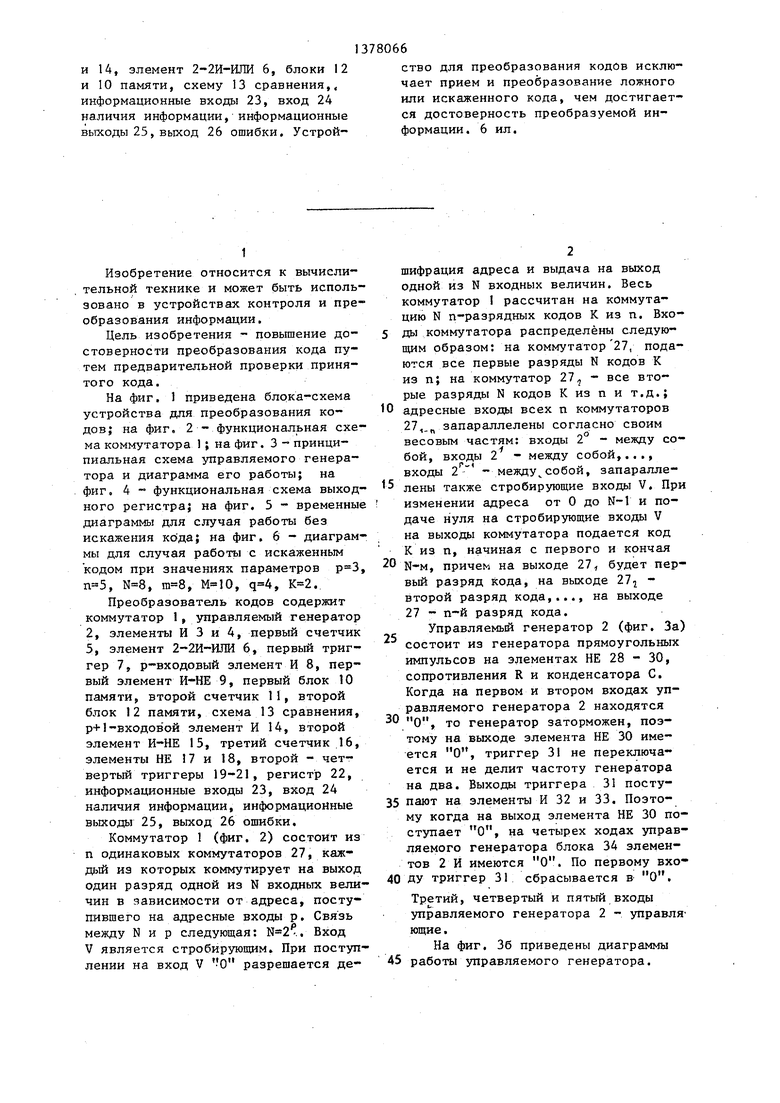

На фиг, 1 приведена блока-схема устройства для преобразования кодов; на фиг. 2 - функциональная схема коммутатора 1 ; на фиг. 3 - принципиальная схема управляемого генератора и диаграмма его работы; на фиг, 4 функциональная схема выходного регистра; на фиг, 5 - временные диаграммы для случая работы без искажения кбда; на фиг, 6 -- диаграммы для случая работы с искаженньм кодом при значениях параметров , , , , , , ,

Преобразователь кодов содержит коммутатор 1, управляемый генератор 2, элементы И 3 и 4, первый счетчик 5, элемент 2-2И-ШШ 6, первый триггер 7, р-входовый элемент И 8, первый элемент И-НЕ 9, первый блок 10 памяти, второй счетчик 11, второй блок 12 памяти, схема 13 сравнения, р+1-входовой элемент И 14, второй элемент И-НЕ 15, третий счетчик 16, элементы НЕ 17 и 18, второй - четвертый триггеры 19-21, регистр 22, информационные входы 23, вход 24 наличия информации, информационные выходы 25, вьпсод 26 ошибки.

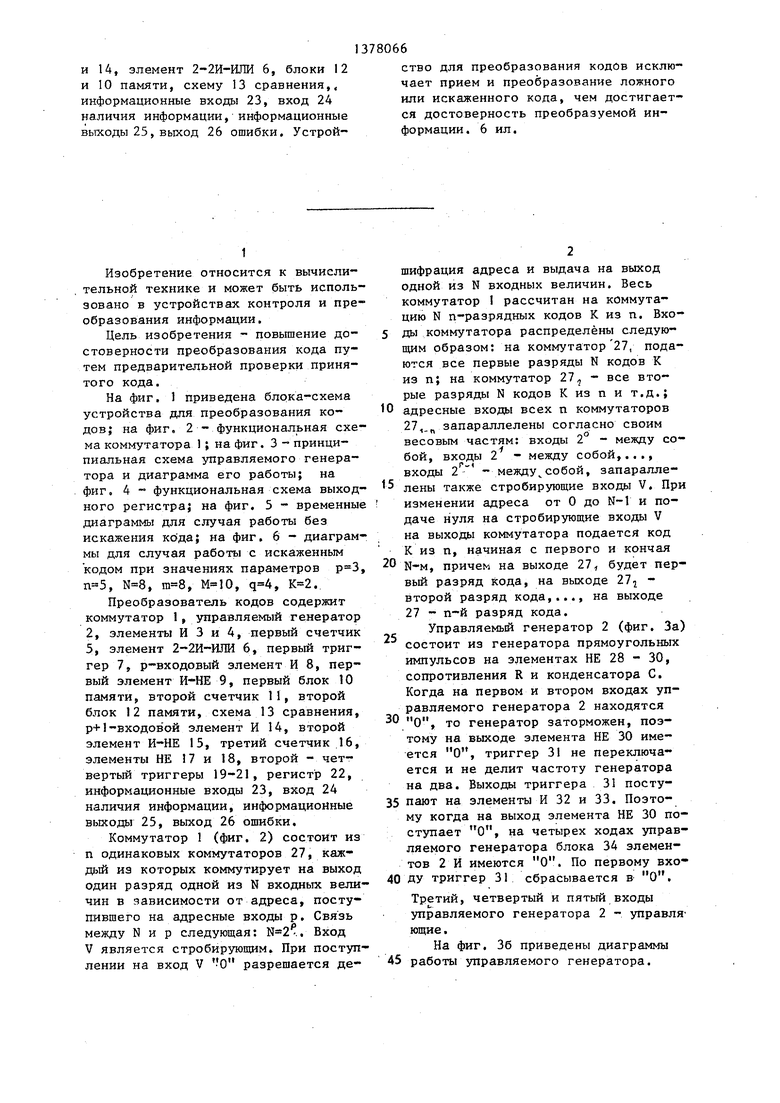

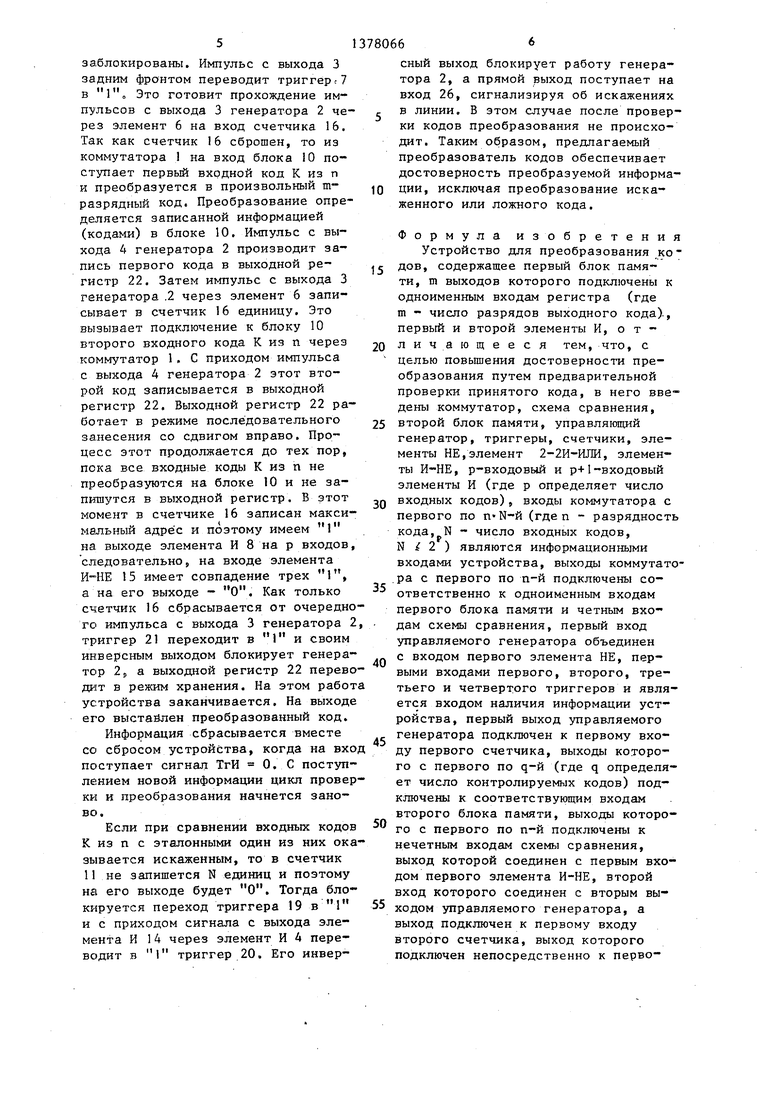

Коммутатор 1 (фиг, 2) состоит из п одинаковых коммутаторов 27, каж- Д1зй из которых коммутирует на выход один разряд одной из N входных величин в зависимости от адреса, поступившего на адресные входы р, Связь между Кир следующая: N-2 ., Вход V является стробирующим. При поступлении на вход V О разрешается дешифрация адреса и выдача на выход одной из N входных величин. Весь коммутатор I рассчитан на коммутацию N п-разрядных кодов К из п, Входы коммутатора распределены следующим образом: на коммутатор 27, подаются все первые разряды N кодов К из п; на коммутатор 27, - все вторые разряды N кодов К из п и т.д.;

адресные входы всех п коммутаторов 27,.„ запараллелены согласно своим весовым частям: входы 2 - между собой, входы 2 - между собой,.,,, входы 2 - между собой, запараллелены также стробирующие входы V. При изменении адреса от О до N-1 и подаче нуля на стробирующие входы V на выходы коммутатора подается код К из п, начиная с первого и кончая

N-MJ причем на выходе 27, будет первый разряд 1:ода, на выходе 27j - второй разряд кода,..,, на выходе 27 - п-й разряд кода.

Управляемый генератор 2 (фиг. За) состоит из генератора прямоугольных импульсов на элементах НЕ 28 - 30, сопротивления R и конденсатора С. Когда на первом и втором входах управляемого генератора 2 находятся

о, то генератор заторможен, поэтому на выходе элемента НЕ 30 имеется О, триггер 31 не переключается и не делит частоту генератора на два. Выходы триггера 31 посту-

пают на элементы И 32 и 33, Поэтому когда на выход элемента НЕ 30 поступает О, на четырех ходах управляемого генератора блока 34 элементов 2 И имеются О, По первому вхоДУ триггер 31 сбрасывается в О,

Третий, четвертый и пятый входы управляемого генератора 2 - управля ющне.

На фиг. Зб приведены диаграммы работы управляемого генератора.

Блок 10 памяти (фиг. 7) аналогичен блоку 12, но имеет п,адресных входов и m ВЫ5СОДОВ, где m - число разрядов преобразованного кода. Таким образом, подавая код К из п на адресные входы при наличии разрешения на считывание по входу V, на выходе имеем т-разрядный преобразованный код. Блок 12, как и блок 10, необходимо предварительно подпрог- раммировать, произведя в него запис

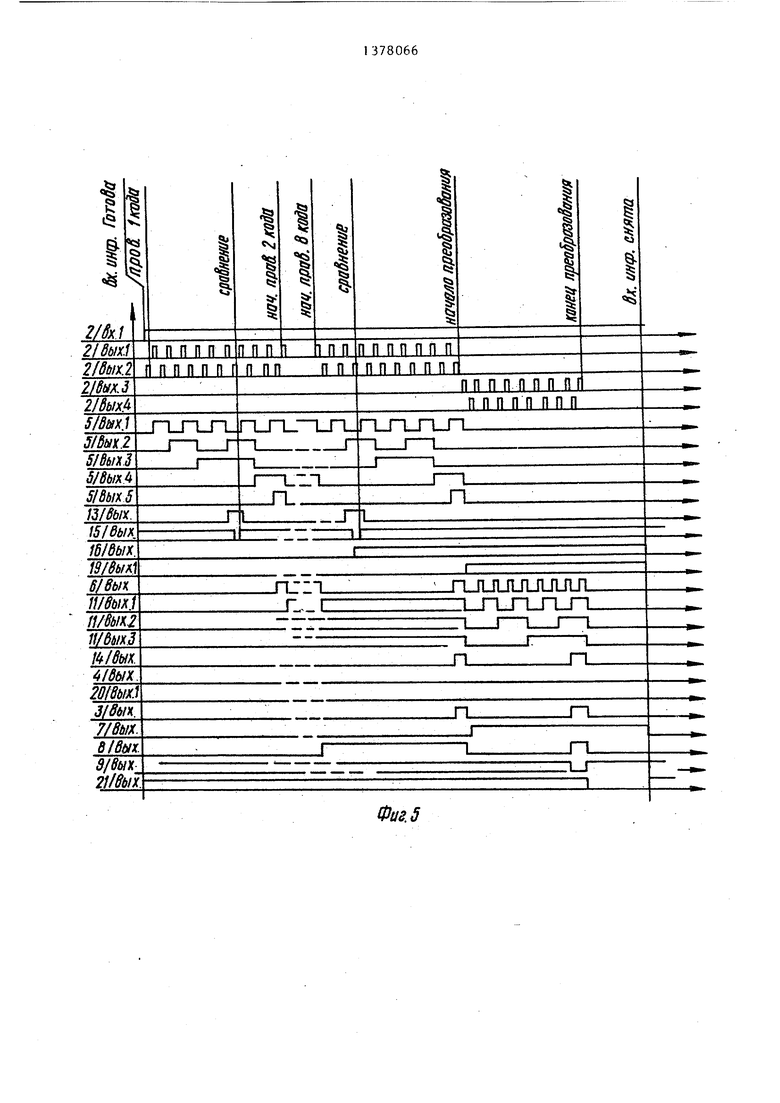

Выходной регистр 22 (фиг, 4) представляет собой стандартньш-регистр на га входов и Nm выходов и работает в двух режимах:

1)при 1 на входе т+2 (сигнал V) и О на входе га+З (сигнал R) с поступлением импульса на вход

т+1 (сигнал С) производится запись в регистр по переднему фронту импулса на входе т+1 информации, поданной на входы 1,..., т. С приходом второго импульса на вход т+1 предыдущая информация сдвигается вправо -на один разряд, а новая записывается на старое место и т.д.

2)при поступлении О на вход т+2 регистр переходит в режим хранения записанной информации.

С приходом 1 на вход т+3 регистр сбрасывается.

Устройство для преобразования кодов работает следующим образом.

На вход устройства (фиг. 1) поступает входная информация N кодов. К из п и поступает сигнал наличия информации ТгИ. Входная информация поступает на входы коммутатора 1 ... .,.nN. Сигнал наличия информации ТгИ равен 1, когда входная информация готова для проверки и .преобразования. При смене входной информации на новую сигнал ТгИ становится равным О, и как только новая входная информация становится готовой для проверки и преобразования, сигнал ТгИ снова становится равным 1. Сигнал ТгИ играет двоякую роль Когда ТгИ - О, этот сигнал явля- ется сигналом сброса в исходное состояние преобразователя кода. Когда ТгИ - 1, этот сигнал снимает сбро с преобразователя и запускает пре- обр азователь для проверки и преобразования кода. Начинает работать управляемый генератор 2, появляется первый импульс на выходе генератора 2 и так как после сброса счетчик 16

0

5

0

5

0

5

0

5

в нуле, с коммутатора 1 в преобразователь поступает первый код К из п, который поступает на схему 13 сравнения i С выхода блока 12 на схему 13 сравнения поступает эталонный код К из п при нулевом адресе счетчика 5. Если происходит сравнение, то через схему i3 в счетчик 11 записывается единица. Если сравнения не происходит, то в счетчик 11 единица не записывается. С приходом импульса с выхода генератора 2 в счетчик 5 записывается единица, и на схему сравнения подается от блока 12 второй эталонный код К из п. Если происходит сравнение с приходом очередного импульса с генератора 2, в счетчик 11 записывается единица. Этот процесс продолжается до тех пор, пока не будут сверены с первым кодом К из п, поступившим с коммутатора 1 на схему сравнения, множество всех элементов эталонных кодов, записанных в блоке 12. Если первый код К из п, поступивший из коммутатора 1 не искажен, то он сравнивается с одним из эталонных кодов блока 12 и в счетчик II записывается одна единица. Перенос счетчика 5 через элемент 2-2И-ИЛИ 6 записывает в счетчик 16. единицу. Выходы счетчика I 1 являются адресом для коммутатора 1. Поэтому из коммутатора 1 поступает на вход схемы 13 сравнения второй входной код К из п. Опять начинается процесс сравнения его с элементами множества эталонных кодов, записанных в блоке 12. При сравнении с одним из них в счетчик 11 записывается единица. Так продолжается до тех пор, пока не будут перебраны все адреса коммутатора 1 и не проверено, кскаж&н или нет хотя бы один входной код К из п. Если ни один код не искажен, в счетчик 11 записывается N единиц и единица с выхода счетчика 11 через элемент НЕ 18 блокирует переход триггера 20 в 1, так как на выходе счетчика 11 1, а в счетчике 16 записан максимальный адрес, перенос с выхода счетчика 5 через элементы И 14 и 3 переводит триггер 19 в 1. Одновременно этот перенос сбрасывает счетчик 16, сбрасывается также счетчик 5, так как триггер 19 перешел в

2 начинает работу а выходы 1 и 2

заблокированы. Импульс с выхода 3 задним фронтом переводит триггер г 7 в Это готовит прохождение импульсов с выхода 3 генератора 2 через элемент 6 на вход счетчика 16. Так как счетчик 16 сброшен, то из коммутатора 1 на вход блока 10 поступает первый входной код К из п и преобразуется в произвольный га- разрядный код. Преобразование определяется записанной информацией (кодами) в блоке 10. Импульс с выхода 4 генератора 2 производит запись первого кода в выходной регистр 22. Затем импульс с выхода 3 генератора .2 через элемент 6 записывает в счетчик 16 единицу. Это вызывает подключение к блоку 10 второго входного кода К из п через коммутатор 1. С приходом импульса с выхода 4 генератора 2 этот второй код записывается в выходной регистр 22. Выходной регистр 22 работает в режиме последовательного занесения со сдвигом вправо. Процесс этот продолжается до тех пор, пока все входные коды К из п не преобразуются на блоке 10 и не запишутся в выходной регистр. В этот момент в счетчике 16 записан максимальный адрес и поэтому имеем 1 на выходе элемента И 8 на р входов, следовательно, на входе элемента И-НЕ 15 имеет совпадение трех 1, а на его выходе - О. Как только сметчик 16 сбрасывается от очередного импульса с выхода 3 генератора 2 триггер 21 переходит в 1 и своим инверсным выходом блокирует генератор 2р а выходной регистр 22 переводит в режим хранения. На этом работ устройства заканчивается. На выходе его выстайлен преобразованный код.

Информация сбрасывается вместе со сбросом устройства, когда на вхо поступает сигнал ТгИ 0. С поступлением новой информации цикл проверки и преобразования начнется заново.

Если при сравнении входных кодов К из п с эталонными один из них оказывается искаженным, то в счетчик 11 не запишется N единиц и поэтому на его выходе будет О. Тогда блокируется переход триггера 19 в 1 и с приходом сигнала с выхода элемента И 14 через элемент И 4 переводит в 1 триггер 20. Его инверсный выход блокирует работу генератора 2, а прямой выход поступает на вход 26, сигнализируя об искажениях

в линии. В этом случае после проверки кодов преобразования не происходит. Таким образом, предлагаемый преобразователь кодов обеспечивает достоверность преобразуемой информации, исключая преобразование искаженного или ложного кода.

Формула изобретения Устройство для преобразования кодов, содержащее первый блок памяти, m выходов которого подключены к одноименным входам регистра (где m - число разрядов выходного кода)., первьгй и второй элементы И, о т личающееся тем, что, с целью повьштения достоверности преобразования путем предварительной проверки принятого кода, в него введены коммутатор, схема сравнения,

второй блок памяти, управляющий

генератор, триггеры, счетчики, элементы НЕ,элемент 2-2И-ИЛИ, элементы И-НЕ, р-входовый и Р+1-ВХОДОВЫЙ элементы И (где р определяет число

входных кодов), входы коммутатора с первого по n N-й (гдеп - разрядность кода, N - число входных кодов, N / 2 ) являются информационными входами устройства, выходы коммутато- .ра с первого по п-й подключены соответственно к одноименным входам первого блока памяти и четным входам схемы сравнения, первый вход управляемого генератора объединен с входом первого элемента НЕ, первыми входами первого, второго, третьего и четвертого триггеров и является входом наличия информации устройства, первый выход управляемого генератора подключен к первому входу первого счетчика, выходы которого с первого по q-й (где q определяет число контролируемых кодов) подключены к соответствующим входам второго блока памяти, выходы которого с первого по п-й подключены к нечетным входам схемы сравнения, выход которой соединен с первым входом первого элемента И-НЕ, второй вход которого соединен с вторым выходом управляемого генератора, а выход подключен к первому входу второго счетчика, выход которого подключен непосредственно к перво

му входу первого элемента И и через второй элемент НЕ - к первому входу второго элемента И, выход которого соединен с вторым и третьим входами третьего триггера, первый выход которого подключен к второму входу управляемого генератора, третий выход которого соединен с (т+1)-м входом регистра, четвертый выход подключен к первому входу элемента 2-2И-ИЛИ.И второму входу первого триггера, выход которого подключен к первому входу второго элемента И-НБ и второму входу элемента 2-2И- ИЛИ, выход которого соединен с первым входом третьего счетчика, соответствующие выходы которого с первого по р-й подключены к входам коммутатора с (n N+l)-tt по (п Н+р)-й, одноименным входам р+1-входового элемента И и одноименным входам р- входового элемента И, выход которого соединен с вторым входом второго элемента И-НЕ, выход которого под- ключен к второму входу четвертого триггера, выход которого подключен к (ffl+2)-My входу регистра и третьему входу управляемого генератора, (q+l)-H выход первого счетчика подключен к третьему входу элемента 2-2И-ИЛИ и (р+1)-му входу р+1-входового элемента И, выход которого соединен с вторыми входами первого и второго элементов И, выход первого элемента И соединен с вторым и третьим входами второго триггера, первый выход которого соединен с третьим входом второго элемента И-НЕ и четвертым входом управляемого генератора, второй выход второго триггера подключен к четвертому входу одноименного триггера, третьего триггера и элемента 2-2И- ИЛИ и пятому входу управляемого генератора, выход первого элемента НЕ подключен к (п Н+р+1)-му входу коммутатора, вторым входом первого, второго и третьего счетчиков, к (п+1)-му, (q+l)-My,(т+3)-му входам соответственно первого и второго блоков памяти и регистра, выходы которого с первого по N.m-й являются информационными выходами устройства, второй выход третьего триггера является выходом ошибки устройства.

J. J

ФигЛ

Фиг. 5

| Устройство для контроля данных, представленных в кодах "к"из"п | 1978 |

|

SU781815A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для преобразования кодов с одного языка на другой | 1982 |

|

SU1034045A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-02-28—Публикация

1986-04-10—Подача