САЭ

СО

о

Изобретение относится к электротехнике, в частности к вторичным источникам питания, и может быть использовано для стабилизации высокого уровня постоянного напряжения.

Цель изобретения - повышение быстродействия и надежности.

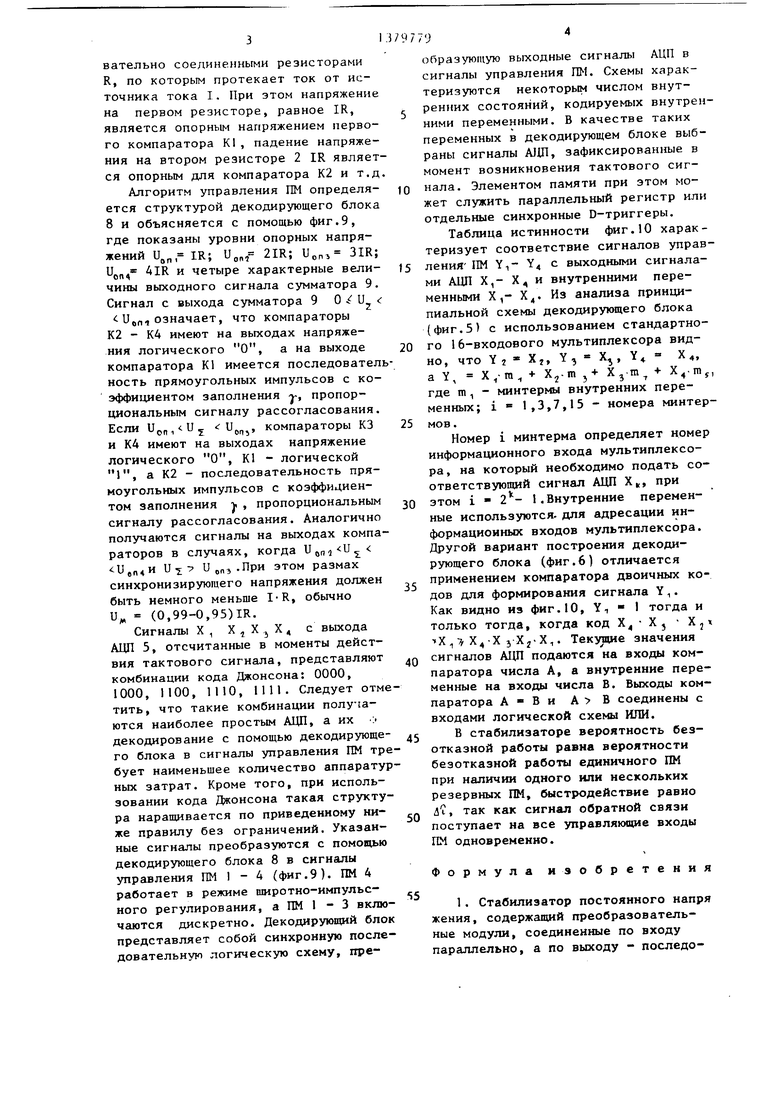

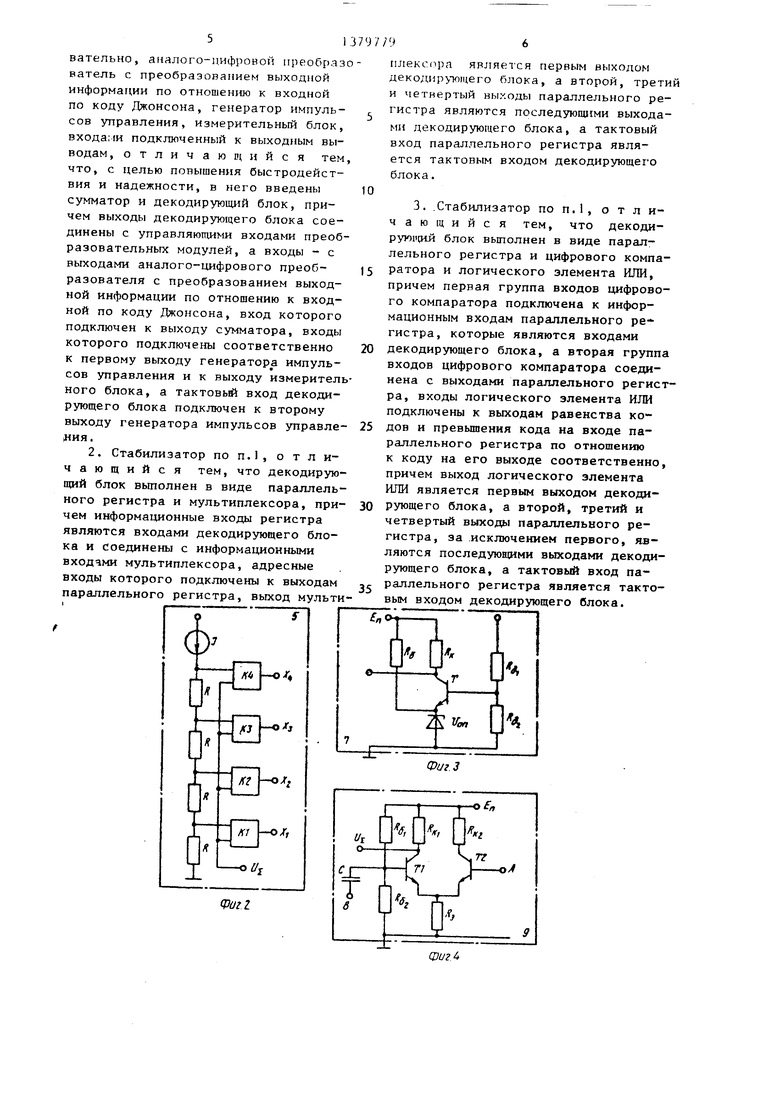

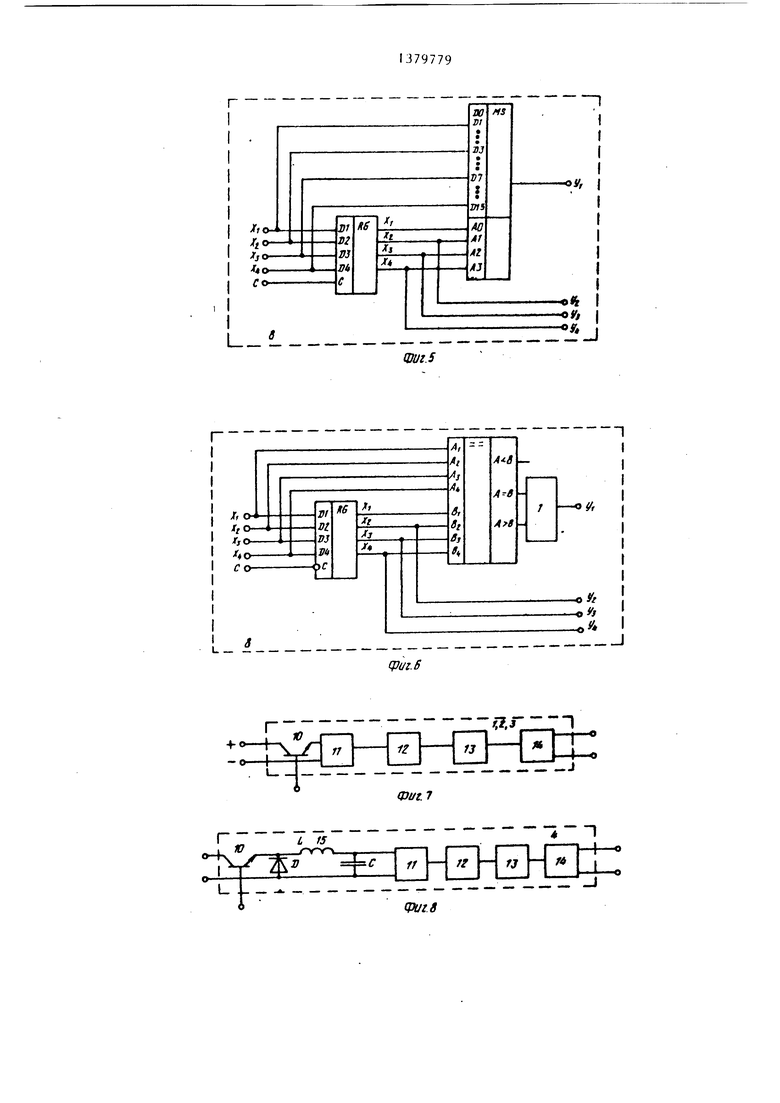

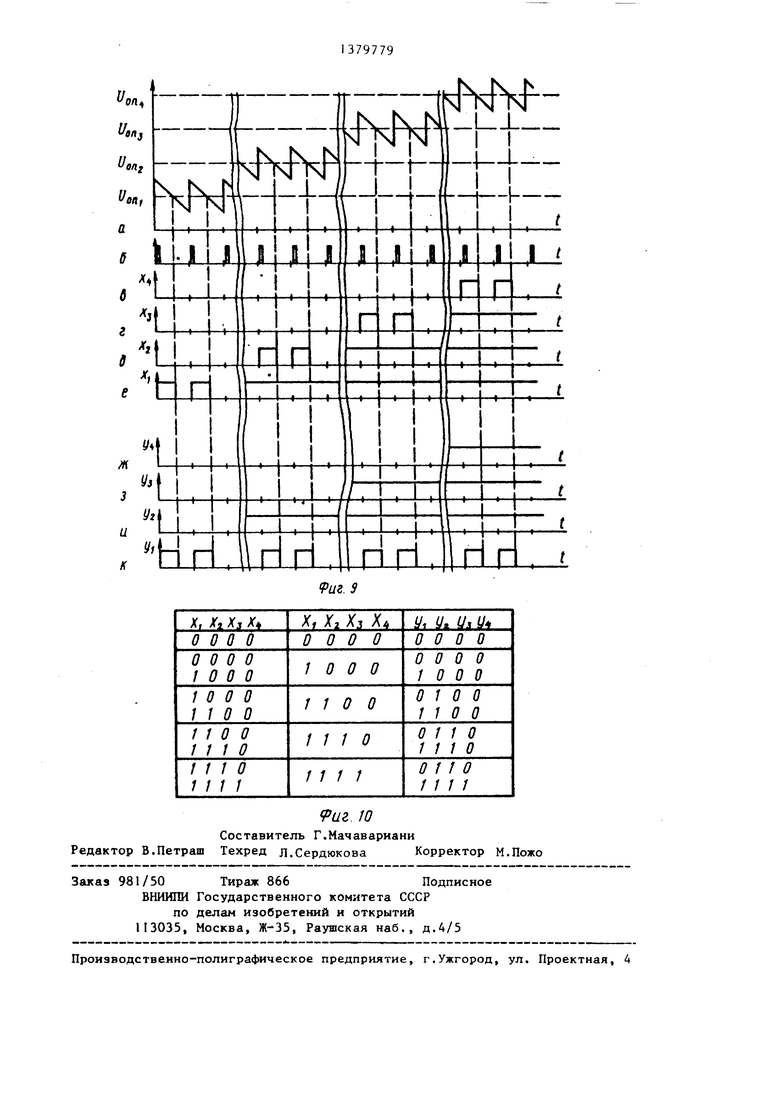

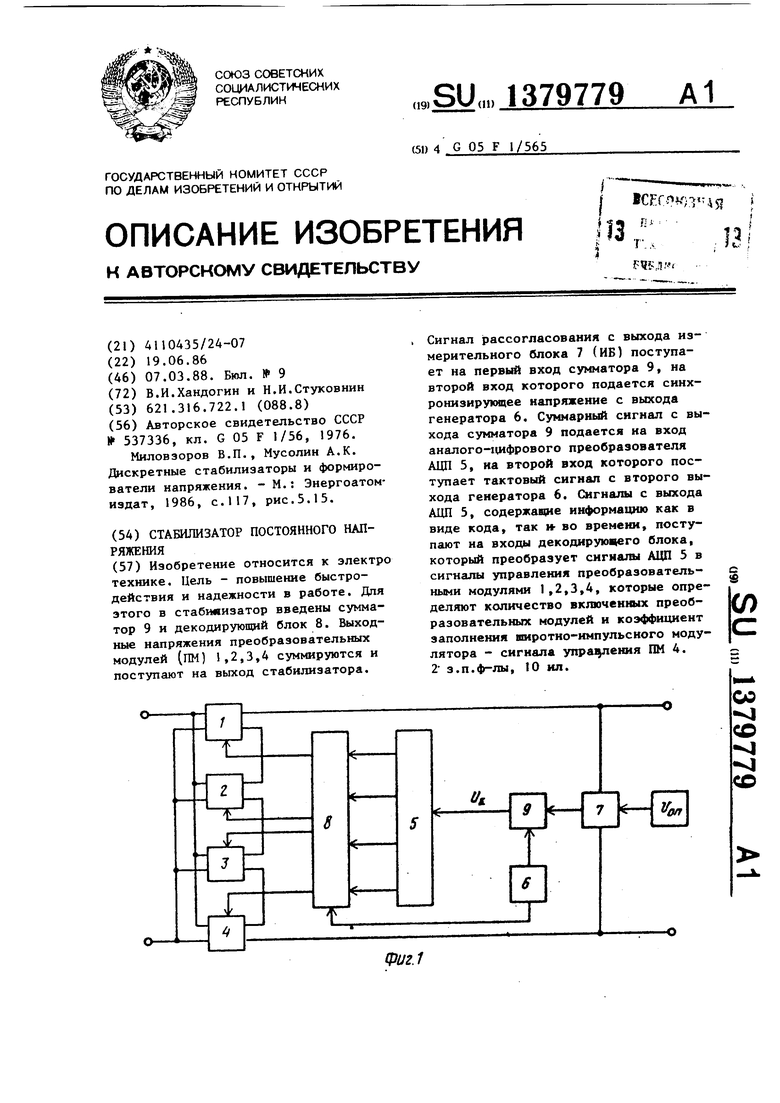

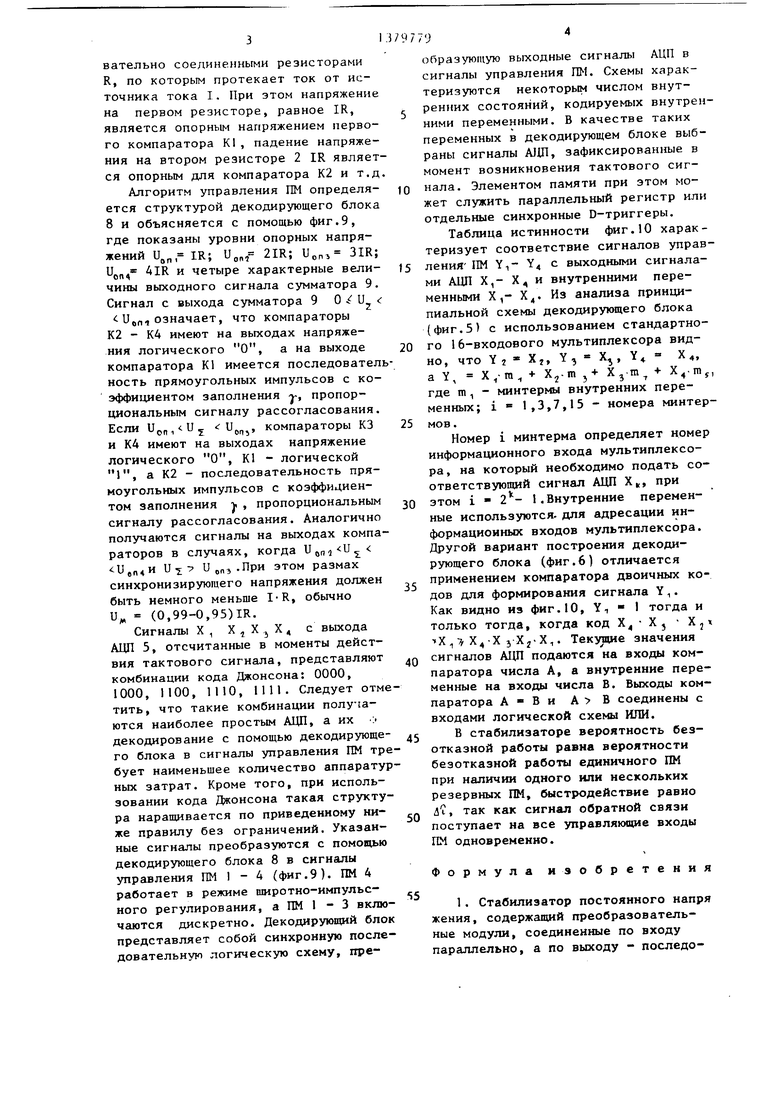

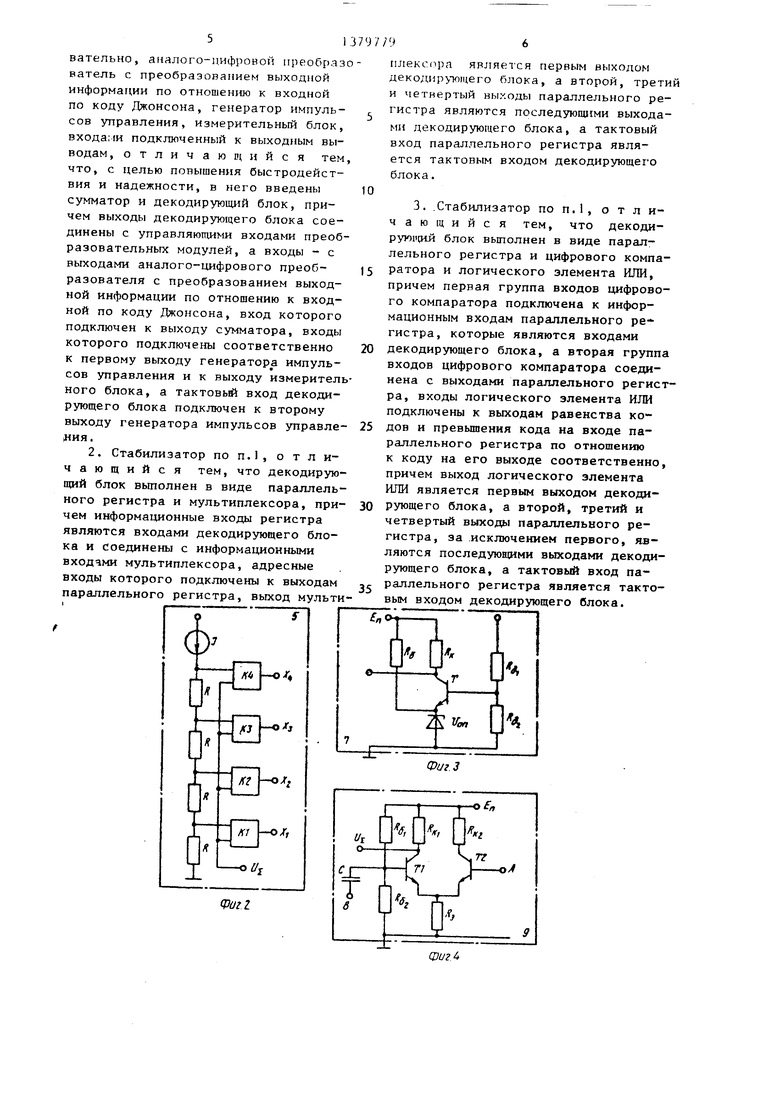

На фиг.1 представлена структурная схема стабилизатора постоянного напряжения; на фиг.2 - схема аналого-цифрового преобразователя с преобразованием выходной информации по отношению к входной по коду Джонсона; на фиг.З - схема измерительного блока; на фиг.4 - схема сумматора; на фиг.З - схема декодирующего блока на параллельном регистре и мультиплексоре; на фиг.6 - то же, на параллельном регистре, цифровом компараторе и логической схеме ИЛИ; на фиг.7 - преобразовательный модуль для реализации двух состояний включено-выключено; на фиг. 8 - то же, дня управления широтно-импульсным модулятором ШИМ-сигналов; на фиг.9 - эпюры, поясняющие работу устройства; на фиг.10 - таблица соответствия входных и выходных сигналов декодирующего блока.

Стабилизатор содержит преобразовательные модули (ПМ) 1-4 постоянного напряжения в постоянное с управляющими входами, аналого-цифровой преобразователь (АЦП) 5 с преобразованием выходной информации по отношению к входной по коду Джонсона, ге- иератор 6 импульсов управления (ГНУ) и измерительный блок (ИБ) 7, причем ПМ 1 - 4 по входу соединены параллельно, а по выходу последовательно. Декодирующий блок 8 выходами соединен с управляющими входами ПМ I - 4, а входами подключен к выходам АЦП 5, вход которого соединен с выходом сумматора 9, входы последнего с выходами ГНУ 6 и ИБ 7. Тактовый вход декодирующего блока 8 подключен к выходу ГНУ 6.

ПМ состоит из ключа 10, задающего генератора 11, усилителя 12 мощности, вьтрямителя 13, фильтра 14. Дпя управления НИМ-сигналом после ключа 10 устанавливается LCD-фильтр 15.

Стабилизатор работает следующим образом.

При подаче на вход стабилизатора постоянного напряжения начинают работать ПМ 1 - 4. Модули 1 - 3 (фиг.7)

Г

5

0

содержат последовательно соединенные управляющий ключ 10, задающий генератор 11, усилитель 12 мощности, вьшря- митель 13 и фильтр 14. База управляющего ключа 10 является управляющим входом ПМ 1 - 3. ПМ 4 (фиг.8) отличается от наличия LCD-фильтра 15 между управляющим ключом 10 и остальными элементами ПМ. Благодаря этому ПМ 4 может управляться 111ИМ-сигналом. Выходные напряжения Ш благодаря последовательному соединению их выходов суммируются и поступают на вход стабилизатора. ИБ 7 (фиг.З), формирует на выходе сигнал рассогласования между выходным и опорным напряжениями.

Сигнал рассогласования с выхода

0 ИБ 7 поступает на первый вход сумматора 9, на второй вход которого подается синхронизирующее напряжение с первого выхода ГНУ 6. Согласно одному из возможных вариантов построения сумматор 9 (фиг.4) является дифференциальным усилителем, причем вход А используется для подачи сигнала рассогласования, а вход В - для сигнала синхронизации. Суммарный сиг нал с выхода сумматора 9 подается на вход А1ДП 5, на второй вход поступает тактовый сигнал с второго выхода ГИУ 6. Синхронизирующее напряжение ГИУ 6 может быть симметричным

5 и несимметричным пилообразным, а также экспоненциальным с приемлемой кривизной. Тактовый сигнал представляет собой последовательность прямоугольных импульсов той же частоты, что и частота синхронизирующего напряжения, имеющую постоянную фазовую задержку Ц относительно последнего , необходимую для нормальной работы АЦП 5.

Сигналы с выхода АЦП 5, содержащие информацию как в виде кода, так и во времени, поступают на входы декодирующего блока 8. Он преобразовывает сигналы АЦП 5 в сигналы

0 управления ПМ I - 4, которые определяют количество включенных Ш 1 - 3 и коэффициент заполнения ШИМ-сигнала управления ПМ 4. Таким образом замыкается обратная связь.

АЦП 5 (фиг.2) состоит из четырех компараторов напряжения, первые входы которых соединены вместе и образуют вход АЦП 5. Другие входы компараторов соединены с последо0

5

55

3

вательно соединенными резисторами R, по которым протекает ток от источника тока I. При этом напряжение на первом резисторе, равное IR, является опорным напряжением первого компаратора К1, падение напряжения на втором резисторе 2 IR является опорным для компаратора К2 и т.д Алгоритм управления ПМ определяется структурой декодирующего блока 8 и объясняется с помощью фиг.9, где показаны уровни опорных напря- жений и„„, 1R; и„„, 2IR; и„,, 3IR; и,,„, 4IR и четыре характерные величины выходного сигнала сумматора 9. Сигнал с выхода сумматора 9 О U : Ujn,означает, что компараторы К2 - К4 имеют на выходах напряжения логического О, а на выходе компаратора К1 имеется последовательность прямоугольных импульсов с коэффициентом заполнения , пропорциональным сигналу рассогласования. Если Uon,Uj Uooi компараторы КЗ и К4 имеют на выходах напряжение логического О, К1 - логической 1, а К2 - последовательность прямоугольных импульсов с коэффициентом заполнения , пропорциональным сигналу рассогласования. Аналогично получаются сигналы на выходах компараторов в случаях, когда Ujn и : и опз-При этом размах синхронизирующего напряжения должен быть немного меньще I-R, обычно и (0,99-0,95)IR.

Сигналы X , X X , X д с выхода АЦП 5, отсчитанные в моменты действия тактового сигнала, представляют комбинации кода Джонсона: 0000, 1000, 1100, 1110, 1111. Следует отметить, что такие комбинации получаются наиболее простым АЦП, а их : декодирование с помощью декодирующего блока в сигналы управления ПМ требует наименьшее количество аппаратурных затрат. Кроме того, при использовании кода Джонсона такая структура наращивается по приведенному ниже правилу без ограничений. Указанные сигналы преобразуются с помощью декодирующего блока 8 в сигналы управления ПМ 1 - 4 (фиг.9). ПМ 4 работает в режиме широтно-импульс- ного регулирования, а ПМ 1 - 3 вклю- чгиотся дискретно. Декодирующий блок представляет собой синхронную последовательную логическую схему, пре/9779

образующую выходные сигналы АЦП в сигналы управления ПМ. Схемы характеризуются некоторым числом внут- , ранних состояний, кодируемых внутренними переменными. В качестве таких переменных в декодирующем блоке выбраны сигналы , зафиксированные в момент возникновения тактового сиг- 10 нала. Элементом памяти при этом может служить параллельный регистр или отдельные синхронные D-триггеры.

Таблица истинности фиг.10 характеризует соответствие сигналов управ- t5 ления ПМ YI- Уд с выходными сигналами АЦП X,- Х и внутренними переменными X,- X/. Из анализа принципиальной схемы декодирующего блока (фиг.5) с использованием стандартно- 0 го 16-входового мультиплексора видно, что YI - Хг, Y, Х, Y X 4, а Y, Х, Xj-m, , где m - минтермы внутренних переменных; i 1,3,7,15 - номера минтер- 5 мов.

Номер i минтерма определяет номер информационного входа мультиплексора, на который необходимо подать соответствующий сигнал АЦП Х, при 0 этом i - 1.Внутренние переменные используются, для адресации ин- формациоиных входов мультиплексора. Другой вариант построения декодирующего блока (фиг.6) отличается применением компаратора двоичных кодов для формирования сигнала Y,. Как видно из фиг. 10, Y, I тогда и только тогда, когда код Х Х, Xjx X } ,. Текутцие значения Q сигналов АЦП подаются на входы компаратора числа А, а внутренние переменные на входы числа В. Выходы компаратора А В и А В соединены с входами логической схемы ИЛИ. 5 В стабилизаторе вероятность безотказной работы равна вероятности безотказной работы единичного ПМ при наличии одного или нескольких резервных ПМ, быст1Х}действие равно Q d, так как сигнал обратной связи поступает на все управляющие входы ПМ одновременно.

5

Формула изобретения

1. Стабилизатор постоянного напря жения, содержащий преобразовательные модули, соединенные по входу параллельно, а по выходу - последе51

вательно, аналого-цифровой преобг)азо ватель с преобразованием выходной информации по отношению к входной по коду Джонсона, генератор импуль- сов управления, измерительный блок, входами подключенный к выходным выводам, отличаю DI и йся тем, что, с целью повышения быстродействия и надежности, в него введены сумматор и декодирующий блок, причем выходы декодирующего блока соединены с управляюпшми входами преобразовательных модулей, а входы - с выходами аналого-цифрового преоб- разователя с преобразованием выходной информации по отношению к входной по коду Джонсона, вход которого подключен к выходу сумматора, входы которого подключены соответственно к первому вьпсоду генератора импульсов управления и к выходу измерительного блока, а тактовьй вход декодирующего блока подключен к второму выходу генератора импульсов управле- ия.

2. Стабилизатор по п.1, о т л и- чающийся тем, что декодирующий блок вьшолнен в виде параллельного регистра и мультиплексора, при- чем информационные входы регистра являются входами декодирующего блока и соединены с информационными входами мультиплексора, адресные входы которого подключены к выходам

параллельного регистра, выход мультиплексгтра ярляется первым выходом декодирующего блока, а второй, третий и четвертый выходы параллельного регистра являются последующими выходами декодирующего блока, а тактовый вход параллельного регистра является тактовым входом декодирующего блока.

3. .Стабилизатор по п.1, отличающийся тем, что декоди- рую11(ий блок выполнен в виде параллельного регистра и цифрового компаратора и логического элемента ИЛИ, причем первая группа входов цифрового компаратора подключена к информационным входам параллельного регистра, которые являются входами декодирующего блока, а вторая группа входов цифрового компаратора соединена с выходами параллельного регистра, входы логического элемента ИЛИ подключены к выходам равенства кодов и превышения кода на входе параллельного регистра по отношению к коду на его выходе соответственно, причем выход логического элемента ИЛИ является первым выходом декодирующего блока, а второй, третий и четвертый выходы параллельного регистра, за исключением первого, являются последуюЕцими выходами декодирующего блока, а тактовый вход параллельного регистра является тактовым входом декодирующего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ импульсной стабилизации напряжения на нагрузке | 2024 |

|

RU2824473C1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ | 2002 |

|

RU2229157C2 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство для измерения динамической погрешности аналого-цифровых преобразователей | 1984 |

|

SU1221749A1 |

| Ключевой стабилизатор | 1984 |

|

SU1372314A1 |

| Устройство для измерения параметров магнитного поля | 2018 |

|

RU2696058C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

Изобретение относится к электро технике. Цель - повышение быстродействия и надежности в работе. Для этого в стабилизатор введены сумматор 9 и декодирующий блок 8. Выходные напряжения преобразовательных модулей (им) 1,2,3,4 суммируются и поступают на выход стабилизатора. Сигнал рассогласования с выхода измерительного блока 7 (ИБ) поступает на первый вход сумматора 9, на второй вход которого подается синхронизирующее напряжение с выхода генератора 6. Суммарный сигнал с выхода сумматора 9 подается на вход аналого-1Щфрового преобразователя АЦП 5, иа второй вход которого поступает тактовый сигнал с второго выхода генератора 6. Сигналы с выхода АЦП 5, содержащие информацию как в виде кода, так и- во времени, поступают на входы декодирующего блока, который преобразует сигналы АЦП 5 в сигналы управления преобразовательными модулями 1,2,3,4, которые определяют количество включенных преобразовательных модулей и коэффициент заполнения юиротно-импульсного модулятора - сигнала упра1}лекия ПМ 4. 2 з.п.ф-лы, 10 ил. (О

Puzt

Р

-±Фиг.З

и

а б

ont

д J

и

Уг 1

| Способ программного регулирования постоянного напряжения | 1975 |

|

SU537336A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Миловзоров в.п., Мусолин А.К | |||

| Дискретные стабилизаторы и формирователи напряжения | |||

| - М.: Энергоатом- иэдат, 1986, с.117, рис.5.15. | |||

Авторы

Даты

1988-03-07—Публикация

1986-06-19—Подача