Фие.;

Изобретение относится к автоматике и вычислительной технике, а именно к устройстпам, контроля работоспособности и поиска дефектов дискретных узлов и блоков.

Цель изобретения - повышение быстродействия устройства.

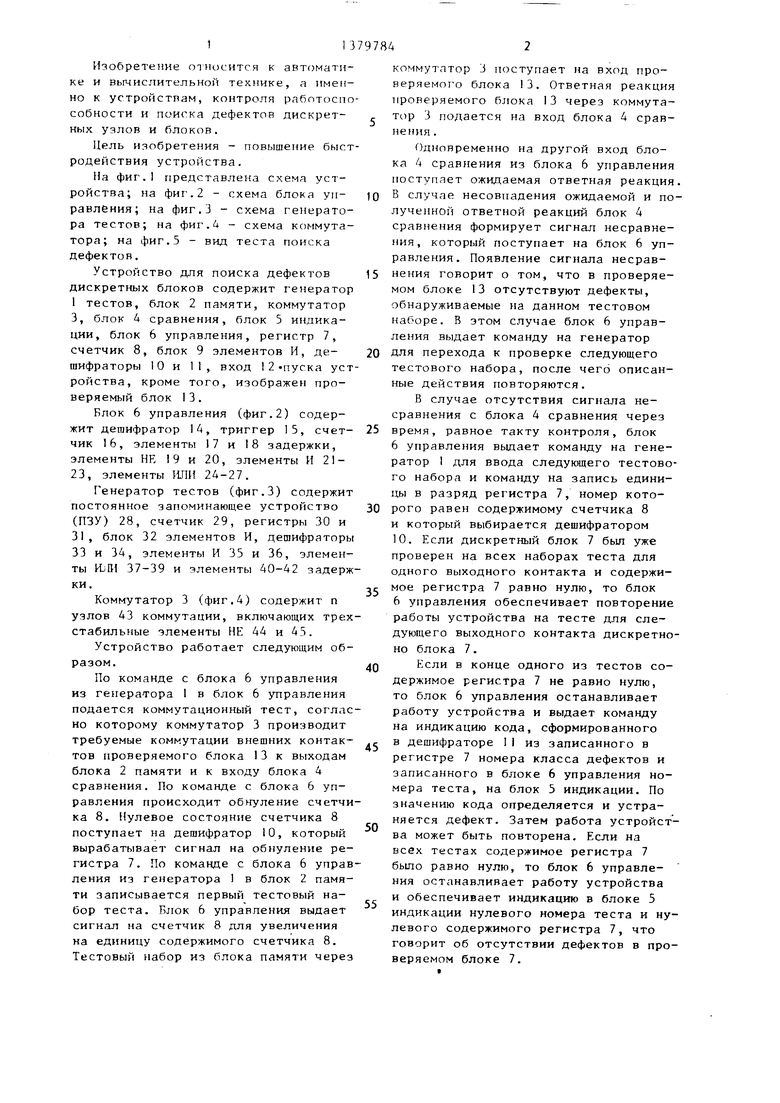

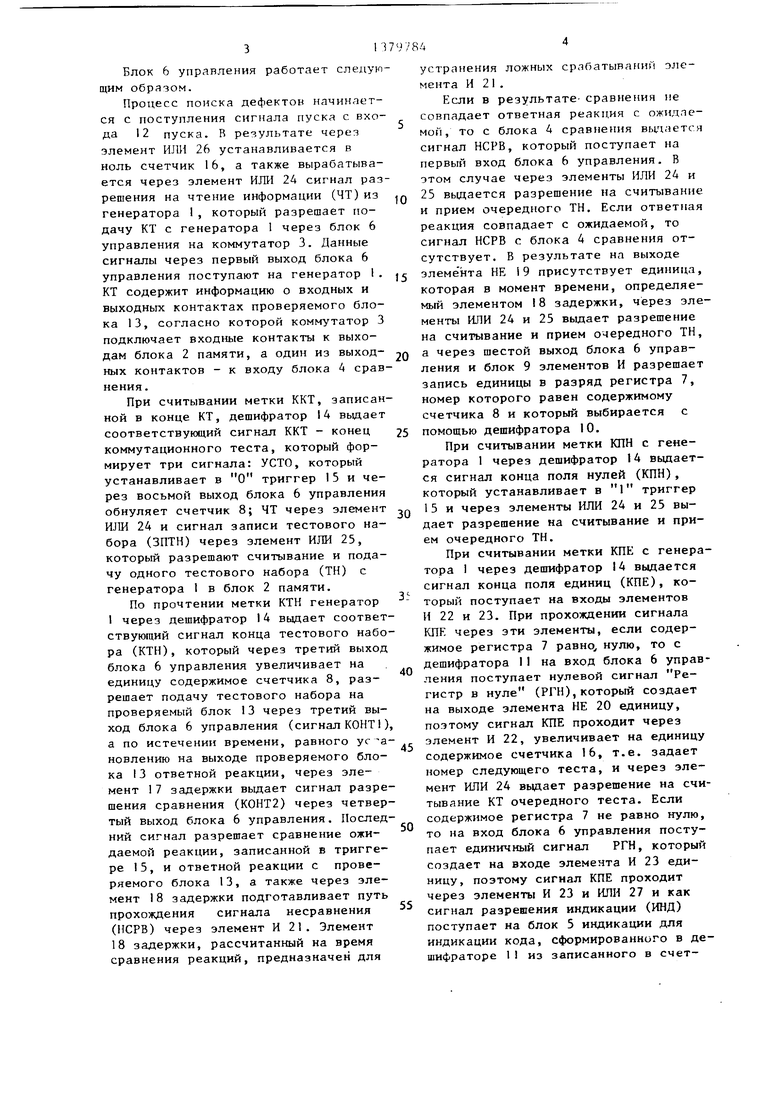

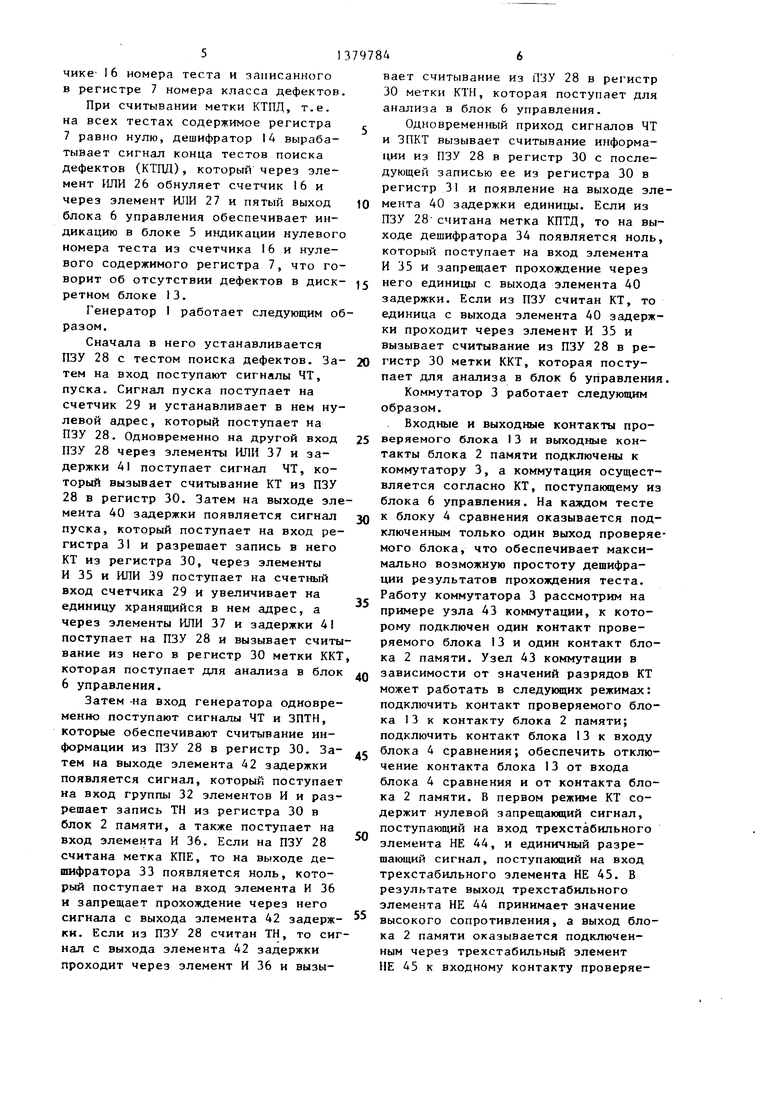

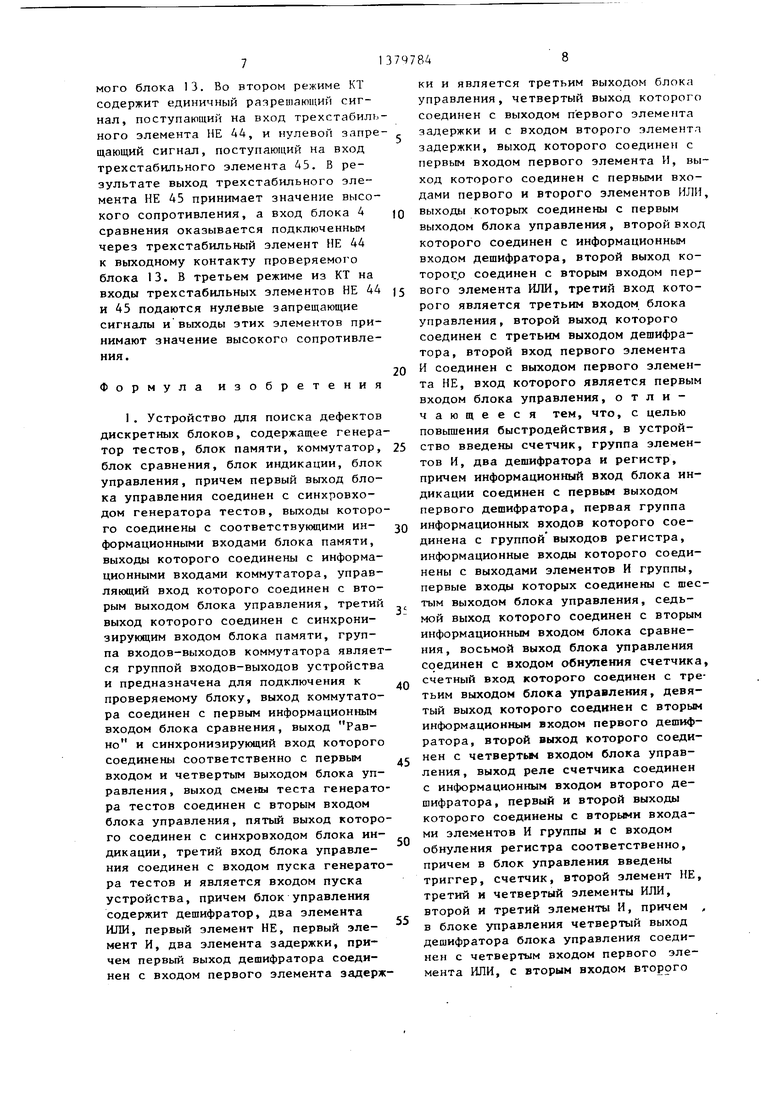

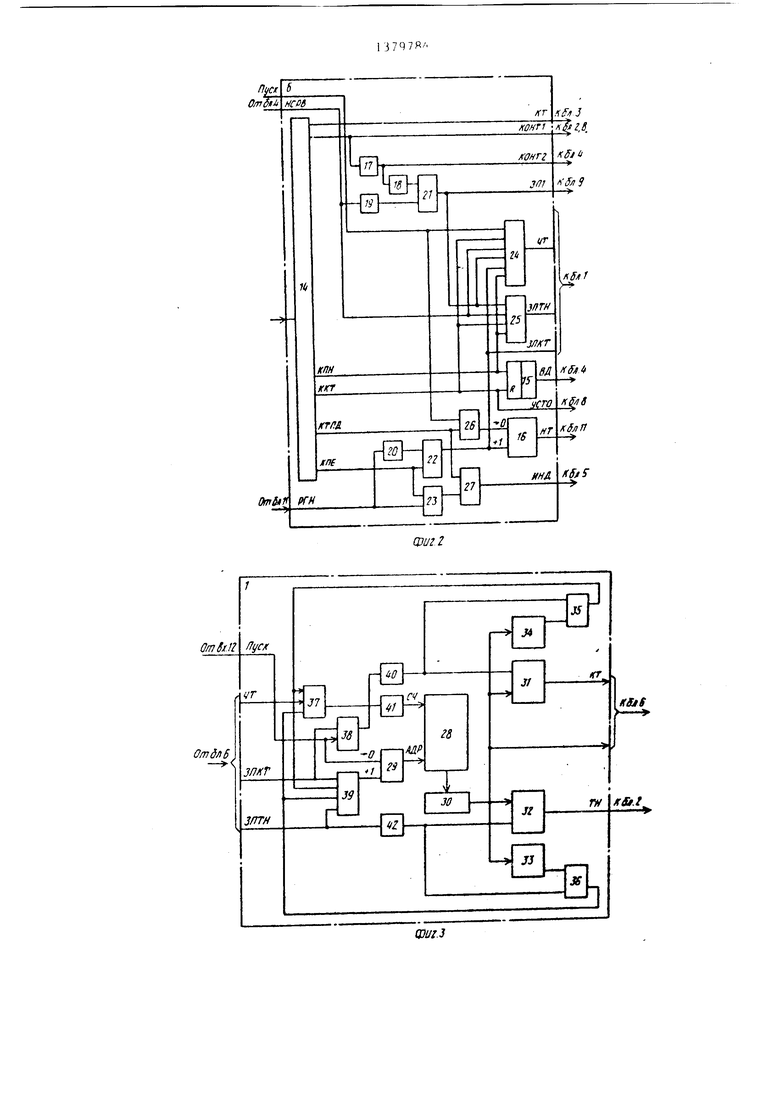

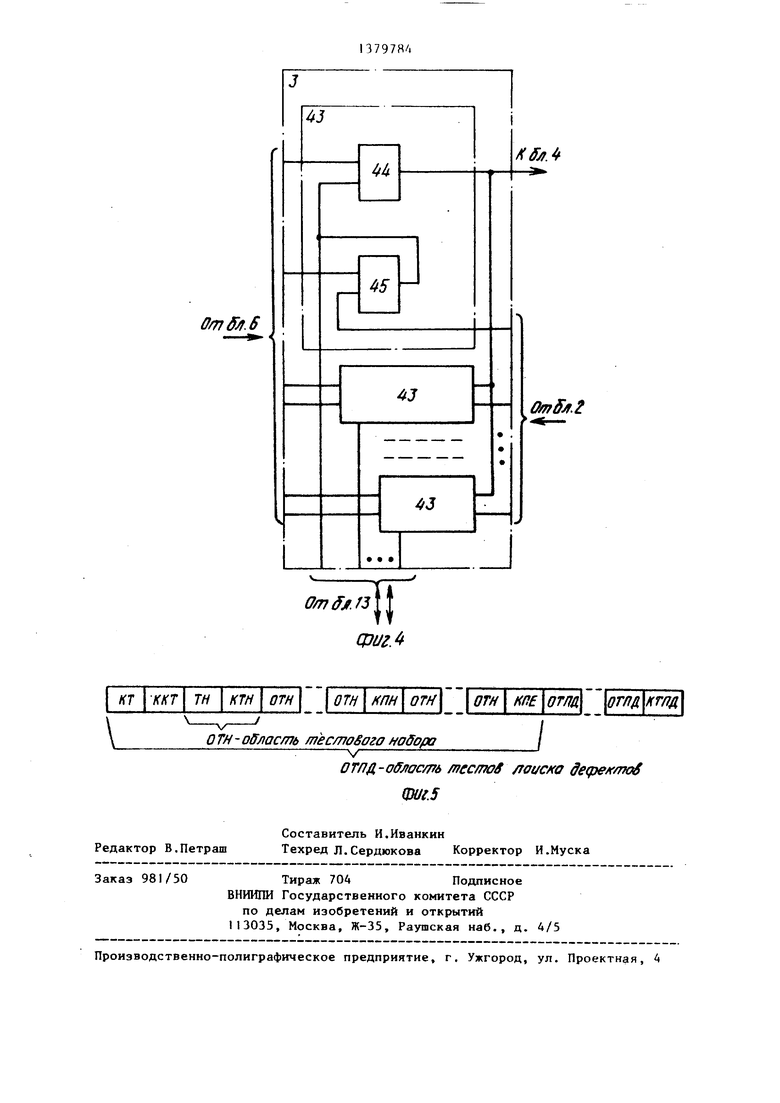

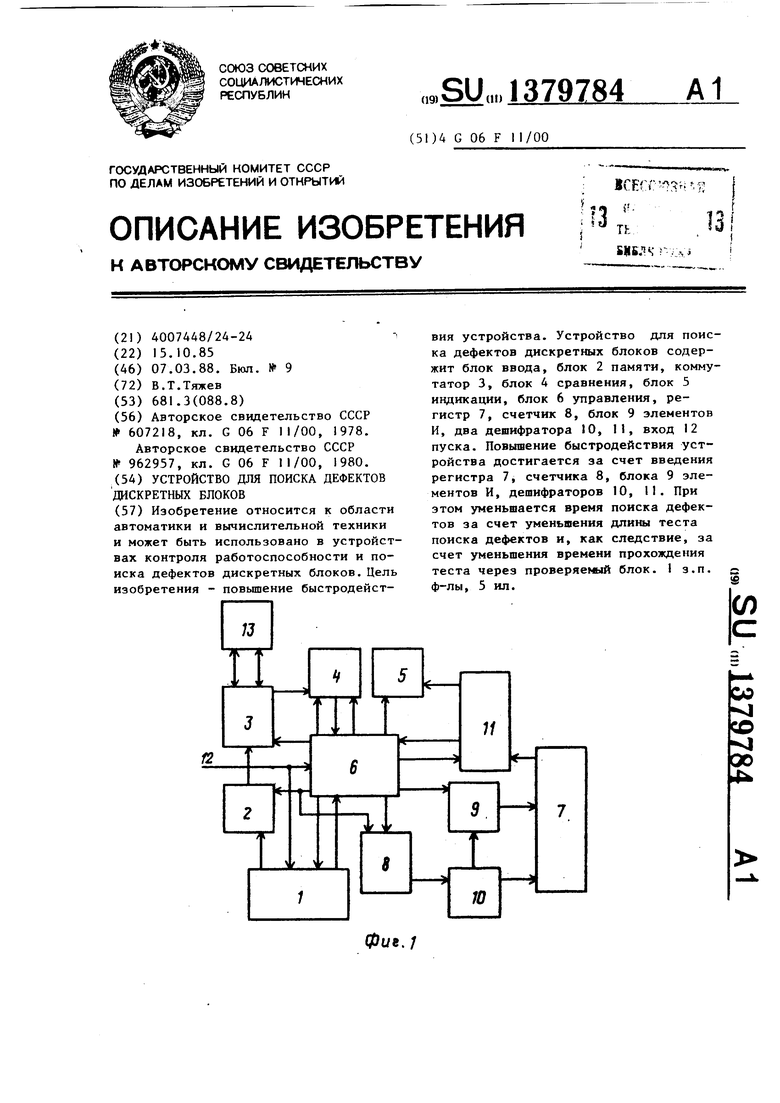

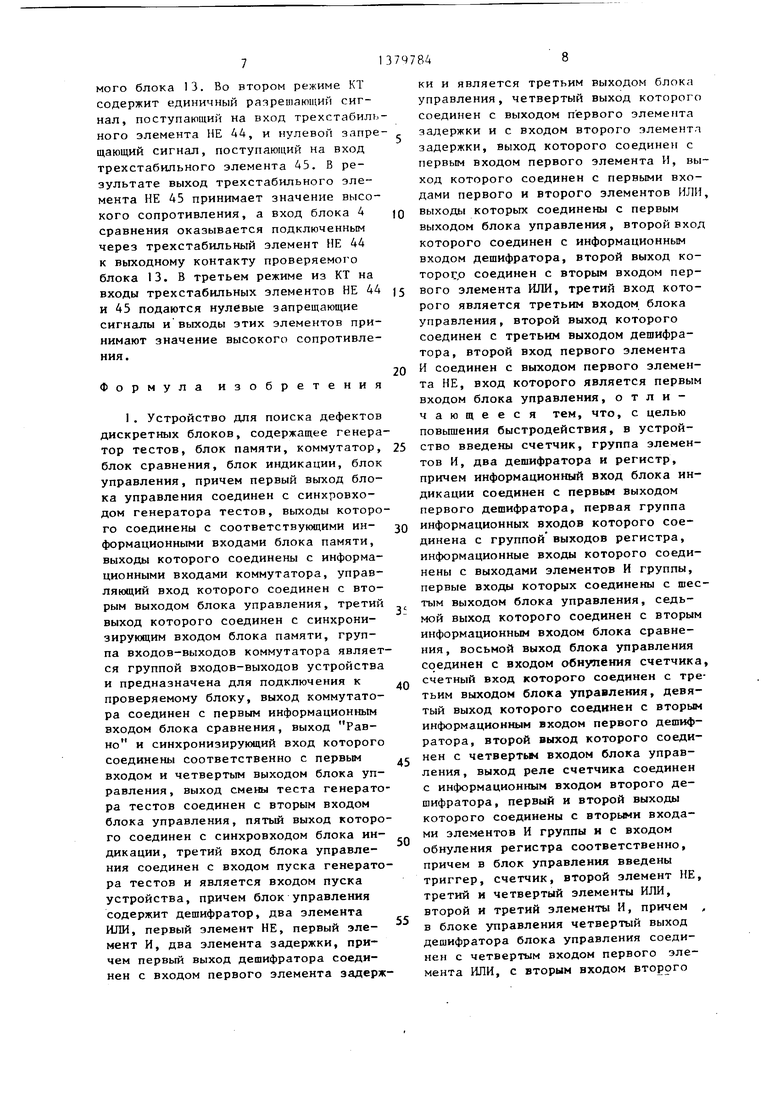

На фиг.1 представлена схема устройства; на фиг.2 - схема блока управления; на фиг.3 - схема генератора тестов; на фиг.4 - схема коммутатора; на фиг.5 - вид теста поиска дефектов.

Устройство для поиска дефектов дискретных блоков содержит генератор 1 тестов, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, блок 6 управления, регистр 7, счетчик 8, блок 9 элементов И, дешифраторы 10 и 11, вход I2«пуска устройства, кроме того, изображен проверяемый блок 13.

Блок 6 управления (фиг.2) содержит дешифратор 14, триггер 15, счетчик 16, элементы 17 и 18 задержки, элементы НЕ 19 и 20, элементы И 21- 23, элементы ИЛИ 24-27.

Генератор тестов (фиг.З) содержит постоянное запоминающее устройство (ПЗУ) 28, счетчик 29, регистры 30 и 31, блок 32 элементов И, дешифраторы 33 и 34, элементы И 35 и 36, элементы HjIH 37-39 и элементы 40-42 задержки.

Коммутатор 3 (фиг.4) содержит п узлов 43 коммутации, включающих трех стабильные элементы НЕ 44 и 45.

Устройство работает следующим образом.

По команде с блока 6 управления из генератора 1 в блок 6 управления подается коммутационный тест, согласно которому коммутатор 3 производит требуемые коммутации внешних контактов проверяемого блока 13 к выходам блока 2 памяти и к входу блока 4 сравнения. По команде с блока 6 управления происходит обнуление счетчика 8. Кулевое состояние счетчика 8 поступает на дешифратор 10, который вырабатывает сигнал на обнуление регистра 7. По команде с блока 6 управления из генератора 1 в блок 2 памяти записывается первый тестовый набор теста. Блок 6 управления выдает сигнал на счетчик В для увеличения на единицу содержимого счетчика 8. Тестовый набор из блока памяти через

5

0

5

0

5

0

5

0

5

коммутатор 3 поступает на вход проверяемого блока 13. Ответная реакция проверяемого блока 13 через коммутатор 3 подается на вход блока 4 сравнения .

Одновременно на другой вход блока 4 сравнения из блока 6 управления поступает ожидаемая ответная реакция. В случае несовпадения ожидаемой и полученной ответной реакций блок 4 сравнения формирует сигнал несравнения, который поступает на блок 6 управления. Появление сиг}1ала несравнения говорит о том, что в проверяемом блоке 13 отсутствуют дефекты, обнаруживаемые на данном тестовом наборе. В этом случае блок 6 управления выдает команду на генератор для перехода к проверке следующего тестового набора, после чего описанные действия повторяются.

В случае отсутствия сигнала несравнения с блока 4 сравнения через время, равное такту контроля, блок 6 управления выдает команду на генератор 1 для ввода следующего тестового набора и команду на запись единицы в разряд регистра 7, номер которого равен содержимому счетчика 8 и который выбирается дешифратором 10. Если дискретный блок 7 был уже проверен на всех наборах теста для одного выходного контакта и содержимое регистра 7 равно нулю, то блок 6 управления обеспечивает повторение работы устройства на тесте для следующего выходного контакта дискретно- но блока 7.

Если в конце одного из тестов содержимое регистра 7 не равно нулю, то блок 6 управления останавливает работу устройства и выдает команду на индикацию кода, сформированного в дешифраторе 1I из записанного в регистре 7 номера класса дефектов и записанного в блоке 6 управления номера теста, на блок 5 индикации. По значению кода определяется и устраняется дефект. Затем работа устройства может быть повторена. Если на всех тестах содержимое регистра 7 было равно нулю, то блок 6 управления останавливает работу устройства и обеспечивает индикацию в блоке 5 индикации нулевого номера теста и кулевого содержимого регистра 7, что говорит об отсутствии дефектов в проверяемом блоке 7.

31

Блок 6 управления работает следующим образом.

Процесс поиска дефектов начинается с поступления сигнала пуска с входа 12 пуска. В результате через элемент ИЛИ 26 устанавливается в ноль счетчик 16, а также вырабатывается через элемент ИЛИ 24 сигнал разрешения на чтение информации (ЧТ)из генератора 1, который разрешает подачу КТ с генератора 1 через блок 6 управления на коммутатор 3. Данные сигналы через первый выход блока 6 управления поступают на генератор 1. КТ содержит информацию о входных и выходных контактах проверяемого блока 13, согласно которой коммутатор 3 подключает входные контакты к выходам блока 2 памяти, а один из выход- ных контактов - к входу блока 4 сравнения .

При считывании метки ККТ, записанной в конце КТ, дешифратор 14 выдает соответствующий сигнал ККТ - конец коммутационного теста, который формирует три сигнала: УСТО, который устанавливает в О триггер 15 и через восьмой выход блока 6 управления обнуляет счетчик 8; ЧТ через элемент ИЛИ 24 и сигнал записи тестового набора (ЗПТН) через элемент ИЛИ 25, который разрешают считывание и подачу одного тестового набора (ТН) с генератора 1 в блок 2 памяти.

По прочтении метки КТН генератор I через дешифратор I4 выдает соответствующий сигнал конца тестового набора (КТН), который через третий выход блока 6 управления увеличивает на единицу содержимое счетчика 8, разрешает подачу тестового набора на проверяемый блок 13 через третий выход блока 6 управления (сигнал КОНТ1) а по истечении времени, равного новлению на выходе проверяемого блока 13 ответной реакции, через элемент 17 задержки выдает сигнал разрешения сравнения (КОНТ2) через четвертый Выход блока 6 управления. Последний сигнал разрешает сравнение ожидаемой реакции, записанной в триггере 15, и ответной реакции с проверяемого блока 13, а также через элемент 18 задержки подготавливает путь прохождения сигнала несравнения (ИСРВ) через элемент И 21. Элемент 18 задержки, рассчитанный на время сравнения реакций, предназначен для

.Q |г JQ

25 OQ

-

40

45

0

844

устранения ложных срабатывар1ий элемента И 2 1 .

Если в результате сравнения не совпадает ответная реакция с ожидаемой, то с блока 4 сравнения вы,ч чется сигнал НСРВ, который поступает на первый вход блока 6 управления. В этом случае через элементы ИЛИ 24 и 25 вьщается разрешение на считывание и прием очередного ТН. Если ответная реакция совпадает с ожидаемой, то сигнал НСРВ с блока 4 сравнения отсутствует. В результате на выходе элеме нта НЕ 19 присутствует единица, которая в момент времени, определяемый элементом 18 задержки, через элементы ИЛИ 24 и 25 вьщает разрешение на считывание и прием очередного ТН, а через шестой выход блока 6 управления и блок 9 элементов И разрешает запись единицы в разряд регистра 7, номер которого равен содержимому счетчика 8 и который выбирается с помощью дешифратора 10.

При считывании метки КПН с генератора 1 через дешифратор 14 вьщает- ся сигнал конца поля нулей (КПН), который устанавливает в 1 триггер 15 и через элементы ИЛИ 24 и 25 выдает разрешение на считывание и прием очередного ТН.

При считывании метки КПЕ с генератора 1 через дешифратор 14 выдается сигнал конца поля единиц (КПЕ), который поступает на входы элементов И 22 и 23. При прохождении сигнала КПЕ через эти элементы, если содержимое регистра 7 равнр, нулю, то с дешифратора I1 на вход блока 6 управления поступает нулевой сигнал Регистр в иуле (РГН), который создает на выходе элемента НЕ 20 единицу, поэтому сигнал КПЕ проходит через элемент И 22, увеличивает на единицу содержимое счетчика 16, т.е. задает номер следующего теста, и через элемент ИЛИ 24 выдает разрешение на считывание КТ очередного теста. Если содержимое регистра 7 не равно нулю, то на вход блока 6 управления поступает единичный сигнал РГН, который создает на входе элемента И 23 единицу, поэтому сигнал КПЕ проходит через элементы И 23 и ИЛИ 27 и как сигнал разрешения индикации (ИНД) поступает на блок 5 индикации для индикации кода, сформированного в дешифраторе 11 из записанного в счетчике 16 номера теста и записанного в регистре 7 номера класса дефектов.

При считывании метки КТПД, т.е. на всех тестах содержимое регистра 7 равно нулю, дешифратор 14 вырабатывает сигнал конца тестов поиска дефектов (КТПД), который через элемент ИЛИ 26 обнуляет счетчик 16 и через элемент ИЛИ 27 и пятый выход блока 6 управления обеспечивает индикацию в блоке 5 индикации нулевого номера теста из счетчика 16 и нулевого содержимого регистра 7, что говорит об отсутствии дефектов в дискретном блоке 13.

Генератор 1 работает следующим образом.

Сначала в него устанавливается ПЗУ 28 с тестом поиска дефектов. Затем на вход поступают сигналы ЧТ, пуска. Сигнал пуска поступает на счетчик 29 и устанавливает в нем нулевой адрес, который поступает на ПЗУ 28. Одновременно на другой вход ПЗУ 28 через элементы ИЛИ 37 и задержки 41 поступает сигнал ЧТ, который вызывает считывание КТ из ПЗУ 28 в регистр 30. Затем на выходе элемента 40 задержки появляется сигнал пуска, который поступает на вход регистра 31 и разрешает запись в него КТ из регистра 30, через элементы И 35 и ИЛИ 39 поступает на счетный вход счетчика 29 и увеличивает на единицу хранящийся в нем адрес, а через элементы ИЛИ 37 и задержки 41 поступает на ПЗУ 28 и вызывает считывание из него в регистр 30 метки ККТ которая поступает для анализа в блок 6 управления.

Затем -на вход генератора одновременно поступают сигналы ЧТ и ЗПТН, которые обеспечивают считывание информации из ПЗУ 28 в регистр 30. Затем на выходе элемента 42 задержки появляется сигнал, который поступает на вход группы 32 элементов И и разрешает запись ТН из регистра 30 в блок 2 памяти, а также поступает на вход элемента И 36. Если на ПЗУ 28 считана метка КПЕ, то на выходе дешифратора 33 появляется ноль, который поступает на вход элемента И 36 и запрещает прохождение через него сигнала с выхода элемента 42 задержки. Если из ПЗУ 28 считан ТН, то сигнал с выхода элемента 42 задержки проходит через элемент И 36 и вызы

5

0

5

0

5

0

5

0

5

вает считывание из ПЗУ 28 в регистр 30 метки КТН, которая поступает для анализа в блок 6 управления.

Одновременный приход сигналов ЧТ и ЗПКТ вызывает считывание информации из ПЗУ 28 в регистр 30 с последующей записью ее из регистра 30 в регистр 31 и появление на выходе элемента 40 задержки единицы. Если из ПЗУ 28 считана метка КПТД, то на выходе дешифратора 34 появляется ноль, который поступает на вход элемента И 35 и запрещает прохождение через него единицы с выхода элемента 40 задержки. Если из ПЗУ считан КТ, то единица с выхода элемента 40 задержки проходит через элемент И 35 и вызывает считывание из ПЗУ 28 в регистр 30 метки ККТ, которая поступает для анализа в блок 6 управления.

Коммутатор 3 работает следующим образом.

Входные и выходные контакты проверяемого блока I3 и выходные контакты блока 2 памяти подключены к коммутатору 3, а коммутация осуществляется согласно КТ, поступающему из блока 6 управления. На каждом тесте к блоку 4 сравнения оказывается подключенным только один выход проверяемого блока, что обеспечивает максимально возможную простоту дешифрации результатов прохождения теста. Работу коммутатора 3 рассмотрим на примере узла 43 коммутации, к которому подключен один контакт проверяемого блока 13 и один контакт блока 2 памяти. Узел 43 коммутации в зависимости от значений разрядов КТ может работать в следующих режимах: подключить контакт проверяемого блока 1 3 к контакту блока 2 памяти; подключить контакт блока 13 к входу блока 4 сравнения; обеспечить отключение контакта блока 13 от входа блока 4 сравнения и от контакта блока 2 памяти. В первом режиме КТ содержит нулевой запрещающий сигнал, поступающий на вход трехстабильного элемента НЕ 44, и единичный разрешающий сигнал, поступающий на вход трехстабильного элемента НЕ 45. В результате выход трехстабильного элемента НЕ 44 принимает значение высокого сопротивления, а выход блока 2 памяти оказывается подключенным через трехстабильный элемент НЕ 45 к входному контакту проверяемого блока 13. Во втором режиме КТ содержит единичный разрешающий сигнал, поступающий на вход трехстабиль ного элемента НЕ 44, и нулевой запре щающий сигнал, поступающий на вход трехстабильного элемента 45. В результате выход трехстабильного элемента НЕ 45 принимает значение высокого сопротивления, а вход блока 4 сравнения оказывается подключенным через трехстабильный элемент НЕ 44 к выходному контакту проверяемого блока 13. В третьем режиме из КТ на входы трехстабильных элементов НЕ 44 и 45 подаются нулевые запрещающие сигналы и выходы этих элементов принимают зиачеине высокого сопротивления.

Формула изобретения

1. Устройство для поиска дефектов дискретных блоков, содержащее генератор тестов, блок памяти, коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход блока управления соединен с синхровхо- дом генератора тестов, выходы которого соединены с соответствующими ин- формациониыми входами блока памяти, выходы которого соединены с информационными входами коммутатора, управляющий вход которого соединен с вторым выходом блока управления, третий выход которого соединен с синхронизирующим входом блока памяти, группа входов-выходов коммутатора является группой входов-выходов устройства

и предназначена для подключения к проверяемому блоку, выход коммутатора соединен с первым информационным входом блока сравнения, выход Равно и синхронизирующий вход которого соединены соответственно с первым входом и четвертым выходом блока управления, выход смены теста генератора тестов соединен с вторым входом блока управления, пятый выход которого соединен с синхровходом блока индикации, третий вход блока управления соединен с входом пуска генератора тестов и является входом пуска устройства, причем блок управления содержит дешифратор, два элемента ИЛИ, первый элемент НЕ, первый элемент И, два элемента задержки, причем первый выход дешифратора соединен с входом первого элемента задержQ 5

0

5 о

0

5

0

5

ки и является третьим выходом блока управления, четвертый выход которого соединен с выходом первого элемента задержки и с входом второго элемента задержки, выход которого соединен с первым входом первого элемента И, выход которого соединен с первыми входами первого и второго элементов ИЛИ, выходы которых соединены с первым выходом блока управления, второй вход которого соединен с информационным входом дещифратора, второй выход которого соединен с вторым входом первого элемента ИЛИ, третий вход которого является третьим входом блока управления, второй выход которого соединен с третьим выходом дешифратора, второй вход первого элемента И соединен с выходом первого элемента НЕ, вход которого является первым входом блока управления, о т л и - чающееся тем, что, с целью повьпиеиия быстродействия, в устройство введены счетчик, группа элементов И, два дешифратора и регистр, причем информационный вход блока индикации соединен с первым выходом первого дешифратора, первая группа информационных входов которого соединена с группой выходов регистра, информационные входы которого соединены с выходами элементов И группы, первые входы которых соединены с шестым выходом блока управления, седьмой выход которого соедниеи с вторым информационным входом блока сравнения, восьмой выход блока управления соединен с входом обнуления счетчика, счетный вход которого соединен с третьим выходом блока управления, девятый выход которого соединеи с вторым информационным входом первого дешифратора, второй выход которого соединен с четвертые входом блока управления , выход реле счетчика соединен с информационным входом второго дешифратора , первый и второй выходы которого соединены с вторыми входами элементов И группы и с входом обнуления регистра соответственно, причем в блок управления введены триггер, счетчик, второй элемент НЕ, третий и четвертый элементы ИЛИ, второй и третий элементы И, причем , в блоке управления четвертый выход дешифратора блока управления соединен с четвертым входом первого элемента ИЛИ, с вторым входом второго

элемента ИЛИ и с нходом установки в 1 триггера, выход которого соединен с выходом бдока управления, восьмой выход которого соединен с входом установки в О триггера, с вторым входом первого :5демен- та ИЛИ и с третьим входом второго элемента ИЛИ, четвертый вход которого соединен с первым входом блока управления и с пятым входом первого элемента ИЛИ, шестой вход которого соединен с выходом второг о элемента И, со счетным входом счетчика и подключен к первому выходу блока управ- ления, девятый выход которого соединен с выходом счетчика, вход установки в О которого соединен с выходом третьего элемента ИЛИ, первый вход которого объединен с первым входом четвертого элемента ИЛИ и подключен к пятому выходу дешифратора, шестой выход которого соединен с первыми входами второго и третьего элементов И, второй вход второго элемента И соединен с выходом второго элемента НЕ, вход которого соединен с вторым входом третьего элемента И и с четвертым входом блока управления, выход третьего элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого является пятым выходом блока управления, девятый выход которого соединен с первым входом первого элемента ИЛИ, третий

вход которого соединен с вторым входом третьего элемента ИЛИ.

2. Устройство по п.1, о т л и - чающееся тем, что генератор тестов содержит постоянное запоминающее устройство, счетчик, два регистра, группу элементов И, два дешифратора, два элемента И, три элемента ИЛИ, три элемента задержки, причем информационные выходы генератора соединены с выходами элементов И группы.

Q

5

Q

первые входы которых соединены с информационными входами дешифраторов, с информационным входом первого регистра, с выходом второго регистра и подключены к выходу генератора, информационные входы второго регистра соединены с выходами постоянного запоминающего устройства, адресные входы которого соединены разрядными выходами счетчика, счетный вход которого соединен с выходом лервого элемента ИЛИ, первый вход которого объединен с первым входом второго элемента ИЛИ и является входом генератора для подключения к выходу второго элемента И блока управления, вход считывания постоянного запоминающего устройства соединен с выходом первого элемента задержки, вход которого соединен с выходом третьего элемента ИШ1, первый вход которого объединен с вторым входом первого элемента ИЛИ и подключен к выходу первого элемента И, первый вход которого соединен с входом записи первого регистра и с выходом второго элемента задержки, вход которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с входом установки в О счетчИка и является входом пуска генератора, выход второго элемента И соединен с третьим входом первого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, третий вход которого является синхровходом, выход первого дешифратора соединен с первым входом второго элемента И, второй вход которого соединен с вторыми входами элементов И группы и с выходом третьего элемента задержки, вход которого соединен с четвертым входом первого элемента ИШ и является входом генератора, выход второго дешифратора подключен к второму входу первого элемента И, выход первого регистра соединен с выходом генератора.

OmSi.il

Пусх

iJT

JS

uo

от

сч

ffXtf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для диагностирования цифровых блоков | 1987 |

|

SU1548789A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах контроля работоспособности и поиска дефектов дискретных блоков. Цель изобретения - повышение быстродействия устройства. Устройство для поиска дефектов дискретных блоков содержит блок ввода, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, блок 6 управления, регистр 7, счетчик 8, блок 9 элементов И, два дешифратора 10, П, вход 12 пуска. Повышение быстродействия устройства достигается за счет введения регистра 7, счетчика 8, блока 9 элементов И, дешифраторов 10, И. При этом уменьшается время поиска дефектов за счет уменьшения длины теста поиска дефектов и, как следствие, за счет уменьшения времени прохождения теста через проверяеьв11Й блок. 1 з.п. ф-лы, 5 Ш1. i (Л

ОтдлБ

j/7/rr

3S

ЗПТН

о /

/w/

Л

TW

xSf.t

OmS/t.6

/77ЛЛШ|

фиг A

ifU

f ffJlA

3

Gmffjf.Z

.

..J

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-07—Публикация

1985-10-15—Подача