1

СП ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для поиска дефектов логических блоков | 1984 |

|

SU1221654A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам контроля работоспособности и поиска дефектов цифровых узлов и блоков. Целью изобретения является расширение класса контролируемых изделий за счет включения в число контролируемых изделий блоков с элементами памяти. Устройство содержит блок 1 формирования тестовых воздействий, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, блок 6 управления. Кроме того, устройство содержит проверяемый блок 7 и коммутатор 8 с соответствующими функциональными связями. 1 з.п.ф-лы, 4 ил.

л

;о

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам контроля работоспособности и поиска дефектов цифровых узлов и блоков.

Целью изобретения является расширение класса контролируемых изделий за счет включения в число контролируемых изделий блоков с элементами памяти.

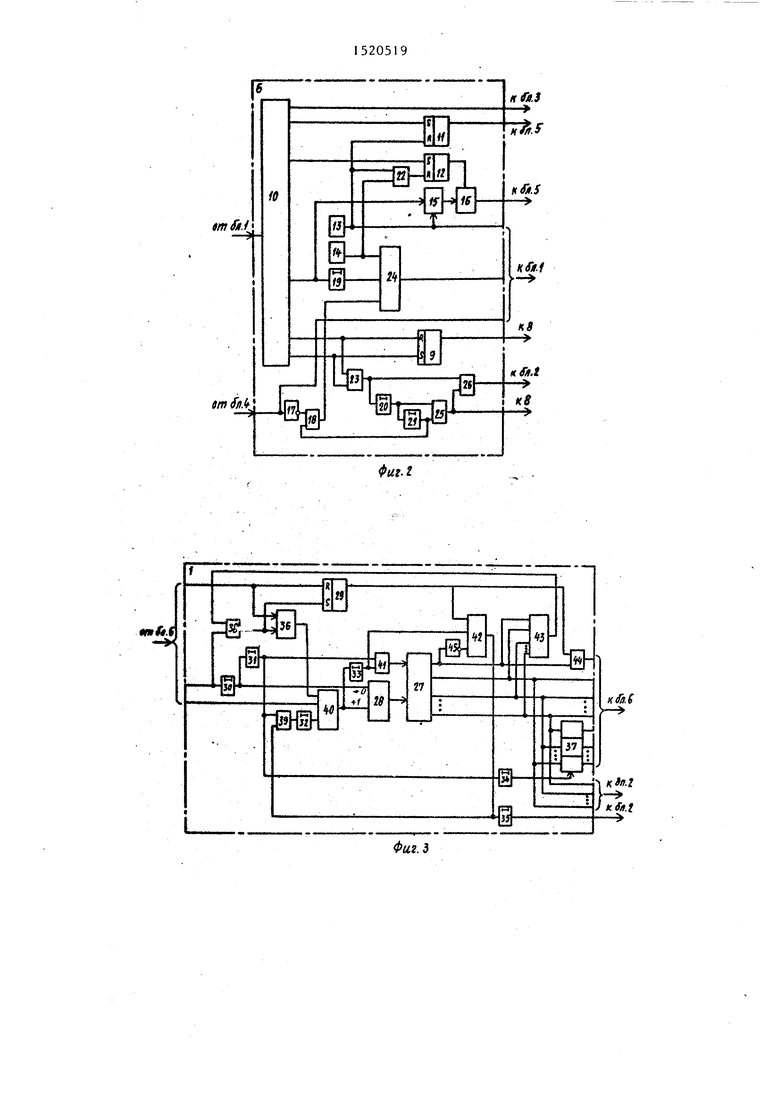

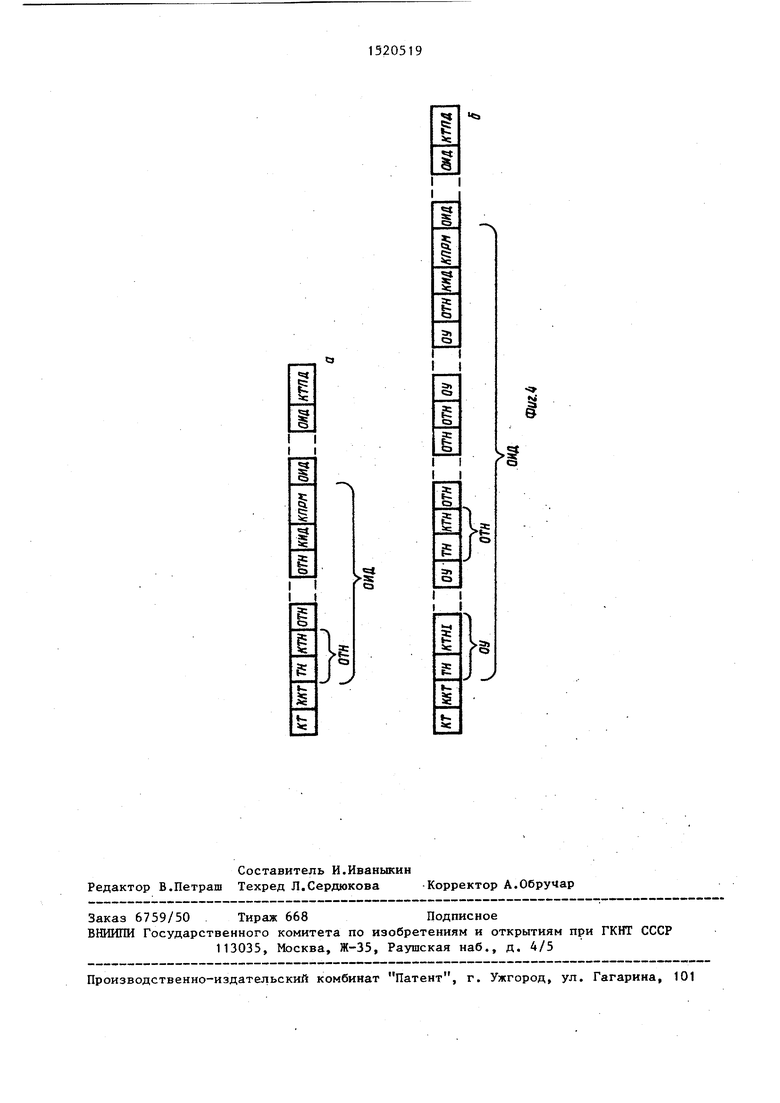

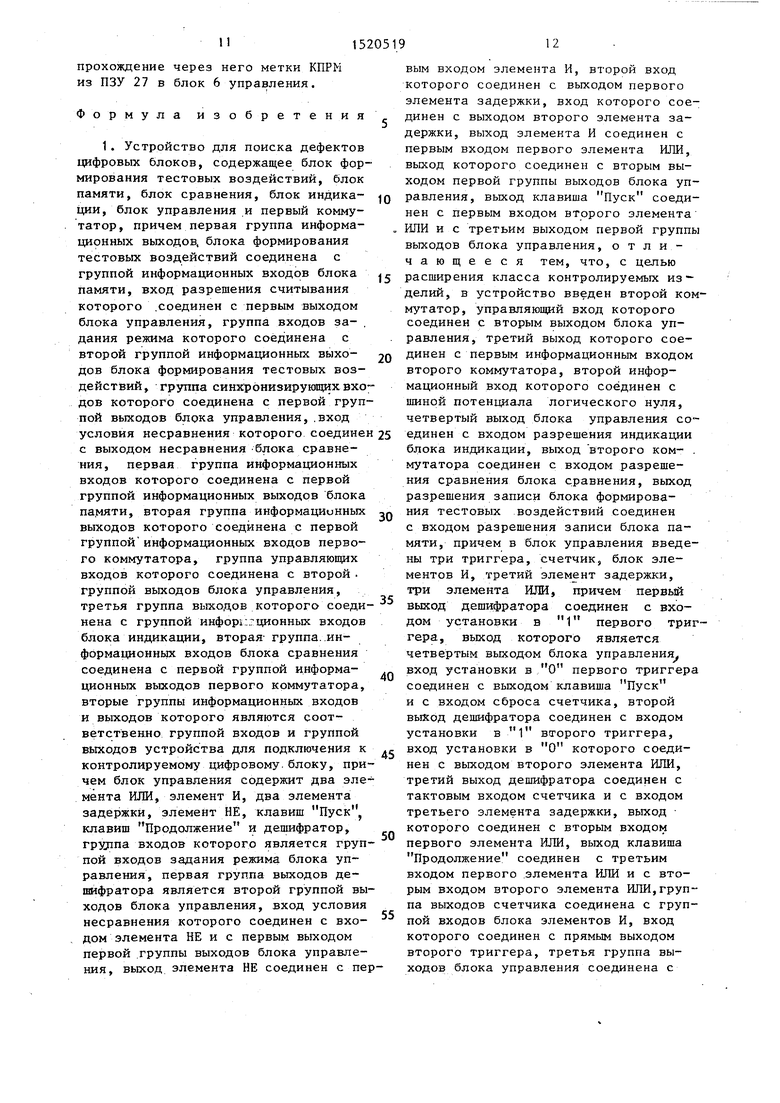

На фиг.1 представлена схема устройства; на фиг,2 - схема блока управления; на фиг.З - схема блока формирования тестовых воздействий; на фиг.4 - вид тестов поиска дефектов для комбинационных и последовательных схем.

В тесте дефектов для комбинационных схем (фиг.4а) использованы следующие обозначения: КТ - коммутационный тест, ККТ - метка конца КТ, ТН - тестовый набор, КТН - метка конца ТН, ОТН - область ТН (включает в себя ТН и КТН), КИД - метка конца идентификатора, КПРМ - метка конца перемотки, ОВД - область идентификатора (включает в себя ТН, КТН, ОТН, КИД, КПРМ), КТПД - метка конца теста поиска дефектов.

В тесте поиска дефектов для после- дователь ных схем, (фиг.Аб) кроме приведённых на фиг. 4а обозначений, используются следующие: КТН1 - метка конца ТН,. ОУ - область установки (включает в себя ТН и КТН1), ОВД включает в себя ТН, КТН, КТН1, ОТН, ОУ, КВД, КПРМ.

Устройство (фиг.1) содержит блок

Iформирования тестовых воздействий, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикаций, блок 6 управления. Кроме того, на фиг.1 изображены проверяемый блок 7 и коммутатор 8.

Блок 6 управления (фиг.2) содержит триггер 9, дешифратор 10, триггеры

IIи 12, клавиши 13 Пуск и 14 Продолжение, счетчик 15, блок 16 элементов И, элемент НЕ 17, злемент И 18, элементы 19-21 задержки, элементы ИЛИ 22-26.

Блок 1 (фиг.З) содержит постоянный запоминающий узел (ПЗУ) 27, счетчик 28, триггер 29, элементы 30-35,задержки, генератор 36 импульсов, регистр 37, элементы ИЛИ 38-41, элементы И 42-44, элемент НЕ 45.

Блок 1 формирования тестовых воздействий предназначен для ввода с

5

0

5

0

5

0

5

0

5

ПЗУ коммутационного теста, тестовых наборов и командой информации. С группы выходов блока 1 на вход блока 6 управления вьдается коммутационньш тест, информация о режимах работы устройства, с группы информационных выходов блока 1 на вход блока 2 памяти выдаются тестовые наборы, с выхода разрешения записи блока 1 на вход блока 2 памяти выдается сигнал разрешения записи тестового набора.

Блок 2 памяти предназначен для хранения тестовых наборов. С первой группы информационных выходов блока 2 памяти на вход блока 4 сравнения вьь- даются ожидаемые ответные реакции . проверяемого блока 7, с второй группы информационных выходов блока 2 памяти на вход коммутатора 3 выдаются тестовые наборы.

Коммутатор 3 предназначен для раз- деления контактов проверяемого блока 7 на входные и выходные.

Блок 4 сравнения обеспечивает сравнение реакций, получаемЬ1х с выходов проверяемого блока 7 и ожидаемых ответных реакций,.хранящихся в блоке 2 памяти. С выхода несравнения блока 4 сигнал несравнения поступает на вход блока 6 управления.

Блок 5 индикации предназначен для индикации номера класса дефектов, присутствующих в проверяемом блоке 7, а также сообщения об отсутствии дефектов в проверяемом блоке и об окончании процесса диагностирования.

Блок 6 управления организует работу всех блоков устройства. С вы-, ходов блока 6 управления на вход блока 1 вьщается командная информация; на вход коммутатора 3 выдается коммутационный тест; на вход блока 5 индикации выдаются номера классов дефектов; на вход блока 5 индикации вьщается сигнал разрешения индикации сообщения об отсутствии дефектов в проверяемом блоке и об окончании процесса диагностирования/ на управляющий вход коммутатора 8 поступает сигнал, коммутирующий сигнал сравнения ответной реакции проверяемого блока 7 с ожидаемой; на вход блока 2 памяти поступает сигнал, разрешающий считывание тестового набора и подачу его на проверяемый блок,

Коммутатор 8 предназначен для разрешения или запрещения прохождения команды разрешения сравнения с блока

6управления на вход блока 4 сравнения .

Устройство работает следующим образом.

По команде с блока 6 управления из блока 1 в блок 6 управления подается коммутационный тест, согласно которому блок 6 управления производи с помощью коммутатора 3 подключение внешних контактов проверяемого блока

7к выходам блока 2 памяти и к входа блока 4 сравнения. Затем по команде

с блока 6 управления из блока 1 в блок 2 памяти записывается первый тестовый набор первого идентификатора и ответная реакция, соответствующая реакции проверяемого блока 7 при наличии в нем дефекта данного класса По команде с блока 6 управления тестовый набор из блока 2 памяти через KONiMyTaTop 3 поступает на вход проверяемого блока 7. Ответная реакция проверяемого блока 7 через коммутатор 3 подается на вход блока 4 сравнения. Одновременно на другой вход блока 4 сравнения из блока 2 памяти поступает ожидаемая ответная реакция.

Дальнейшая работа устройства зависит от того, каким является тестовый набор - проверяющим или установочным. В тесте поиска дефектов схем без элементов памяти используются только проверяющие тестовые наборы. Необходимость установочных тестовых наборов в тесте поиска дефектов схем с элементами памяти объясняется тем, что для перехода от одного йроверя- емого тестового набора к другому нужно, в общем случае, провести проверяемый блок 7 через несколько внутренних состояний. При переходе по тестовому набору из одного такого промежуточного состояния в другое нет необходимости сравнивать реакции, поскольку такие тестовые наборы используются, только для установки проверяемого блока 7 в требуемое внутреннее состояние.

Если тестовьй набор является проверяющим, то сигнал с блока 6 управления поступает на коммутатор 8, разрешая прохождение управляющего сигнала с блока 6 управления в блок 4 сравнения. Поступивший сигнал разрешает сравнение реакций проверяемого блока 7 с ожидаемыми. В случае несовпадения реакций, блок 4 сравнения

0

5

0

5

0

5

0

5

0

5

формирует сигнал несравнения, который поступает на блок 6 управления. Появление сигнала несравнения говорит о том, что в проверяемом блоке 7 отсутствуют дефекты данного класса. В этом случае блок 6 управления выдает команду на блок 1 для перехода к проверке следуклцего идентификатора, после чего описание действия повторяется. В случае отсутствия сигнала несравнения с блока 4 сравнения через время, равное такту диагностирования, блок 6 управления вьщает команду на ввод следующего тестового набора данного идентификатора.

Если тестовый набор является установочным, то сигнал с блока 6 управления поступает на коммутатор 8, запрещая прохождение управляющего сигнала с блока 6 управления на блок 4 сравнения. В этом случае сигнал несравнения отсутствует и блок 6 управления через время, равное такту диагностирования, вьщает команду на ввод следующего тестового набора данного идентификатора. Если проверяемый блок проверен уже на всех тестовых наборах идентификатора, а сигнал несравнения так и не появился, то в этом случае в проверяемом блоке 7 присутствует один из дефектов проверяемого класса дефектов и блок 6 управления при попытке считать следующий тесто- вый набор, определив конец идентификатора, вырабатывает команду разрешения индикации номера класса дефектов в блоке 5 индикации. По номеру класса дефектов определяется и устраняется дефект, после чего работа устройства повторяется до полного устранения всех дефектов.

Блок 6 управления работает следующим образом.

Процесс диагностирования начинается нажатием клавиша Пуск 13. В резуль- тате обнуляется счетчик 15, устанав.- ливаются в ноль триггеры 11 и 12 и вырабатьгеается сигнал ЗПКТ - запись коммутационного теста. С выхода триг гера 12 нулевой сигнал поступает на управляющий вход блока 16 элементов И, запрещая индикацию содержимого счетчика 15 в блоке 5 индикации. Сигнал ЗПКТ разрешает передачу КТ - коммутационного теста с блока 1 на блок 6 управления, в результате чего КТ через дешифратор 10 поступает на вход коммутатора 3. КТ содержит

информацию о входных и выходных контактах проверяемого блока 7, согласно которой коммутатор 3 подключает входные контакты к выходам блока 2 памяти, а выходные - к входам блока 4 сравнения.

При считывании метки ККТ - конец коммутационного теста, записанной в конце КТ, дешифратор 10 выдает соответствующий сигнал ККТ, который увеличивает на единицу содержимое счетчика 15, а также через время, определяемое элементом 19 задержки, формирует на выходе элемента ИЛИ 24 еди- объясняется тем, что в,результате не- ничный сигнал ЗПТИ - запись тестового набора, который разрешает, считывание и передачу одного тестового набора в блок 2 памяти.

По прочтении метки КТН (КТН1) на выходе дешифратора 10 формируется соответствующий сигнал КТН (КТН1), который поступает на первый (второй) вход триггера 9, а также через эле20

сравнения реакций доказано отсутствие в проверяемом блоке 7 дефектов из соответствующего данному идентификатору класса дефектов, следовательно, нет необходимости подавать оставшиеся ТН идентификатора.

При считывании метки КПРМ с блока 1 через дешифратор 10 выдается сигнал КПРМ, действие которого аналогично

мент ИЛИ 23 на входы элементов ИЛИ 2625 действию сигнала ККТ.

и задержки 20. При этом на выходе элемента ИЛИ 26 формируется единичный сигнал КОНТ1, который поступает на блок 2 памяти, разрешая подачу Если после очередно ти ТН считана метка КИ тификатора, то дешифра батывается соответству

35

40

. тестового набора на проверяемый блок о КИД, который устанавливает в единицу

триггер 12. С выхода триггера 12 единичный сигйал поступает на вход блока элементов И 16, разрешая индикацию номера класса дефектов, поступающего из счетчика 15 в блок 5 индикации.

После устранения обнаруженного дефекта процесс диагностирования может быть продолжен путем нажатия клавиша продолжение 14. В результате обес печиваются действия по считыванию очередного тестового набора и устанавливается в ноль триггер 12.

Если тест поиска дефектов прошел до конца, т.е. считана метка КТПД, то дешифратором 10 вырабатывается сигнал КТПД, которьй устанавливает в единицу триггер 11. С выхода триггера 11 единичный сигнал ИНД поступает в блок 5 индикации, разрешая индикацию информации об отсутствии дефектов В проверяемом блоке 7 и об окончании г процесса диагностирования.

Блок 1 формирования тестовых BO3j- действий работает следующим образом.

Сначала в блок устанавливается ПЗУ 27 с тестом поиска дефектов. Затем на вход блока поступает сигнал ЗПКТ. Сигнал ЗПКТ поступает через элемент ИЛИ 38 на генератор им7. Затем через время, необходимое для формирования на вьжоде проверяемого блока 7 ответной реакции и определяемое элементом 20 задержки, - единица поступает на элементы ИЛИ 25 и задержки 21. При этом на выходе элемента ИЛИ 25 формь -уется единица, которая поступает как сигнал КОНТ2 на вход коммутатора 8, а также поступает на вход элемента ИЛИ 26 для под держания единицы на выходе КОНТ1. Затем через элемент 21 задержки, рассчитанный на время сравнения реакций и предназначенный для устранения ложных срабатываний единичный сигнал .с поступает на вход элементы И 18, подготавливая путь для прохождения через него сигнала НСРВ - несравнения, и на вход элемента И 25 для поддержания единицы на выходах КОНТ 1, КОНТ;.

результат сравнения может быть двояким, рассмотрим оба случая.

При совпадении ответной реакхщи с ожидаемой или при запрете на сравнение на вход НСРВ с блока 4 сравнения поступает нулевой сигнал. В этом случае на выходе элемента НЕ 17 присутствует единица, которая в момент времени, определяемый элементом

50

55

21 задержки, через элемент ИЛИ 25 вьщает разрешение на считывание и прием очередного ТН.

Если ответная реакция не совпала с ожидаемой, то с блока 4 сравнения на вход КСРВ поступает единичный сигнал. В результате на выходе элемента НЕ 17 устанавливается ноль, который запрещает считывание очередного тестового набора, и выдается сигнал ПРМ на блок t, что приводит к пропуску оставшихся ТН данного идентификатора. Необходимость пропуска ТН

объясняется тем, что в,результате не-

сравнения реакций доказано отсутствие в проверяемом блоке 7 дефектов из соответствующего данному идентификатору класса дефектов, следовательно, нет необходимости подавать оставшиеся ТН идентификатора.

При считывании метки КПРМ с блока 1 через дешифратор 10 выдается сигнал КПРМ, действие которого аналогично

Если после очередной попытки ввести ТН считана метка КИД - конец идентификатора, то дешифратором 10 выра- батывается соответствующий сигнал

915

пульсов Jib и останавливает его, а также поступает через элемент ИЛИ 38 на триггер 29, устанавливая его в единицу, и поступает на элемент 3D задержки. Единичньш сигнал с выхода триггера 29 поступает на вход элемента И 44, разрешая прохождение через него меток к блоку 6 управления, и на вход элемента И 42, подготавли- вая условия для формирования на его выходе единичного сигнала. Затем через время, необходимое для установки триггера 29, генератора импульсов 36 и определяемое элементом.30 задержки единичный сигнал поступает на счетчик адреса 28, устанавливая его в .ноль, а также н.а элемент 31 задержки Затем через время., необходимое для установки нулевого адреса на выходе ДЦР счетчика 28 адреса и определяемое элементом 31 задержки, единичный сигнал поступает через элемент ИЛИ 41 на вход СЧ - считывание ПЗУ 27, вызывая считывание КТ, а через эле- мент ИЛИ 39 на вход, элемента 32 задержки, а также на вход элемента 34 задержки.

Затем через время, необходимое для формирования КТ на информацион- .ных выходах ПЗУ 27 и определяемое элементом 34 задержки, на выходе элемента 34 задержки появляется единичный сигнал ЗРКГ, по которому происходит запись КТ в регистр 37 коммутации. Через время, необходимое для осуществления считывания-зациси КТ и .определяемое элементом 32 задержки, .единичный сигнал поступает на вход элемента ИЛИ 40. С выхода элемента ИЛИ 40 единичньЕй сигнал пос тупает на вход +1, счетчика 28 адреса, увеличивая его содержимое на единицу, и на вход элемента 33 задержки. За- тем через время, необходимое для изменения адреса на выходе АДР счетчика адреса 28 и определяемое элементом 33 задержки, единичный сигнал поступает через элемент ИЛИ 41 на вход СЧ ПЗУ 27, вызывая считывание метки ККТ - конец коммутационного теста, и на элемент И 42. При считывании любой метки из ПЗУ 27 единица поступает на вход элемента НЕ 45, с выхода которого ноль запрещает формирование единичного сигнала на выходе элемента И 42, Метка ККТ поступает для анализа в блок 6 управления.

19

10

Qг 20 25

Q д .с

35

0

5

Затем на входе ЗПТН - запись тестового набора появляется единичный сигнал, который поступает на вход +1 счетчика 28 адреса, увеличивая его содержимое, и на вход элемента 33 задержки. Затем через время необходимое для изменения адреса на выходе АДР счетчика 28 адреса и определяемое элементом 33 задержки, единичный сигнал поступает через элемент ИЛИ 41 на вход СЧ ПЗУ 27, вызьшая считывание ТН - тестового набора. Считывание ТН сопровождается появлением нуля на входе элемента НЬ 45, с выхода которого единица поступает на вход элемента И 42. При этом иа выходе элемента И 42 формируется единичный сигнал, который поступает на элемент 35 задержки, а также через элемент ИЛИ 39 на элемент 32 задержки. Затем через время, необходимое для формирования ТН на информационных выходах ПЗУ 27 и определяемое элементом 35 задержки, на выходе элемента 35 задержки появляется единичный сигнал РЗЗП, по которому происходит запись ТН в блок 2 памяти.

Затем через время, определяемое элементом 32 задержки, единичный сигнал увеличивает на единицу содержимое счетчика 28 адреса с последующим формированием сигиала СЧ, обеспечивая тем самьм считывание метки КТН (КТН1), которая поступает для анализа в блок 6 управления.

Приход на вход блока сигнала ПРМ вызывает установку триггера 29 в иоль, а также запуск генератора 36 импульсов, сигналы с выхода которого обеспечивают последоватеггьное считывание информации из ПЗУ 27 до появления метки КПРК. При этом нулевой сигКал с выхода триггера 29 поступает на вход элемента И 42, запрещая формирование сигналов РЗЗП и на элемент И 44, запрещая прохождение через него меток к блоку 6 управления. Считывание с ПЗУ 27 метки КПРМ вызывает появление на выходе элемента.И 43 единичного сигнала, который проходит через элемент ИЛИ 38 и останавливает генератор 36 импульсов, а также устанавливает триггер 29 в единицу. Единица с выхода триггера 29 поступает на элемент И 42, подготавливая условия для формирования сигнала РЗЗП, и на элемент И 44 и разрешает

прохождение через него метки КПРМ из ПЗУ 27 в блок 6 управления.

Формула изобретения

0

5

0

5

0

5

0

5

вым входом элемента И, второй вход которого соединен с выходом первого элемента задержки, вход которого соединен с выходом второго элемента задержки, выход элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с вторым выходом первой группы выходов блока управления, выход клавиша Пуск соединен с первым входом второго элемента ИЛИ и с третьим выходом первой группы выходов блока управления, отличающееся тем, что, с целью расширения класса контролируемых изделий, в устройство введен второй коммутатор, управляющий вход которого соединен с вторым выходом блока управления, третий выход которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого соединен с шиной потенциала логического нуля, четвертый выход блока управления соединен с входом разрешения индикации блока индикации, выход второго ком- . мутатора соединен с входом разрешения сравнения блока сравнения, выход разрешения записи блока формирования тестовых воздействий соединен с входом разрешения записи блока памяти, причем в блок управления введены три триггера, счетчик, блок элементов И, третий элемент задержки, три элемента ИЛИ, причем первый выход дешифратора соединен с входом установки в 1 первого триггера, выход которого является четвертым выходом блока управления вход установки в О первого триггера соединен с выходом клавиша Пуск и с входом сброса счетчика, второй выход дешифратора соединен с входом установки в 1 второго триггера, вход установки в О которого соединен с выходом второго элемента ИЛИ, третий выход дешифратора соединен с тактовым входом счетчика и с входом третьего элемента задержки, выход которого соединен с вторым входом первого элемента ИЛИ, выход клавиша Продолжение соединен с третьим входом первого элемента ИЛИ и с вторым входом второго элемента ИЛИ,группа выходов счетчика соединена с группой входов блока элементов И, вход которого соединен с прямым выходом второго триггера, третья группа выходов блока управления соединена с

группой выходов блока элементов И, четвертый выход дешифратора соединен с первым входом третьего элемента ИЛИ и с входом установки в 1 третьего триггера, второй вход третьего элемента ИЛИ соединен с пятым выходо дешифратора и с входом установки в О третьего триггера, выход третьего элемента ИЛИ соединен с первым входом четвертого элемента ИЛИ и с входом второго элемента задержки, выход которого соединен с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом первого элемента задержки, выход пятого элемента ИЛИ соединен с вторым входом четвертого элемента ИЛИ и с третьим выходом блока управления, первый выход которого соединен с выг ходом четвертого элемента ИЛИ, второй выход блока управления соединен с прямым выходом третьего триггера. 2. Устройство по п. 1, отличающееся тем, что блок фор- мирования тестовых воздействий содержит постоянный запоминающий узел, счетчик, триггер,шесть элементов задержки, генератор импульсов, регистр четьфе элемента ИЛИ, три элемента И, элемент НЕ, причем первый вход группы синхронизирующих входов блока соединен с входом запуска генератора импульсов и с входом установки в О триггера, выход которого соединен с первыми входами первого и второго элементов И, второй вход группы синхронизирующих входов блока соединен с первым входом первого элемента ИЛИ и с входом первого элемента задерж- ки,, выход которого соединен с входом второго элемента задержки и с входом сброса счетчика, выход первого элемента ИЛИ соединен с входом установки в 1 триггера и с входом останов ки генератора импульсов, выход кото

Q 5 0 5 о « с

5

рого соединен с первым входом второго элемента ИЛИ, второй вход которого является третьим входом группы синхронизирующих входов блока.выход второго элемента задержки соединен с первыми входами третьего и четвертого элементов ИЛИ и с входом третьего элемента задержки, выход которого соединен с входом разрешения записи регистра, выход четвертого элемента ИЛИ соединен с входом четвертого элемента задержки, выход которого соединен с третьим входом второго элемента ИЛИ, выход которого соединен с тактовым входом счетчика и с входом пятого элемента задержки, выход которого соединен с вторым входом третьего элемента ИЛИ и с вторым входом первого элемента И, выход которого соединён с вторым входом четвертого элемента ИЛИ и с входом шестого элемента задержки, вьЬсод которого является выходом разрешения записи бло ка, выход третьего элемента ИЛИ соединен с входом считывания постоянного запоминакнцего узла, группа адресных входов которого соединена с группой выходов счетчика, группа выходов постоянного запоминакяцего узла соединена с группой входов третьего элемента И, с группой информационных входов регистра и является первой группой информационных выходов блока, выход постоянного запоминающего узла соединен с вторым входом второго элемента И, с входом третьего элемента И, с входом элемента НЕ, выход которого соединен с третьим входом первого элемента И, выход третьего элемента И соединен с вторым входом первого элемента ИЛИ, группы выходов постоянного запоминающего узла, регистра и выход второго элемента И соединены с второй группой информационных выходов блока.

втШ

em М

Hfa.}

SI

M

(.. e

i

t I

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-11-07—Публикация

1987-03-31—Подача