Изобретение относится к автоматике и вычислительной технике, а именно к устройствам Тконтроля работоспособности и поиска дефктов цифровых узлов и блоков.

Известно устройство для контроля цифровых блоков, содержащее блок ввода, блок сравнения, блок индикации, блок памяти .

Недостатком известного устройства является малая степень автоматизации поиска, дефектов, так как при наличии большого числа неудачных исходов тестов просмотр словаря неисправностей с целью поиска неисправного элемента занимает достаточно много времени.

Наиболее близким к изобретению по технической сущности является устройство для контроля цифровых блоков, содержащее блок ввода, блок памяти г коммутатор, блок сравнения, бдок индикации, блок управления, первый и второй регистры контроля, причем первый, второй и третий выходы блока ввода соединены соответственно с первым входом блока памяти, пе 5выми входами соответственно первого и второго регистров контроля и с входом блока управления,

,первый и второй выходы блока памяти соединены соответственно с первым входом коммутатора и с первым входом блока сравнения, второй вход и второй выход коммутатора являются соответственно выходом и входомустройства, первый и вторюй выходы блока сравнения соединены соответ.ственно с вторыми входами первого

10 и второго регистров контроля,выходы первого и второго регистров контроля соединены с входами блока индикации, а первый, второй, третий и четвер.тый выходы блока управления соеди15нены соответственно свходом блока ввода, вторым входом блока памяти, третьим входом блока сравнения и с третьим входом коммутатора.

Это устройство позволяет опре20делить множество одиночных дефектов проверяемого блока. Поиск дефектов осуществляется с помощью

тестов, а именно, подачей на входы проверяемого блока последователь25ности, входных импульсов (тестового набора) и проверкой правильности реакций проверяемого блока. Для каждого тестового набора с блока ввода выдается множество одиночных

30 дефектов, обнаруживаемых данным

набором. При наличии дефекта это множествг (среди которого присутствует как действительный дефект блока так и подозреваемые) подается на один из регистров контроля. При отсутствии дефекта, т.е. в случае правильного ответа блока на данный тестовый набор, соответствующее набору множество подозреваемых дефектов записывается в другой регистр контроля.

Таким образом, в первом регистре будут сосредоточены возможные оди ночные дефекты, а во втором регистре будут фиксироваться одиночные дефекты, действительно отсутствующие в бло ке (исключенныеиз рассмотрения дефекты) , так как соответствующие тестовые наборы их не обнаружили. Если из возможных дефектов удалить .исключенные дефекты (т.е. произвести onepa цию вычитания из множества возможных дефектов множества исключенных дефектов) , то результатом будет множество .действительных дефектов блока.

.Номера этих дефектов будут индици. рованы на блоке индикации, а по таблице неисправностей будет найден номер неисправного элемента и вид дефекта Г

Недостатком известного устройства являются относительно большие затраты времени на подготовку информации для поиска дефектов и соответственно большое время поиска дефектов. Составление тестов весьма трудоемкий и дорогостоящий процесс. Затраты на создание программного обеспечения, решающего эту задачу или на ручное составление тестов, значительны и превосходят стоимость самих устройств контроля.

Для работы известного устройства тесты должны формироваться следующим образом. После построения полного диагностического теста для каждого тестового набора необходимо промоделировать каждый из возможных и. проверяемом блоке дефектов для вычисления множества одиночных дефектов, обнаруживаемых данным набором. Таким образом, после получения h тестовых наборов и при m возможных одиночных дефектах в проверяемом блоке необходимо

.произвести nxm дополнительных анализов.

Цель изобретения - ускорение поиска дефектов. .

Поставленная цель достигается тем что в устройстве для поиска дефекта цифровых узлов, содержащем блок ввода , блок памяти,коммутатор, блок сравнения, блок индикации, блок управления, причем первый выход блока управления соединен с входом блока ввода, первый выход которого соединен с первьа«| входом блока памяти, первая группа выходов которого соединена с первой группой информационных входов коммутатора, управляющий вход котсурго соединен с вторым выходом блока управления, третий выход которого содинен с вторым входом блока памяти, вторая группа выходов которого соединена с первой группой информационных входов-блока сравнения, вторая групп информационных входов;.которого соединена с первой группой выходов коммуттора, вторая группа информационных входов которого соединена соответственно с входами проверяемого узла, группа выходов которого соединена соответственно с второй группой информационных входов коммутатора, управлякядий вход блока сравнения соединен с четвертым выходом блока управления, первый вход которого соединен с вторым выходом блока ввода, третий выход которого соединен cf первым входом блока индикации, второй вход блока индикации соединен с пятым выходом блока управле ния, второй вход которого соединен с выходом блока сравнения.

Блок управления содержит дешифратор, два переключателя, три элемента или , элемент НЕ, элемент И, два элемента задержки, два шифратора, причем выход первого шифратора является первым выходом блока, второй выход блока соединен с первым выходом первого дешифратора, второй выход которого соединен с входом первого элемента задержки и является третьим выходом блока, четвертый выход.блока соединен с выходо первого элемента задержки и с выходом второго элемента, задержки, вход которого соединен с первым входом элемента И, выход которого соединен с первым вход6м первого элемента ИЛИ, второй вход которого соединен с третьим выходом дешифратора, четвертый выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого переключателя, выход второго переключателя соединед с первым входом первого шифратора и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и с вторым входом первого шифратора, третий вход которого соединен о выходом первого элемента ИЛИ и с третьим входом третьего элемента ИЛИ, выход которого соединен с четвертым входом первого шифратора, первый вход блока соедине с входом дешифратора, второй вход блока соединен с пятым входом первого шифратора и с входом элемента НЕ, выход которого соединен с вторым входом второго элемента И, пятый и пюстой выходы дешифратора соединены соответственно с первым и вторым входами второго шифратора, выход которого является пятым выходом блока.

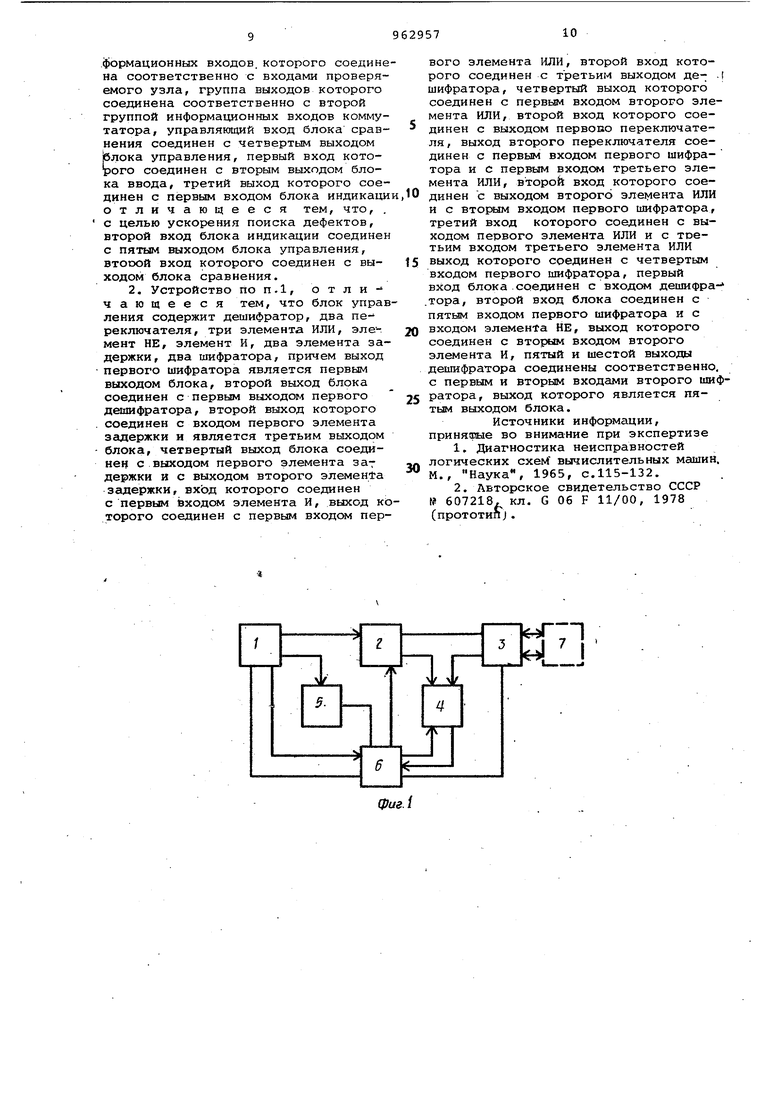

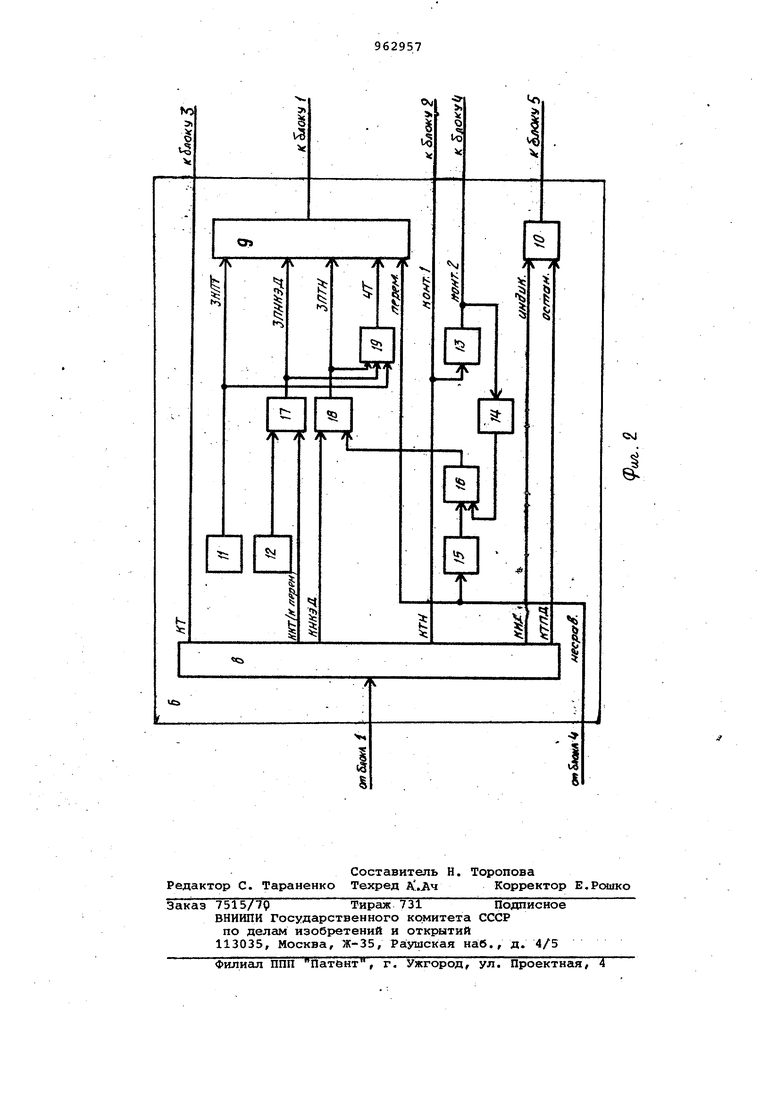

На фиг,1 представлена схема устройства; на фиг.2 - схема блока управления.

Устройство содержит блок 1 ввода, блок 2 памяти, ко мутатор 3, блок 4 сравнения, блок 5 индикации, блок б управления и проверяемый блок 7.

Блок управления содержит дешифратор 8, шифраторы 9 и 10, переключатели 11 и 12 Пуск и Продолжение, элементы 13 и 14 задержки, элементы НЕ 15, элемент И 16, элементы ИЛИ 17-19.

Процесс диагностирования начинается нажатием кнопки 11 Пуск. В результате вырабатываются два сигнала: через элемент ИЛИ 19 сигнал ЧТ разрешение на чтение информации блоком 1 ввода, и сигнал ЗПКТ - запись коммутационного теста.(КТ), который разрешает передачу КТ с блока 1 вво,да на первый вход блока 6 управления. Данные сигналы через шифратор 9 и первый выход блока 6 управления поступают на блок 1 ввода. КТ содержит информацию о входных и выходных контактах проверяемого блока 7 , согласно которой коммутатор 3подключает входные контакты к выходам блока 2 памяти, а выходные контакты - к входам блока 4 сравнения.

При считывании метки ККТ, записанной в конце КТ, детиифратор 8 выдает соответствующий сигнал ККТ, который формирует два сигнала: ЧТ через элемент ИЛИ 19 и сигнал ЗПНКЭД через элемент ИЛИ 17, которые разр ешают считывание и передачу НКЭД с блока 1 ввода в блок 5 индикации.

По прочтению метки КИКЭД блок 1 ввода через дешифратор 8 выдает соответствующий сигнал КНКЭД, KOTOjxidf формирует два сигнала: ЧТ через элементы ИЛИ 18 и 19 и сигнал ЗПТН через элемент ИЛИ 18, которые разрешают считывание и передачу одного тестового набора (ТН) с блока 1 ввопа в блок 2 памяти. , i

По прочтении метки КТН блок 1 ввода через дешифратор 8 вьщает соответствующий сигнал КТН, разрешает подачу тестового набора, на проверяемый блок 7 через третий выход блока б управления (сигнал КОНТ.1), и по истечению времени, равного.установлению на выходе проверяемого блока 7 ответной реакции, через Элемент 13 задержки выдает сигнал КОНТ.2 через четвертый выход блока 6 управления. Последний сигнал во-первых, разрешает сравнение ожидаемых реакций, записанных в блоке 2 памяти. и ответных реакций с про веряемого блока 7 и, во-вторых, через элемент 14 задержки подготавли- , вает путь прохождения сигнала несрав,нения НЕСРАВ, через элемент И 16. Элемент 14 задбржки, рассчитанный .на время сравнения реакций, предназначен для устранения ложных срабатываний элемента и 16. 5 Результат сравнения может быть двояким, поэтому рассмотрим оба случая.

При совпадении ответных реакций с ожидаемыми сигнал ;НЕСРАВ. с блока 4 сравнения отсутствует В этом случае на выходе элемента НЕ присутствует единица, которая в момент времени, определяемый элементом 14 задержки, через элементы ИЛИ 18 и 19

5 и шифратор 9 сигналов выдает разрешение на считывание и прием очередного ТН.

Если ответная реакция не совпала с ожидаемой, то с блока 4 сравнения

0 выдается сигнал НЕСРАВ, который поступает на второй вход блока 6 управления. В результате, во-первых, на выходе элемента НЕ 15 устанавливается ноль, который запрещает считывание

5 очередного тестового набора, и воBTOfftix, выдается сигнал ПЕРЕМ., КО7 ,торый через шифратор 9 сигналов и первый выход блока 6 управления приводит к пропуску оставшихся ТН данного

- идентификатора до метки К ПЕРЕМ.

Необходимость пропуска ТН объясняется тем, что в результате несовпадения реакций доказано отсутствие дефектов из иЙентифицируемого класса эквивалентных дефектов, а значит, нет необходимости подавать оставшиеся ТН идентификатора. При считывании метки К ПЕРЕМ, с блока 1 ввода через дешифратор а выдается сигнал К ПЕРЕМ, действия которого аналогичны действиям

0 сигнала ККТ.

Если после очередной попытки ввести ТН считана метка КИД (кднец идентификатора) , то дешифратором 8 вырабатывается соответствующий сигнал

5 ЗКИД, который является сигналом на индикацию ИНДИК. Данный сигнал через шифратор 10 и пятый выход бло. ка 6 управления разрааает индикацию номера класса эквивалентньах дефектов

Q в блоке 5 индикации.

После устранения обнаруженного дефекта процесс диагностирования может -быть продолжен путем нажатия кнопки 12 ПРОДОЛЖЕНИЕ. В результате

5 будут обеспечены действия, аналогичные действиям сигналов ККТ или К ПЕРЕМ.

Если тест поиска дефектов прошел до конца; T.Q. считана метка КТПД,

O то дешифратором 8 вырабатывается сигнал на индикацию ОСТАН. Данный сигнал через шифратор 10 и пятый выход блока 6 управления разрешает индикацию и нформахщи об отсутствии .

5 идентифицируемых дефектов проверяемого блока 7 и окончания процесса диагностирования .

Для организации процесса поиска дефектов используется тест пЪиска дефектов (ТПД), организованный следующим образом.

Все множество дефектов проверяемого блока разбивается на классы эквивалентности таким образом, что неразличимее дефекты образуют один класс. Для каждого класса эквивалентных дефектов строится идентификатор - минимальная совокупность тестовых наборов, выделяющих данный класс дефектов среди всех других классов дефектов. Причем при подаче на проверяемый блок идентификатора для одного класса дефектов при наличии в блоке дефектов, принадлежащих данному классу, реакция на выходе проверяемого блока будет отличаться от ответной реакции блока без дефекта или блока с дефектами, не принадлежащими данному классу дефектов , хотя бы на одном тестовом наборе идентификатора.

Блок 1 .ввода предназначен для ввода с перфоленты, например, номера класса эквивалентных дефектов, тестовых наборов, информации с ожидаемой ответной реакции блока 7, а такжекомандной информации. Блок 2 памяти предназначен для хранения и выдачи на проверяемый блок 7 тестовой информации. Коммутатор 3 предназначен для коммутации внешних контактов проверяемого блока 7, при этом вхоЯ-ныв контакты подключаются к выходам блока 2 памяти, выходные кон такты подключа ются к входам блока 4 сравнения. Блок 4 сравнения обес-. печивает сравнение реакций, получаемых с выходов проверяемого блока 7, и ответных реакций, хранящихся в блоке 2 памяти. При несовпадении реакций блок 4 сравнения формирует сиг нал нёсравнения. Блок 5 индикации |предназначен для индикации номера ;класса дефектов. Блок 6 управления организует работу всех блоков устоойства.

По команде б управления из блока 1 ввода подается коммутационный тест согласно которому блок 6 управления производит требуемые коммутации внешних контактов проверяемого блока 7 к выходам блока 2 памяти и к входам блока 4 сравнения. Затем по команде с блока 6 управления из блока 1 ввода в блок 5 индикации записывается номер класса эквивалентных дефектов. Затем по команде с блока 6 управления из блока 1 ввода в блок 2 памяти записывается первый тестовый набор первого идентификатора и ответная реакция, соответствующая реакции блока при наличии в

нем дефекта данного класса. Тестовый набор из блока 2 памяти через коммутатор 3 поступает на вход проверяемого блока 7. Ответные реакции проверяемого блока 7 через коммутатор 3 подаются на вход блока 4 сравнения. Одновременно на другой вход блока

4сравнения из блока 2 памяти поступают ожидаемые ответные реакции.

В случае несовпадения ожидаемых и полученных ответных реакций блок 4 сравнения формирует сигнал несравнения, который поступает на блок б управления. Появление сигнала несравнения говорит о том, что в проверяемом блоке 7 отсутствуют дефекты данного класса. В этом случае блок 6 управления выдает команду на блок 1 ввода для перемотки.ленты и переходу к проверке следующего идентификатора, после чего описанные действия повторяются. В случае отсутствия сигнала несравнения с блока 4 сравнения через время, равное такту контроля, блок 6 управления выдает команДУ 3 ввод следующего тестового набора данного идентификатора. Если проверяемый блок 7 был проверен уже на всех тестовых наборах данного идентификатора , а сигнал несравнения так и не появился, в этом случае в проверяемом блоке 7 присутствует один из дефектов проверяемого класса дефектов, блок б управления при попытке считать следующий тестовый набор, определив конец идентификатора, выдает команду на индикацию номера

класса эквивалентных дефектов на блок

5индикации. По номеру класса дефектов определяется и устраняется дефект. Затем работа устройства повторяется до полного устранения всех дефектов блока.

Формула изобретения

1. Устройство для поиска дефектов цифровых узлов, содержгицее блок ввода, блок памяти, коммутатор, блок

сравнения, блок индикации/ блок управления, причем первый выход блока управления соединен с входом блока ввода, первый выход которого соединен с первым входом блока памяти, первая группа выходов которого соединена с первой группой информационных входов коммутатора, управляющий вход которого соединен с вторым выходом блока управления, третий выход которого соединен с вторым входом блока

памяти, вторая группа выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов котолого соединена с первой группой вы1ходов коммутатора, вторая группа ин- .формационных входов, которого соедине на соответственно с входами проверяемого узла, группа выходов которого соединена соответственно с второй группой информационных входов коммутатора, управляющий вход блока сравнения соединен с четвертьлм выходом |блока управления, первый вход которого соединен с вторым выходом блока ввода, третий выход которого соединен с первым входом блока индикаци отличающееся тем, что, с целью ускорения поиска дефектов, второй вход блока индикации соединен с пятым выходом блока управления, втоосй вход которого соединен с выходом блока сравнения. 2. Устройство По П.1, отличающееся тем, что блок управ ления содержит дешифратор, два переключателя, три элемента ИЛИ, элемент НЕ, элемент И, два элемента задержки, два шифратора/ причем выход первого шифратора является первым выходом блока, второй выход блока соединен с первым выходом первого дешифратора, второй выход которого . соединен с входом первого элемента задержки и является третьим выходом блока, четвертый выход блока соединен с выходом первого элемента за7 держки и с выходом второго элемента задержки, вход которого соединен с первым йходом элемента И, выход ко торого соединен с первым входсм первого элемента ИЛИ, второй вход которого соединен с третьим выходом да-; шифратора, четвертый выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первопо переключателя, выход второго переключателя соединен с первым входом первого шифратора и с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и с вторым входом первого шифратора, третий вход которого соединен с выходом первого элемента ИЛИ и с третьим входом третьего элемента ИЛИ выход которого соединен с четвертым входом первого шифратора, первый вход блока .соединен с входом дешифратора, второй вход блока соединен с пятым входом первого шифратора и с входом элемента НЕ, выход которого соединен с вторым входом второго элемента И, пятый и шестой выходы дешифратора соединены соответственно, с первым и вторым входами второго шифратора, выход которого является пятым вьлходом блока. Источники информации, принятые во внимание при экспертизе 1.Диагностика неисправностей логических схем вычислительных машин. М., Наука, 1965, с.115-132. 2.Авторское свидетельство СССР 607218, кл. G Об F 11/00, 1978 (прототип;.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для поиска дефектов логических блоков | 1984 |

|

SU1221654A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Многоканальное устройство для контроля систем управления | 1985 |

|

SU1345200A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для поиска дефектов дискретных блоков | 1990 |

|

SU1714610A1 |

о I

Авторы

Даты

1982-09-30—Публикация

1980-07-04—Подача