Изобретение относится к автомати- ке и вычислительной технике: к устройствам контроля работоспособности и поиска дефектов дискретных узлов и блоков.

Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля схем и дискретных блоков, содержащих комбинационные схемы и схемы, содержащие элементы памяти.

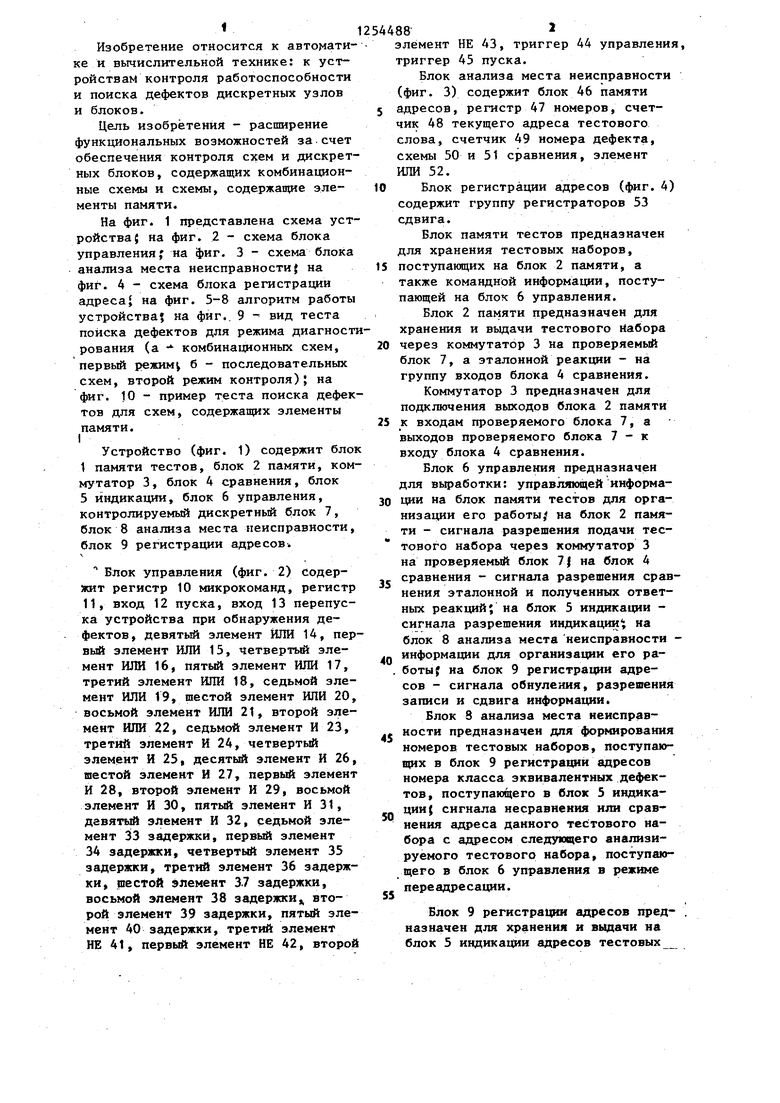

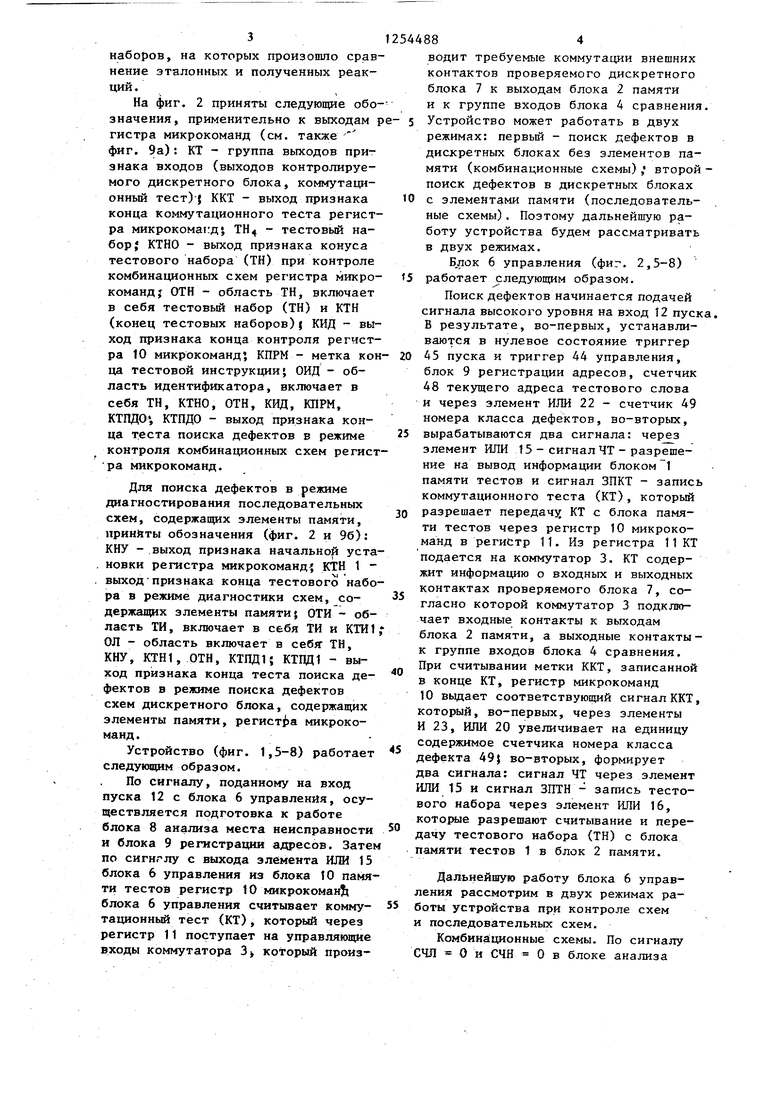

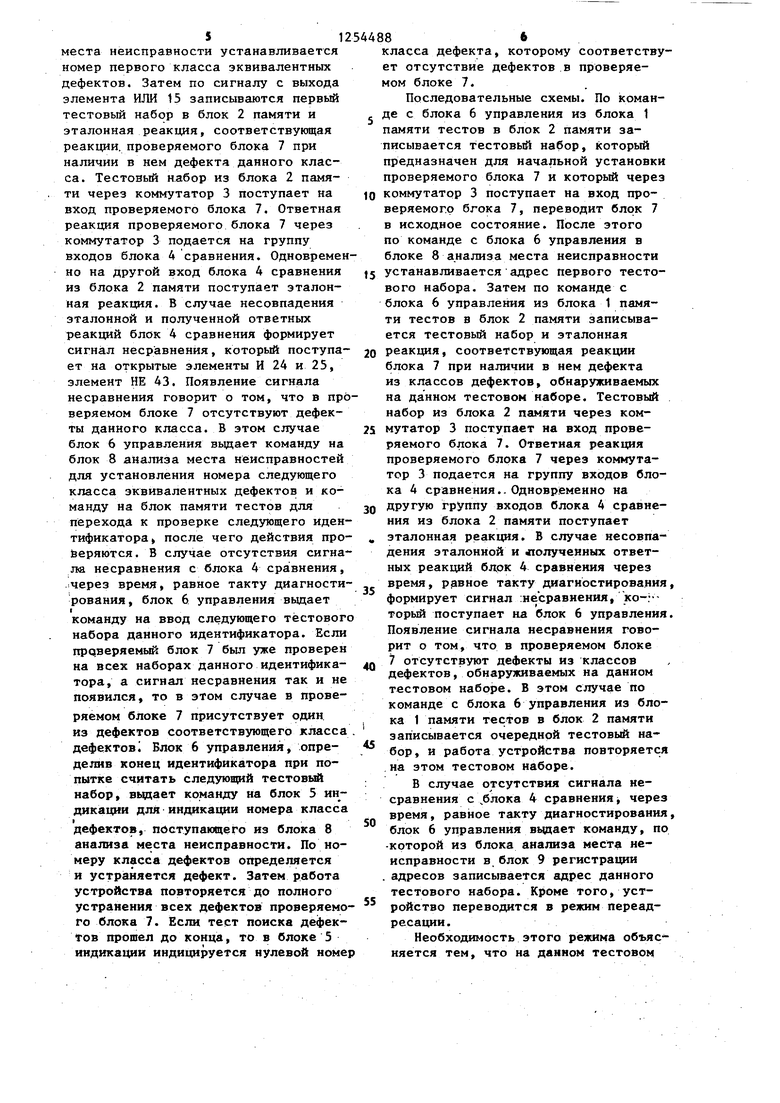

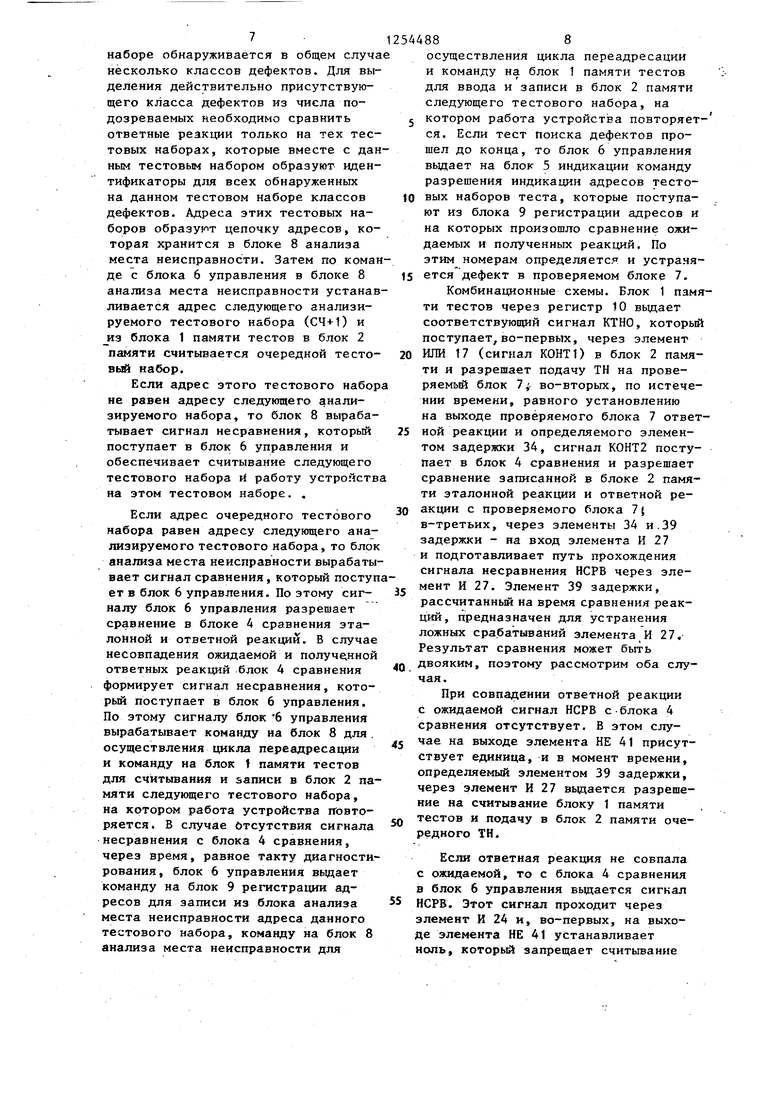

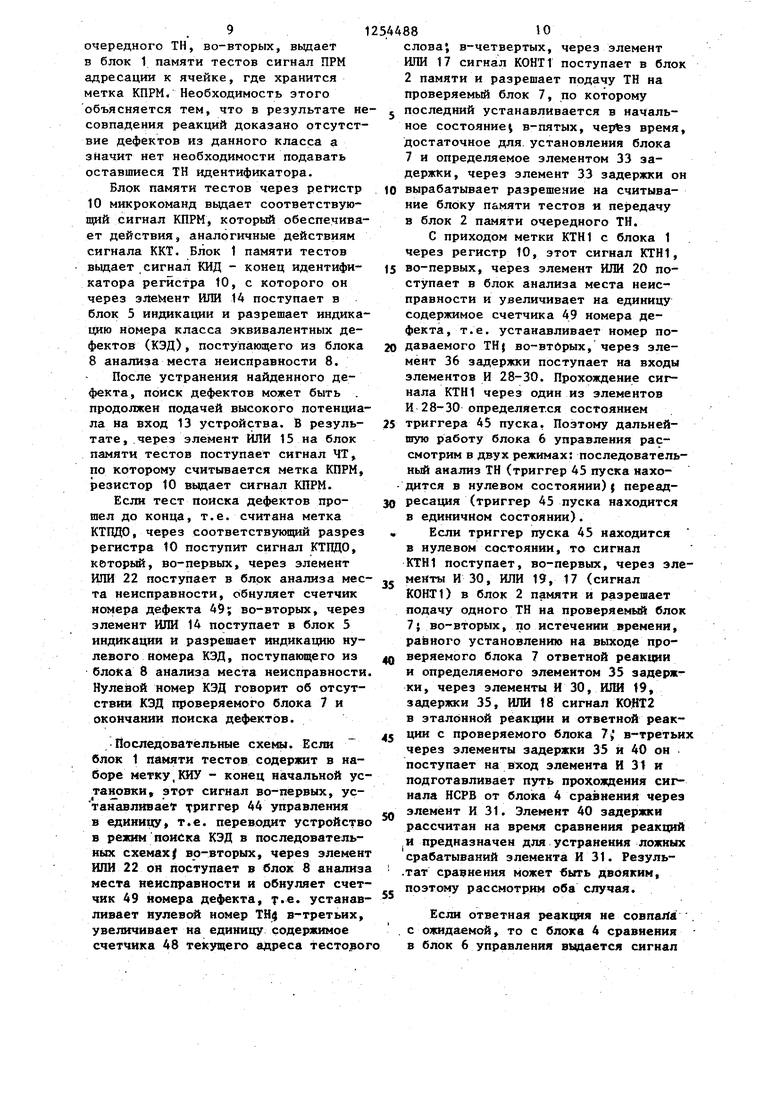

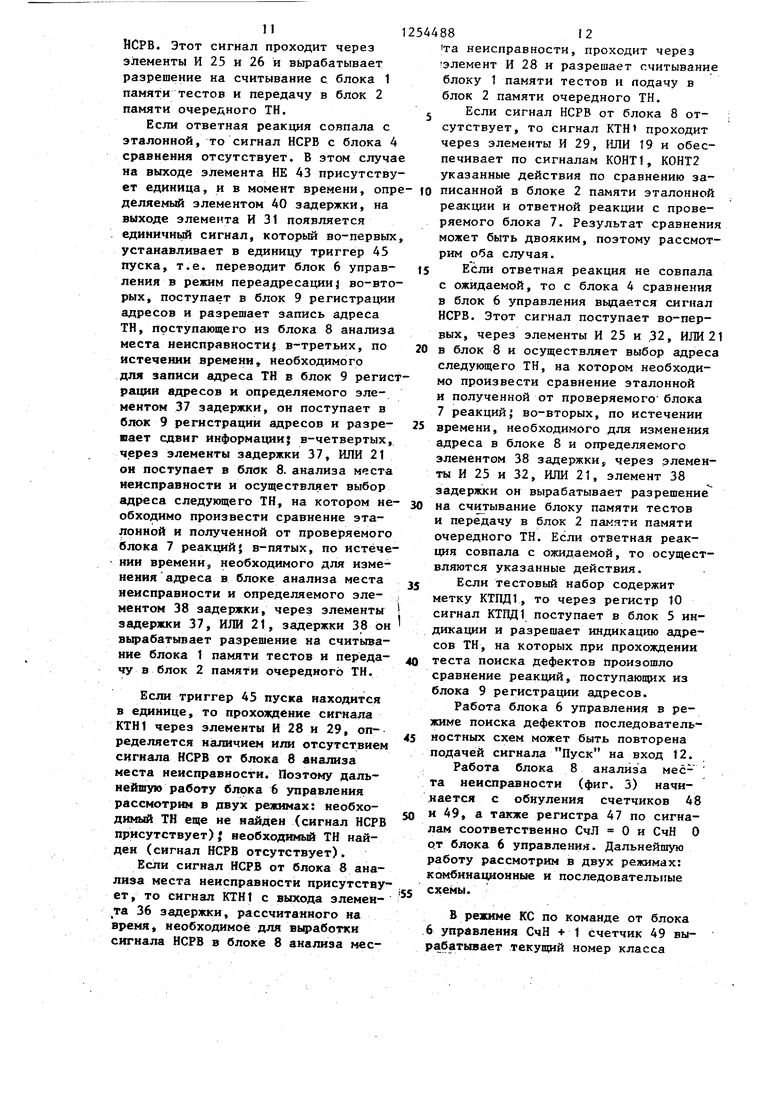

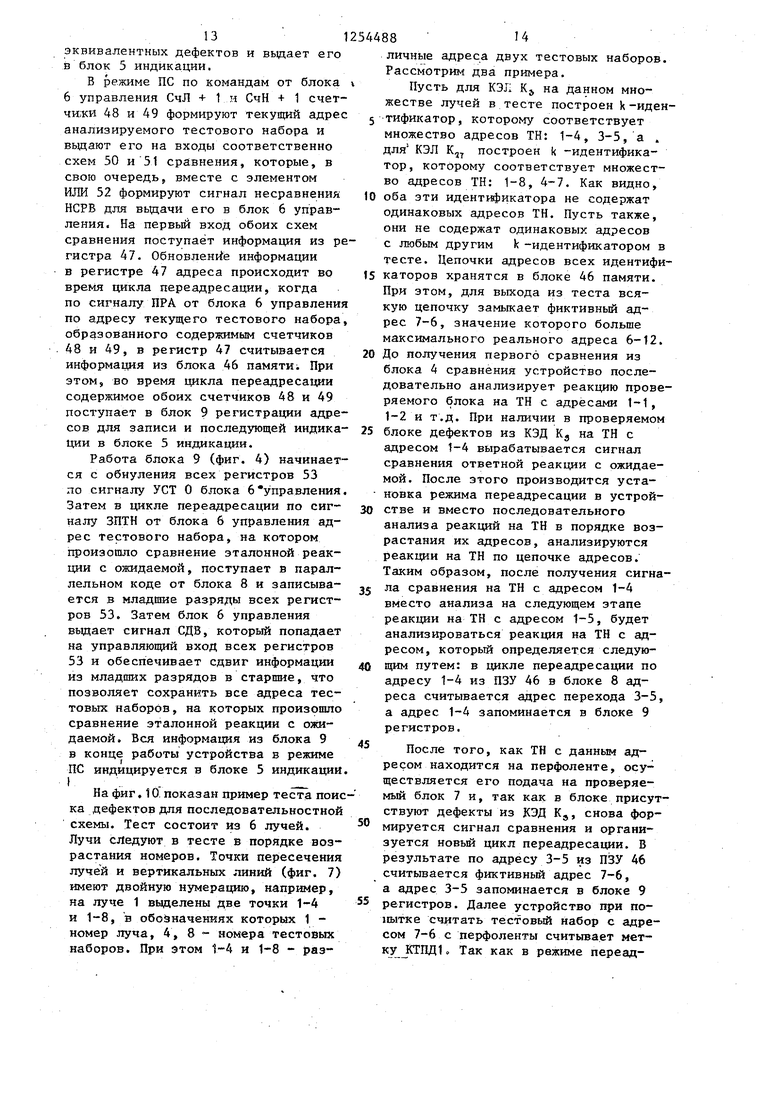

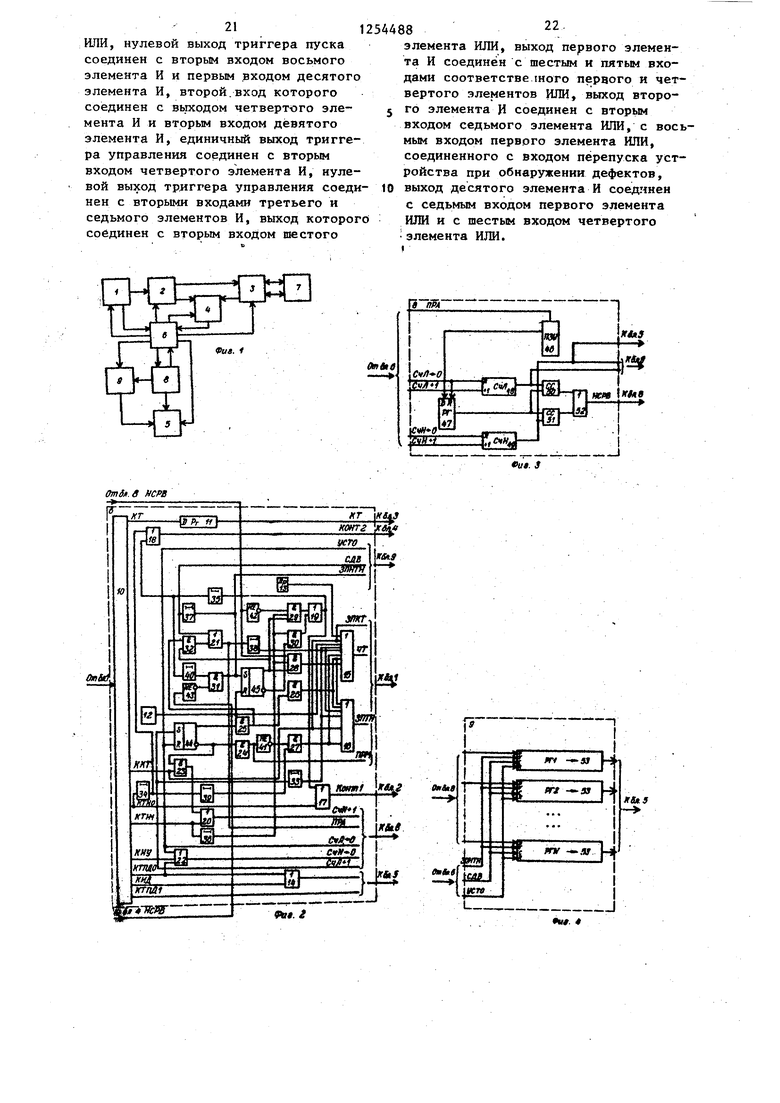

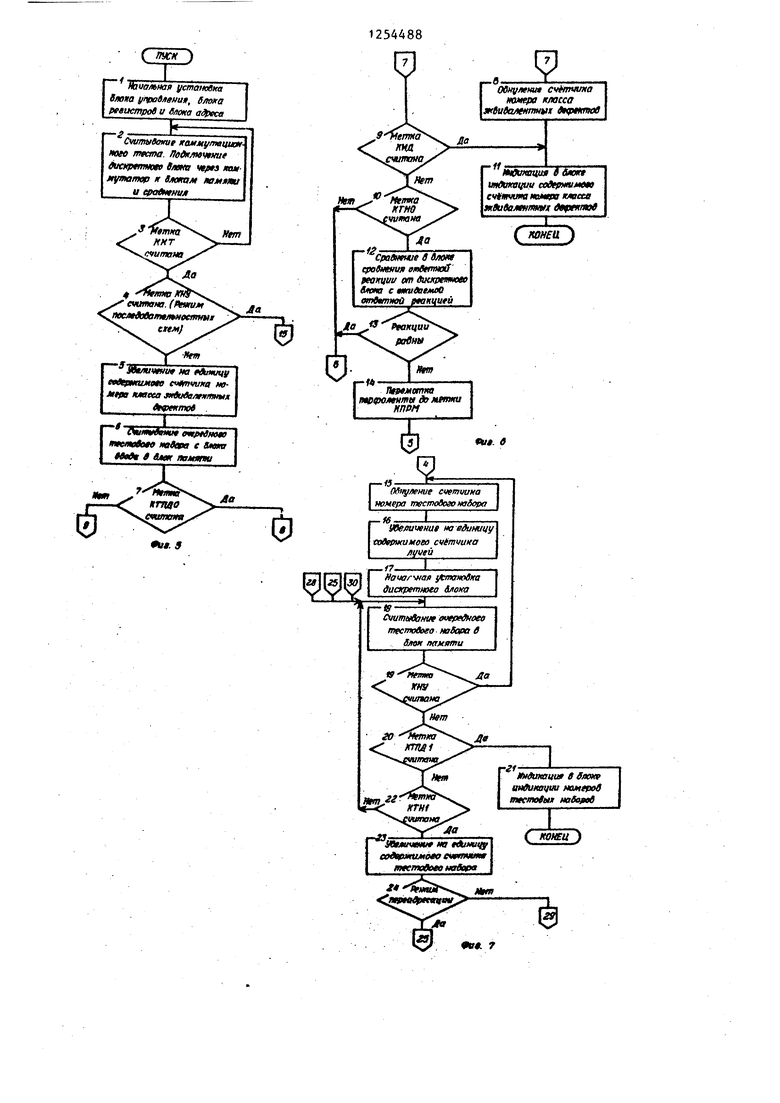

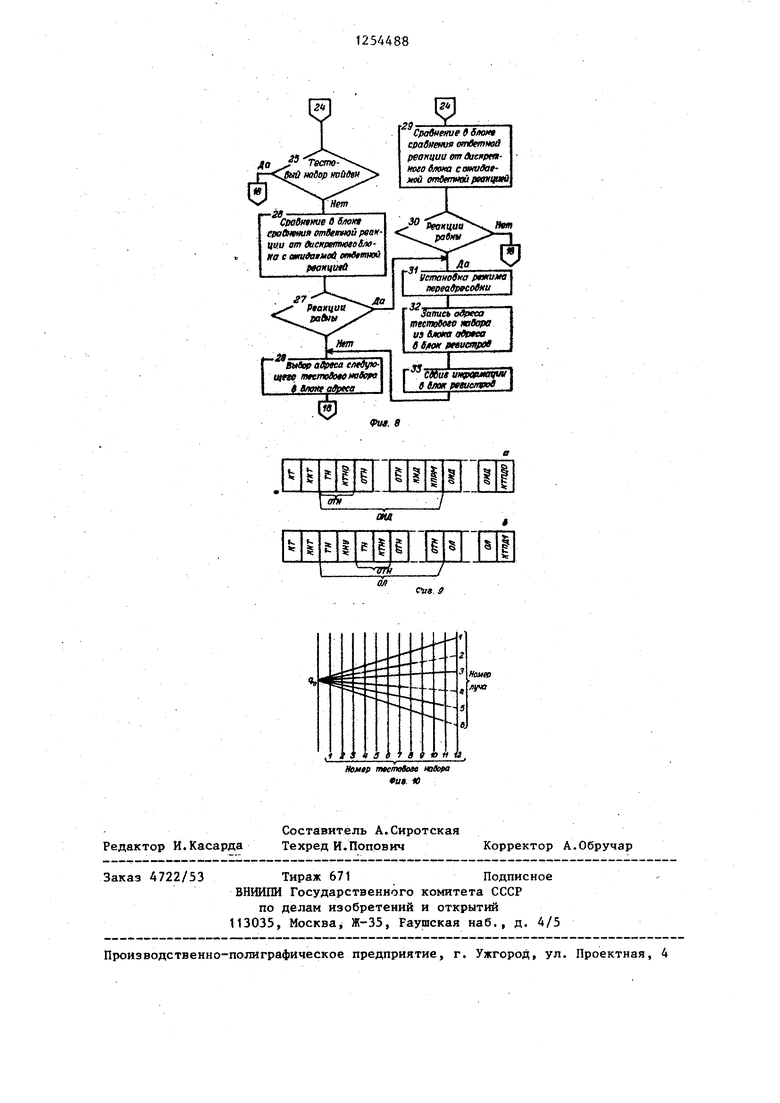

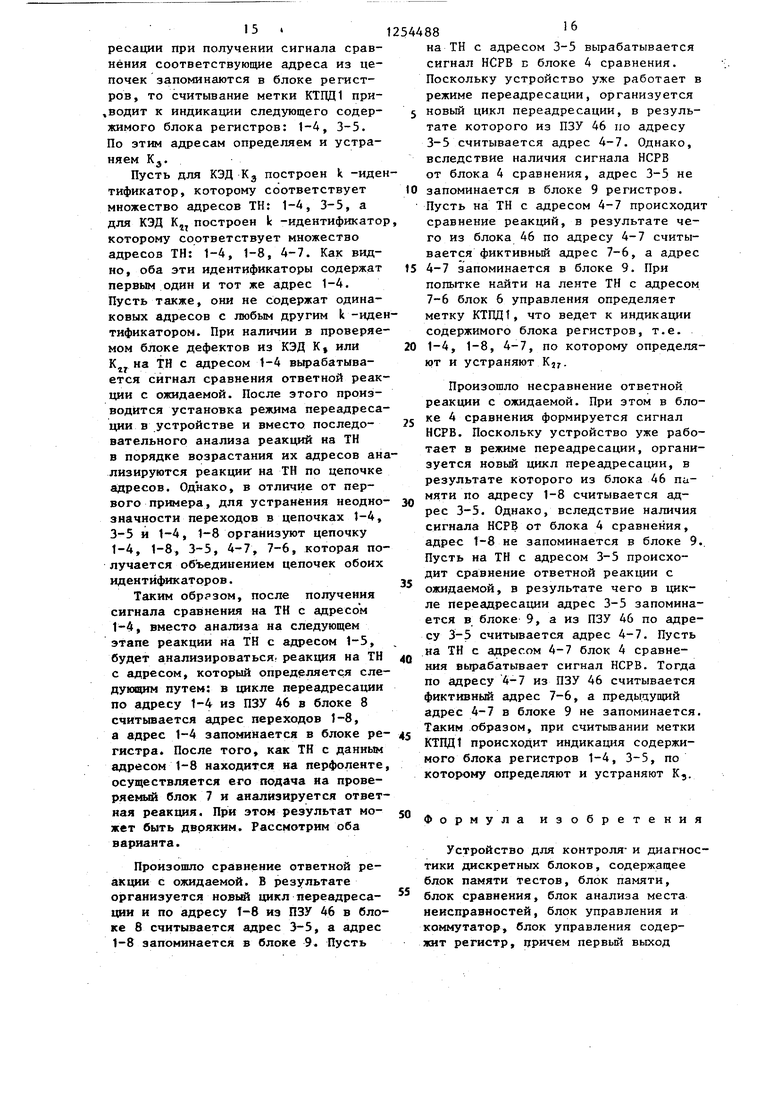

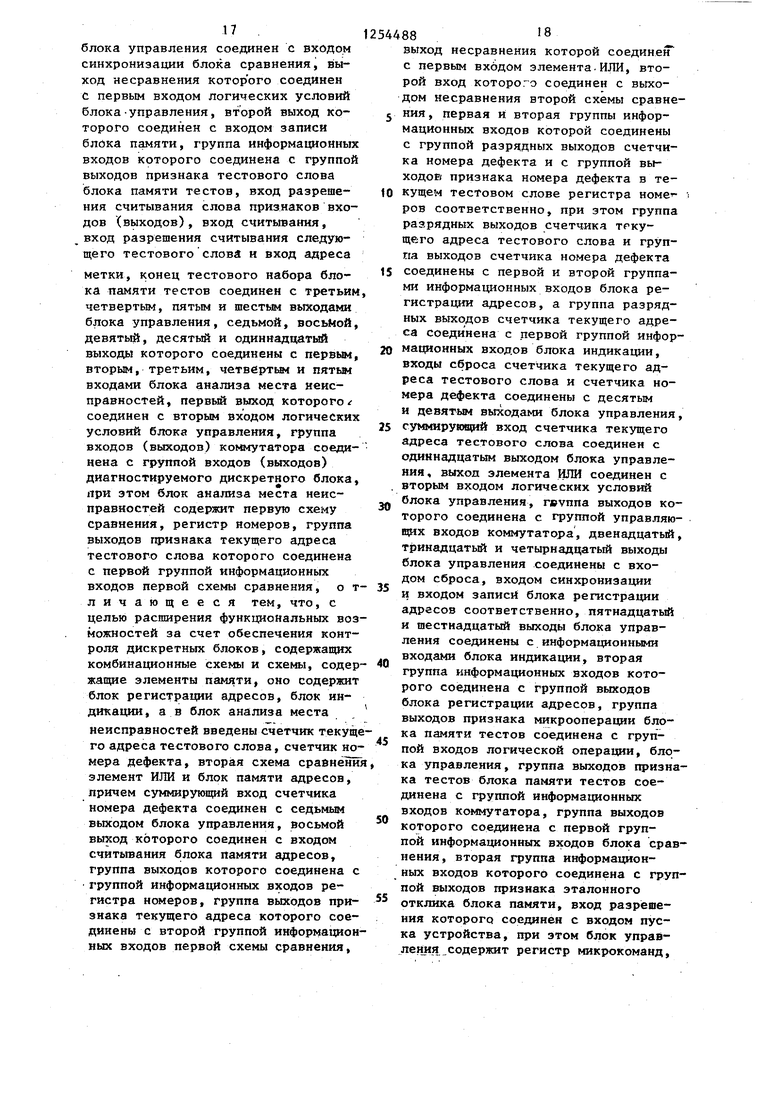

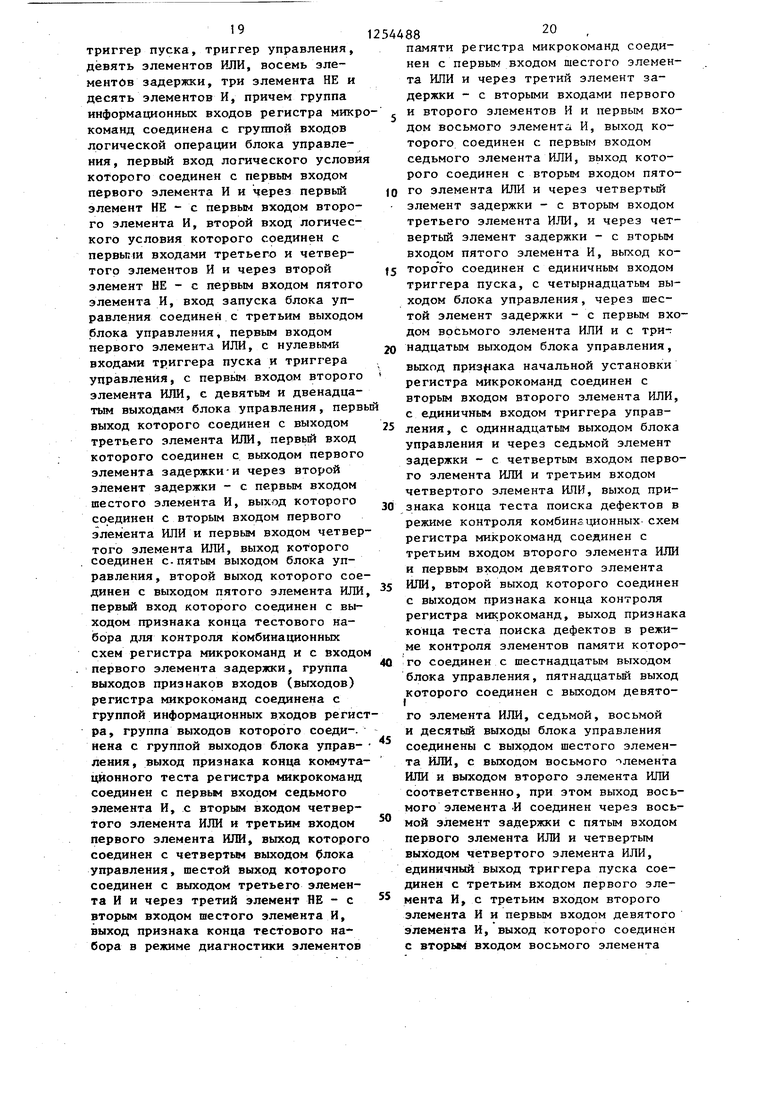

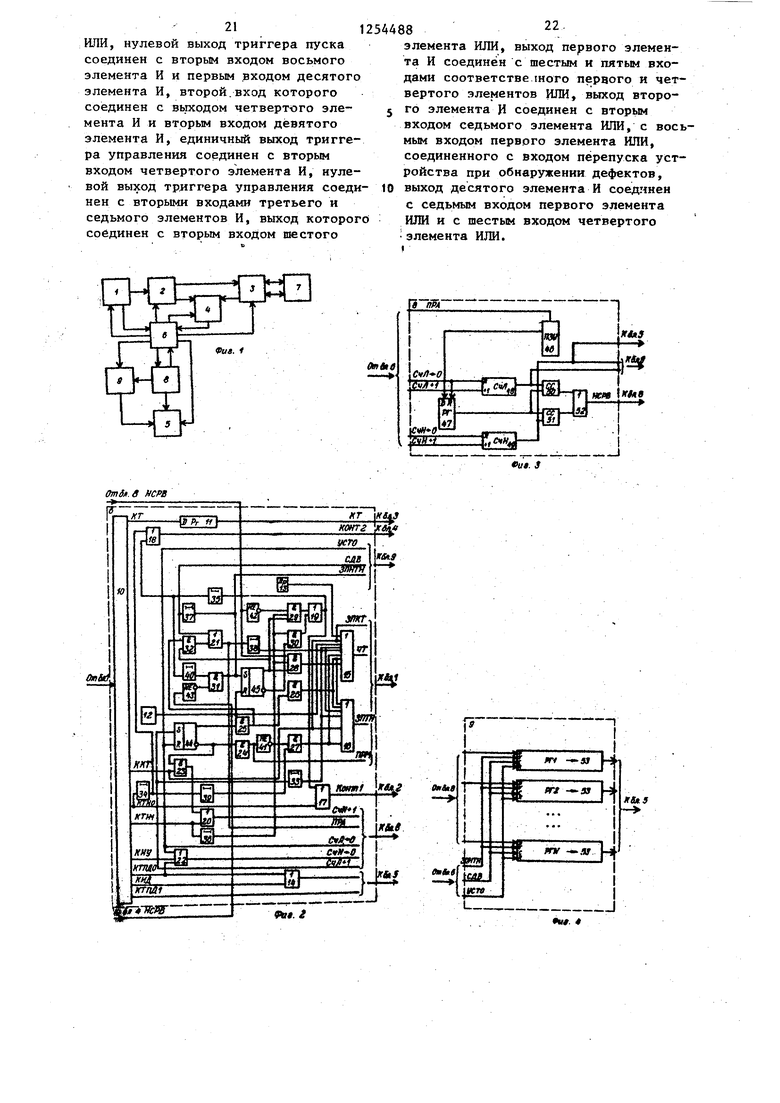

На фиг. 1 представлена схема устройства} на фиг. 2 - схема блока управления; на фиг. 3 - схема блока анализа места неисправностиf на фиг. 4 - схема блока регистрации адресаi на фиг. 5-8 алгоритм работы устройства на фиг.. 9 - вид теста поиска дефектов для режима диагностирования (а комбинационных схем, первый режиму б - последовательных схем, второй режим контроля); на фиг. 10 - пример теста поиска дефектов для схем, содержащих элементы

памяти. I

Устройство (фиг. 1) содержит блок памяти тестов, блок 2 памяти, коммутатор 3, блок 4 сравнения, блок 5 индикации, блок 6 управления, контролируемый дискретньй блок 7, блок 8 анализа места неисправности, блок 9 регистрации адресов.

Блок управления (фиг. 2) содержит регистр 10 микрокоманд, регистр 11, вход 12 пуска, вход 13 перепуска устройства при обнаружения дефектов, девятый элемент ИЛИ 14, первый элемент ИЛИ 15, четвертый элемент ШШ 16, пятый элемент ИЛИ 17, третий элемент ШШ 18, седьмой элемент ИЛИ 19, шестой элемент ИЛИ 20, восьмой элемент ИЛИ 21, второй элемент ИЛИ 22, седьмой элемент И 23, третий элемент И 24, четвертый элемент И 25, десятый элемент И 26, шестой элемент И 27, первый элемент И 28, второй элемент И 29, восьмой элемент И 30, пятый элемент И 31, девятый элемент И 32, седьмой элемент 33 задержки, первый элемент 34 задержки, четвертый элемент 35 задержки, третий элемент 36 задержки, шестой элемент 3.7 задержки, восьмой элемент 38 задержки, второй элемент 39 задержки, пятый элемент 40 задержки, третий элемент НЕ 41, первый элемент НЕ 42, второй

44

управления.

5

0

элемент НЕ 43, триггер триггер 45 пуска.

Блок анализа места неисправности (фиг. 3) содержит блок 46 памяти адресов, регистр 47 номеров, счетчик 48 текущего адреса тестового слова, счетчик 49 номера дефекта, схемы 50 и 51 сравнения, элемент ИЛИ 52.

Блок регистрации адресов (фиг. 4) содержит группу регистраторов 53 сдвига.

Блок памяти тестов предназначен для хранения тестовых наборов, поступающих на блок 2 памяти, а также командной информации, поступающей на блох 6 управления.

Блок 2 памяти предназначен для хранения и выдачи тестового йабора через коммутатор 3 на проверяемый блок 7, а эталонной реакции - на группу входов блока 4 сравнения.

Коммутатор 3 предназначен для подключения выходов блока 2 памяти 5 к входам проверяемого блока 7, а выходов проверяемого блока 7 - к входу блока 4 сравнения.

Блок 6 управления предназначен для выработки: управляющей информации на блок памяти тестов для организации его работы/ на блок 2 памяти - сигнала разрешения подачи тестового набора через коммутатор 3 на проверяемьй блок 7} на блок 4 сравнения - сигнала разрешения сравнения эталонной и полученных ответных реакций; на блок 5 индикации - сигнала разрешения индикации на блок 8 анализа места неисправности - информации для организации его работы на блок 9 регистрации адресов - сигнала обнуления, разрешения записи и сдвига информации

Блок 8 анализа места неисправности предназначен для формирования номеров тестовых наборов, поступаю- вщх в блок 9 регистрации адресов номера класса эквивалентных дефектов, поступающего в блок 5 индикации ( сигнала несравнения или сравнения адреса данного тестового набора с адресом следующего анализируемого тестового набора, поступающего в блок 6 управления в режиме переадресации.

0

5

0

5

0

5

Блок 9 регистрации адресов предназначен для хранения и выдачи на блок 5 индикации адресов тестовых

наборов, на которых произошло сравнение эталонных и полученных реакций.

На фиг. 2 приняты следующие обозначения, применительно к выходам р гистра микрокоманд (см. также фиг. 9а): КГ - группа выходов признака входов (выходов контролируе- МОго дискретного блока, коммутационный тест)} ККТ - выход признака конца коммутационного теста регистра микрокомандJ ТН - тестовый набор J КТНО - выход признака конуса тестового набора (ТН) при контроле комбинационных схем регистра микрокоманд J ОТН - область ТН, включает в себя тестовый набор (ТН) и КТН (конец тестовых наборов)| КИД - выход признака конца контроля регистра 10 микрокоманд; КПРМ - метка конца тестовой инструкции; ОИД - область идентификатора, включает в себя ТН, КТНО, ОТН, КИД, КПРМ, КТПДО , КТПДО - выход признака конца теста поиска дефектов в режиме контроля комбинационных схем регистра микрокоманд.

Для поиска дефектов в режиме диагностирования последовательных схем, содержащих элементы памяти, принйты обозначения (фиг. 2 и 96): КНУ - .выход признака начальной уста- новки регистра микрокоманд КТН 1 - выход признака конца тестового набора в режиме диагностики схем, со- держаацих элементы памяти; ОТИ - область ТИ, включает в себя ТИ и КТИ1 , ОЛ - область включает в себя ТН, КНУ, КТН1, ОТН, КТПД1; КТЦД1 - выход признака конца теста поиска дефектов в режиме поиска дефектов схем дискретного блока, содержащих элементы памяти, регистра микрокоманд.

Устройство (фиг. 1,5-8) работает следующим образом.

По сигналу, поданному на вход пуска 12 с блока 6 управления, осуществляется подготовка к работе блока 8 анализа места неисправности и блока 9 регистрации адресов. Затем по сигнглу с выхода элемента ИЛИ 15 блока 6 управления из блока 10 памяти тестов регистр 10 микрокоманд; блока 6 управления считывает коммутационный тест (КТ), который через регистр 11 поступает на управляющие входы коммутатора 3 который произ10

s

t5

20

25

0

5

0

5

O

5

водит требуемые коммутации внешних контактов проверяемого дискретного блока 7 к выходам блока 2 памяти и к группе входов блока 4 сравнения. Устройство может работать в двух режимах: первый - поиск дефектов в дискретных блоках без элементов памяти (комбинационные схемы) , второй - поиск дефектов в дискретных блоках с элементами памяти (последователь- . ные схемы). Поэтому дальнейшую работу устройства будем рассматривать в двух режимах.

Блок 6 управления (фиг. 2,5-8) работает следующим образом.

Поиск дефектов начинается подачей сигнала высокого уровня на вход 12 пуска. В результате, во-первых, устанавливаются в нулевое состояние триггер 45 пуска и триггер 44 управления, блок 9 регистрации адресов, счетчик 48 текущего адреса тестового слова и через элемент ИЛИ 22 - счетчик 49 номера класса дефектов, во-вторых, вырабатываются два сигнала: через элемент ИЛИ 15 - сигнал ЧТ - разрешение на вывод информации блоком 1 памяти тестов и сигнал ЗПКТ - запись коммутационного теста (КТ), который разрешает передачу КТ с блока памяти тестов через регистр 10 микрокоманд в регистр 11. Из регистра 11 КТ подается на коммутатор 3. КТ содержит информацию о входных и выходных контактах проверяемого блока 7, согласно которой коммутатор 3 подклк - чает входные контакты к выходам блока 2 памяти, а выходные контакты- к группе входов блока 4 сравнения. При считывании метки ККТ, записанной в конце КТ, регистр микрокоманд 10 вьщает соответствующий сигнал ККТ, который, во-первых, через элементы И 23, ИЛИ 20 увеличивает на единицу содержимое счетчика номера класса дефекта 49J во-вторых, формирует два сигнала: сигнал ЧТ через элемент ИЛИ 15 и сигнал ЗПТН - запись тестового набора через элемент ИЛИ 16, которые разрешают считывание и передачу тестового набора (ТН) с блока памяти тестов 1 в блок 2 памяти.

Дальнейшую работу блока 6 управления рассмотрим в двух режимах работы устройства при контроле схем и последовательных схем.

Комбинационные схемы. По сигналу еЧЛ О и СЧН - О в блоке анализа

места неисправности устанавливается номер первого класса эквивалентных дефектов. Затем по сигналу с выхода элемента ИЛИ 15 записываются первый тестовый набор в блок 2 памяти и эталонная реакция, соответствующая реакции, проверяемого блока 7 при наличии в нем дефекта данного класса. Тестовый набор из блока 2 памяти через коммутатор 3 поступает на вход проверяемого блока 7. Ответная реакция проверяемого блока 7 через коммутатор 3 подается на группу входов блока 4 сравнения. Одновременно на другой вход блока 4 сравнения из блока 2 памяти поступает эталонная реакция. В случае несовпадения эталонной и полученной ответных реакций блок 4 сравнения формирует сигна л несравнения, который поступает на открытые элементы И 24 и 25, элемент НЕ 43. Появление сигнала несравнения говорит о том, что в проверяемом блоке 7 отсутствуют дефекты данного класса. В этом случае блок 6 управления выдает команду на блок 8 анализа места неисправностей для установления номера следующего класса эквивалентных дефектов и команду на блок памяти тестов для перехода к проверке следующего Идентификатора, после чего действия проверяются. В случае отсутствия сигнала несравнения с блока 4 сравнения, через время, равное такту диагностирования, блок 6 управления выдает команду на ввод следующего тестовог набора данного идентификатора. Если пррверяемый блок 7 был уже проверен на всех наборах данного идентификатора, а сигнал несравнения так и не появился, то в этом случае в проверяемом блоке 7 присутствует один из дефектов соответствующего класса дефектов Блок 6 управления, определив конец идентификатора при попытке считать следующий тестовьй набор, вьвдает команду на блок 5 дикации для индикации номера класса

дефектов, поступающего из блока 8 анализа места неисправности. По номеру класса дефектов огфеделяется и устраняется дефект. Затем работа устройства повторяется до полного устранения всех дефектов проверяемого блока 7. Если тест поиска дефектов прошел до конца, то в блоке 5 индикации индицируется нулевой номе

класса дефекта, которому соответствует отсутствие дефектов .в проверяемом блоке 7.

Последовательные схемы. По коман, де с блока 6 управления из блока 1 памяти тестов в блок 2 памяти записывается тестовый набор, который предназначен для начальной установки проверяемого блока 7 и который через

0 коммутатор 3 поступает на вход проверяемого бгока 7, переводит блок 7 в исходное состояние. После этого по команде с блока 6 управления в блоке 8 анализа места неисправности

5 устанавливается адрес первого тестового набора. Затем по команде с блока 6 управления из блока 1 памяти тестов в блок 2 памяти записывается тестовый набор и эталонная

0 реакция, соответствующая реакции блока 7 при наличии в нем дефекта из классов дефектов, обнаруживаемых на данном тестовом наборе. Тестовый набор из блока 2 памяти через ком5 мутатор 3 поступает на вход проверяемого блока 7. Ответная реакция проверяемого блока 7 через коммутатор 3 подается на группу входов блока 4 сравнения.. Одновременно на

0 другую группу входов блока 4 сравнения из блока 2 памяти поступает

. эталонная реакция. В случае несовпадения эталонной и лолученных ответных реакций блок 4 сравнения через время, рэвное такту диагностирования, формирует сигнал :несравнения, ко-:-- торый поступает на блок 6 управления. Появление сигнала несравнения говорит о том, что в проверяемом блоке

- 7 отсутствуют дефекты из классов дефектов, обнаруживаемых на данном

тестовом наборе. В этом случае по команде с блока 6 управления из бло- ка 1 памяти тестов в блок 2 памяти записывается очередной тестовый набор, и работа устройства повторяется на этом тестовом наборе.

В случае отсутствия сигнала несравнения с яблока 4 сравнения -, через время, равное такту диагностирования, блок 6 управления вцдает команду, по которой из блока анализа места неисправности в блок 9 регистрации . адресов записывается гщрес данного тестового набора. Кроме того, устройство переводится в режим переадресации.

Необходимость этого режима объясняется тем, что на данном тестовом

5

0

5

7

наборе обнаруживается в общем случа несколько классов дефектов. Для выделения действительно присутствующего класса дефектов из числа подозреваемых необходимо сравнить ответные реакции только на тех тестовых наборах, которые вместе с данным тестовым набором образуют идентификаторы для всех обнаруженных на данном тестовом наборе классов дефектов. Адреса этих тестовых наборов образуют цепочку адресов, которая хранится в блоке 8 анализа места неисправности. Затем по команде с блока 6 управления в блоке 8 анализа места неисправности устанавливается адрес следующего анализируемого тестового набора (СЧ+1) и из блока 1 памяти тестов в блок 2 памяти считывается очередной тестовый набор.

Если адрес этого тестового набор не равен адресу следующего анализируемого набора, то блок 8 вырабатывает сигнал несравнения, который поступает в блок 6 управления и обеспечивает считывание следующего тестового набора ri работу устройств на этом тестовом наборе. .

Если адрес очередного тестового набора равен адресу следующего анализируемого тестового набора, то блок анализа места неисправности вырабатывает сигнал сравнения, который поступет в блок 6 управления. По этому сигналу блок 6 управления разрешает сравнение в блоке 4 сравнения эталонной и ответной реакций. В случае несовпадения ожидаемой и полученной ответных реакций блок 4 сравнения формирует сигнал несравнения, который поступает в блок 6 управления. По этому сигналу блок 6 управления вырабатывает команду на блок 8 для. осуществления цикла переадресации и команду на блок t памяти тестов для считывания и записи в блок 2 памяти следующего тестового набора, на котором работа устройства повторяется . В случае отсутствия сигнала несравнения с блока 4 сравнения, через время, равное такту диагностирования, блок 6 управления выдает команду на блок 9 регистрации адресов для записи из блока анализа места неисправности адреса данного тестового набора, команду на блок 8 анализа места неисправности для

544888

осзтцествления цикла переадресации и команду на блок 1 памяти тестов для ввода и записи в блок 2 памяти следующего тестового набора, на 5 котором работа устройства повторяет- ся. Если тест поиска дефектов прошел до конца, то блок 6 управления выдает на блок 5 индикагщи команду разрешения индикации адресов тесто- 10 вых наборов теста, которые поступают из блока 9 регистрации адресов и на которых произошло сравнение ожидаемых и полученных реакций. По этим номерам определяется и устраня- 15 ется дефект в проверяемом блоке 7.

Комбинационные схемы. Блок 1 памяти тестов через регистр 10 выдает соответствующий сигнал КТНО, который поступает, во-первых, через элемент 20 ИЛИ 17 (сигнал КОНТ1) в блок 2 памяти и разрешает подачу ТН на проверяемый блок 1 во-вторых, по истечении времени, равного установлению на выходе проверяемого блока 7 ответ- 5 ной реакции и определяемого элементом задержки 34, сигнал КОНТ2 поступает в блок 4 сравнения и разрешает сравнение записанной в блоке 2 памяти эталонной реакции и ответной ре0 акции с проверяемого блока 7j

в-третьих, через элементы 34 и.39 задержки - на вход элемента И 27 и подготавливает путь прохождения сигнала несравнения НСРВ через элемент И 27. Элемент 39 задержки,

рассчитанньй на время сравнения реакций, предназначен для устранения ложных срабатываний элемента И 27. Результат сравнения может быть

Q двояким, поэтому рассмотрим оба случая.

При совпадении ответной реакции с ожидаемой сигнал НСРБ с блока 4 сравнения отсутствует. В этом слу5 чае на выходе элемента НЕ 41 присутствует единица, и в момент времени, определяемый элементом 39 задержки, через элемент И 27 вьщается разрешение на считывание блоку 1 памяти

0 тестов и подачу в блок 2 памяти очередного ТН.

Если ответная реакция не совпала с оямдаемой, то с блока 4 сравнения в блок 6 управления вьщается сигнал НСРВ. Этот сигнал проходит через элемент И 24 и, во-первых, на выходе элемента НЕ 41 устанавливает ноль, который запрещает считывание

очередного ТН, во-вторых, вьздает в блок 1 памяти тестов сигнал ПРМ адресации к ячейке, где хранится метка КПРМ. Необходимость этого объясняется тем, что в результате не совпадения реакций доказано отсутствие дефектов из данного класса а значит нет необходимости подавать оставшиеся ТН идентификатора.

Блок памяти тестов через регистр 10 микрокоманд вцдает соответствующий сигнал КПРМ, который обеспечивает действия, аналогичные действиям сигнала ККТ. Блок 1 памяти тестов выдает сигнал КИД - конец идентифи- катора регистра 10, с которого он через зяеНент ИЛИ 14 поступает в блок 5 индикации и разрешает индика- одю номера класса эквивалентных дефектов (КЭД), поступающего из блока 8 анализа места неисправности 8.

После устранения найденного дефекта, поиск дефектов может быть . продолжен подачей высокого потенциала на вход 13 устройства. В резуль- тате, .через элемент ИЛИ 15 на блок памяти тестов поступает сигнал ЧТ, по которому считывается метка КПРМ, резистор 10 выдает сигнал КПРМ.

Если тест поиска дефектов про- шел до конца, т.е. считана метка КТПДО, через соответствующий разрез регистра 10 поступит сигнал КТВДО, который, во-первых, через элемент ИЛИ 22 поступает в блок анализа мес- та неисправности, обнуляет счетчик номера дефекта 49; во-вторых, через элемент ИЛИ 14 поступает в блок 5 индикации и разрешает индикацию нулевого номера КЭД, поступающего из блока 8 анализа места неисправности Нулевой номер КЭД говорит об отсутствии КЭД проверяемого блока 7 и окончании поиска дефектов.

Последовательные схемы. Если блок 1 памяти тестов содержит в наборе метку,КИУ - конец начальной установки, этот сигнал во-первых, ус- танавливает триггер 44 управления в единицу, т.е. переводит устройство в режим поиска КЭД в последовательных схемахj во-вторых, через элемент ИЛИ 22 он поступает в блок 8 анализа места неисправности и обнуляет счетчик 49 номера дефекта, . устанав- ливает нулевой номер в-третьих, увеличивает на единицу содержимое счетчика 48 текущего адреса Тестово

слова в-четвертых, через элемент ИЛИ 17 сигнал КОНТТ поступает в блок 2 памяти и разрешает подачу ТН на проверяемый блок 7, по которому последний устанавливается в начальное состояниеi в-пятых, время, достаточное для. установления блока 7 и определяемое элементом 33 задержки, через элемент 33 задержки он вырабатывает разрешение на считывание блоку памяти тестов и передачу в блок 2 памяти очередного ТН.

С приходом метки КТН1 с блока 1 через регистр 10, этот сигнал КТН1, во-первых, через элемент ИЛИ 20 поступает в блок анализа места неисправности и увеличивает на единицу содержимое счетчика 49 номера дефекта, т.е. устанавливает номер подаваемого THj во-втбрых, через элемент 36 задержки поступает на входы элементов И 28-30. Прохождение сигнала КТН1 через один из элементов И 28-30 определяется состоянием триггера 45 пуска. Поэтому дальнейшую работу блока 6 управления рассмотрим в двух режимах: последовательный анализ ТН (триггер 45 пуска находится в нулевом состоянии)J переадресация (триггер 45 пуска находится в единичном Состоянии).

Если триггер пуска 45 находится в нулевом состоянии, то сигнал КТН1 поступает, во-первых, через элементы И 30, ИЛИ 19, 17 (сигнал КОНТ1) в блок 2 памяти и разрешает подачу одного ТН на проверяемый блок 7; во-вторых, по истечении времени, равного установлению на выходе проверяемого блока 7 ответной реакции и определяемого элементом 35 задержки, через элементы И 30, ШШ 19, задержки 35, ИЛИ 18 сигнал КОЯТ2 в эталонной реакции и ответной реакции с проверяемого блока 7; в-третьи через элементы задержки 35 и 40 он поступает на вход элемента И 31 и подготавливает путь прохождения сигнала НСРВ от блока 4 сравнения через элемент И 31. Элемент 40 задержки рассчитан на время сравнения реакций .и предназначен для устранения ложных срабатываний элемента И 31. Резуль- .тат сравнения может быть двояким, поэтому рассмотрим оба случая.

Если ответная реакция не совпала с ожидаемой, то с блока 4 сравнения в блок 6 управления въщается сигнал

1

НСРВ. Этот сигнал проходит через элементы И 25 и 26 и вырабатывает разрешение на считывание с блока 1 памяти тестов и передачу в блок 2 памяти очередного ТН.

Если ответная реакция совпала с эталонной, то сигнал НСРВ с блока 4 сравнения отсутствует. В этом случа на выходе элемента НЕ 43 присутствует единица, и в момент времени, опрделяемый элементом 40 задержки, на выходе элемента И 31 появляется единичный сигнал, который во-первых устанавливает в единицу триггер 45 пуска, т.е. переводит блок 6 управления в режим переадресации; во-вторых, поступает в блок 9 регистрации адресов и разрешает запись адреса ТН, поступающего из блока 8 анализа места неисправности} в-третьих, по истечении времени, необходимого для записи адреса ТН в блок 9 регисрации адресов и определяемого элементом 37 задержки, он поступает в блок 9 регистрации адресов и разрешает сдвиг информацииJ в-четвертых, через элементы задержки 37, ИЛИ 21 он поступает в блок 8. анализа места неисправности и осуществляет выбор адреса следующего ТН, на котором не обходимо произвести сравнение эталонной и полученной от проверяемого блока 7 реакщ1й{ в-пятых, по истечении времени, необходимого для изменения адреса в блоке анализа места неисправности и определяемого элементом 38 задержки, через элементы задержки 37, ИЛИ 21, задержки 38 он вырабатывает разрешение на считывание блока 1 памяти тестов и передачу в блок 2 памяти очередного ТН.

Если триггер 45 пуска находится в единице, то прохождение сигнала КТН1 через элементы И 28 и 29, определяется наличием или отсутствием сигнала НСРВ от блока 8 анализа места неисправности. Поэтому дальнейшую работу блока 6 управления рассмотрим в двух режимах: необходимый ТН еще не найден (сигнал НСРВ присутствует)J необходимый ТН найден (сигнал НСРВ отсутствует).

Если сигнал НСРВ от блока 8 анализа места неисправности присутствует, то сигнал КТН1 с выхода элемен- та 36 задержки, рассчитанного на время, необходимое для вьфаботки сигнала НСРВ в блоке 8 анализа мес

15

20

25

зо

25448812

та неисправности, проходит через элемент И 28 и разрешает считывание блоку 1 памяти тестов и подачу в блок 2 памяти очередного ТН. , Если сигнал НСРВ от блока 8 отсутствует, то сигнал KTHt проходит через элементы И 29, ИЛИ 19 и обеспечивает по сигналам КОНТ1, КОНТ2 указанные действия по сравнению за- fO писанной в блоке 2 памяти эталонной реакции и ответной реакции с проверяемого блока 7. Результат сравнения может быть двояким, поэтому рассмотрим оба случая.

Если ответная реакция не совпала с ожидаемой, то с блока 4 сравнения в блок 6 управления вьщается сигнал НСРВ. Этот сигнал поступает во-первых, через элементы И 25 и 32, ИЛИ 21 в блок 8 и осуществляет выбор адреса следующего ТН, на котором необходимо произвести сравнение эталонной и полученной от проверяемого блока 7 реакций; во-вторых, по истечении времени, необходимого для изменения адреса в блоке 8 и определяемого элементом 38 задержки, через элементы И 25 и 32, ШШ 21, элемент 38 задержки он вырабатывает разрешение на считывание блоку памяти тестов и передачу в блок 2 памяти памяти очередного ТН. Если ответная реакция совпала с ожидаемой, то осуществляются указанные действия.

Если тестовый набор содержит метку КТПД, то через регистр 10 сигнал КТПД1 поступает в блок 5 индикации и разрешает индикацию адресов ТН, на которых при прохождении теста поиска дефектов произошло сравнение реакций, поступающих из блока 9 регистрации адресов.

Работа блока 6 управления в режиме поиска дефектов последователь- ностных схем может быть повторена подачей сигнала Пуск на вход 12.

Работа блока 8 анализа мае- та неисправности (фиг. 3) начинается с обнуления счетчиков 48 и 49, а также регистра 47 по сигналам соответственно СчЛ О и СчН О QT блока 6 управления. Дальнейшую работу рассмотрим в двух режимах: комбинационные и последовательные схемы.

35

40

45

50

55

В режиме КС по команде от блока 6 управления СчН ч- 1 счетчик 49 вырабатывает текущий номер класса

эквивалентных дефектов и вьщает его в блок 5 индикации.

В реясиме ПС по командам от блока 6 управления СчЛ + 1 и СчН + 1 счет- чижи 48 и 49 формируют текущий адрес анализируемого тестового набора и вьщают его на входы соответственно схем 50 и 51 сравнения, которые, в свою очередь 5 вместе с элементом ИЛИ 52 формируют сигнал несравнения НСРВ для выдачи его в блок 6 управления. На первый вход обоих схем сравнения поступает информация из регистра 47. Обновление информации в регистре 47 адреса происходит во время цикла переадресации, когда по сигналу ПРА от блока 6 управления по адресу текущего тестового набора, образованного содержимым счетчиков 48 и 49, в регистр 47 считывается информация из блока 46 памятиi При этом, во время цикла переадресации содержимое обоих счетчиков 48 и 49 поступает в блок 9 регистрации адресов для записи и последующей индикации в блоке 5 индикации.

Работа блока 9 (фиг. 4) начинается с обнуления всех регистров 53 по сигналу УСТ О блока 6 Управления Затем в цикле переадресации по сигналу ЗПТН от блока 6 управления адрес тестового набора, на котором произошло сравнение эталонной реакции с ожидаемой, поступает в параллельном коде от блока 8 и записывается в младшие разряды всех регистров 53. Затем блок 6 управления вьщает сигнал СДВ, который попадает на управляющий вход всех регистров 53 и обеспечивает сдвиг информации из младших разрядов в старшие, что позволяет сохранить все адреса тестовых наборов, на которых произошло сравнение эталонной реакции с ожидаемой. Вся информация из блока 9 в конце работы устройства в режиме ПС индицируется в блоке 5 индикаций I . ..

На фиг. 10 показан пример теста поиска дефектов для последовательностной схемы. Тест состоит из 6 лучей. Лучи следуют в тесте в порядке возрастания номеров. Точки пересечения лучей и вертикальных линий (фиг. 7) имеют двойную нумерацию, например, на луче 1 выделены две точки 1-4 и 1-8, в обозначениях которых 1 - номер луча, 4, 8 - номера тестовых наборов. При этом 1-4 и 1-8 - различные адреса двух тестовых наборов. Рассмотрим два примера.

Пусть для КЭЛ Kj на данном множестве лучей в тесте построен k-иден- тификатор, которому соответствует множество адресов ТН: 1-4, 3-5, а . для КЭЛ К,, построен k -идентификатор, которому соответствует множество адресов ТН: 1-8, 4-7. Как видно,

оба эти идентификатора не содержат одинаковых адресов ТН. Пусть также, они не содержат одинаковых адресов с любым другим k-идентификатором в тесте. Цепочки адресов всех идентификаторов хранятся в блоке 46 памяти. При этом, для выхода из теста всякую цепочку замыкает фиктивный адрес 7-6, значение которого больше максимального реального адреса 6-12.

До получения первого сравнения из блока 4 сравнения устройство последовательно анализирует реакцию проверяемого блока на ТН с адресами 1-1, 1-2 и т.д. При наличии в проверяемом

блоке дефектов из КЭД Kg на ТН с адресом t-4 вырабатывается сигнал сравнения ответной реакции с ожидаемой. После этого производится уста- новка режима переадресации в устройстве и вместо последовательного

анализа реакций на ТН в порядке возрастания их адресов, анализируются реакции на ТН по цепочке адресов. Таким образом, после получения сигнала сравнения на ТН с адресом 1-4 вместо анализа на следующем этапе реакции на ТН с адресом 1-5, будет анализироваться реакция на ТН с адресом, который определяется следующим путем: в цикле переадресации по адресу 1-4 из ПЗУ 46 в блоке 8 адреса считывается адрес перехода 3-5, а адрес 1-4 запоминается в блоке 9 регистров.

После того, как ТН с данным адресом находится на перфоленте, осуществляется его подача на проверяемый блок 7 и, так как в блоке присутствуют дефекты из КЭД К,, снова формируется сигнал сравнения и организуется новый цикл переадресации. В результате по адресу 3-5 из ПЗУ 46 считьгоается фиктивный адрес 7-6, а адрес 3-5 запоминается в блоке 9 регистров. Далее устройство при попытке считать тестовый набор с адресом 7-6 с перфоленты считывает метку КТПД1. Так как в режиме переад

ресации при получении сигнала сравнения соответствующие адреса из цепочек запоминаются в блоке регистров, то считывание метки КТПД1 при- ,водит к индикации следующего содержимого блока регистров: t-4, 3-5. По этим адресам определяем и устраняем Кд.

Пусть для КЭД Kg построен k -идентификатор, которому соответствует множество адресов ТН: 1-4, 3-5, а для КЭД Kj построен 1с -идентификатор которому соответствует множество адресов ТН: 1-4, 1-8, 4-7. Как видно, оба эти идентификаторы содержат первым один и тот же адрес 1-4. Пусть также, они не содержат одинаковых адресов с любым другим k -идентификатором. При наличии в проверяемом блоке дефектов из КЭД К, или К на ТН с адресом 1-4 вырабатывается сигнал сравнения ответной реакции с ожидаемой. После этого производится установка режима переадресации в устройстве и вместо последо- нательного анализа реакций на ТН в порядке возрастания их адресов анализируются реакции на ТН по цепочке адресов. Однако, в отличие от первого примера, для устранения неодно- значности переходов в цепочках 1-4, 3-5 и 1-4, 1-8 организуют цепочку 1-4, 1-8, 3-5, 4-7, 7-6, которая получается объединением цепочек обоих идентификаторов.

Таким обрязом, после получения сигнала сравнения на ТН с адресом 1-4, вместо анализа на следующем этапе реакции на ТН с адресом 1-5, будет анализироваться; реакция на ТН с адресом, который определяется следующим путем: в цикле переадресации по адресу 1-4 из ПЗУ 46 в блоке 8 считывается адрес переходов 1-8, а адрес 1-4 запоминается в блоке ре- гистра. После того, как ТН с данньж адресом 1-8 находится на перфоленте, осуществляется его подача на проверяемый блок 7 и анализируется ответная реакция. При этом результат мо- жег быть двояким. Рассмотрим оба варианта.

Произошло сравнение ответной реакции с ожидаемой. В результате организуется новый цикл переадресации и по адресу Т-8 из ПЗУ 46 в блоке 8 считывается адрес 3-5, а адрес 1-8 запоминается в блоке 9. Пусть

o

5

на ТН с адресом 3-5 вырабатывается сигнал НСРВ Б блоке 4 сравнения. Поскольку устройство уже работает в режиме переадресации, организуется 5 новый цикл переадресации, в результате которого из ПЗУ 46 по адресу 3-5 считывается адрес 4-7. Однако, вследствие наличия сигнала НСРВ от блока 4 сравнения, адрес 3-5 не запоминается в блоке 9 регистров. Пусть на ТН с адресом 4-7 происходит сравнение реакций, в результате чего из блока 46 по адресу 4-7 считывается фиктивный адрес 7-6, а адрес 4-7 запоминается в блоке 9. При попытке найти на ленте ТН с адресом 7-6 блок 6 управления определяет метку КТПД1, что ведет к индикации содержимого блока регистров, т.е. 1-4, 1-8, 4-7, по которому определяют и устраняют Kj.

Произошло несравнение ответной реакции с ожидаемой. При этом в блоке 4 сравнения формируется сигнал НСРВ. Поскольку устройство уже работает в режиме переадресации, организуется новый цикл переадресации, в результате которого из блока 46 памяти по адресу 1-8 считывается адрес 3-5. Однако, вследствие наличия сигнала НСРВ от блока 4 сравнения, адрес 1-8 не запоминается в блоке 9.. Пусть на ТН с адресом 3-5 происходит сравнение ответной реакции с ожидаемой, в результате чего в цикле переадресации адрес 3-5 запоминается в блоке 9, а из ПЗУ 46 по адресу 3-5 считывается адрес 4-7. Пусть на ТН с адресом 4-7 блок 4 сравнения вырабатывает сигнал НСРВ. Тогда по адресу 4-7 из ПЗУ 46 считывается фиктивный адрес 7-6, а предыдущий адрес 4-7 в блоке 9 не запоминается. Таким образом, при считывании метки КТПД1 происходит индикация содержимого блока регистров 1-4, 3-5, по которому определяют и устраняют К,.

Формула изобретения

Устройство для контроля- и диагностики дискретных блоков, содержащее блок памяти тестов, блок памяти, блок сравнения, блок анализа места неисправностей, блок управления и коммутатор, блок управления содержит регистр, причем первый выход

17

блока управления соединен с входом синхронизации блока сравненияi выход несравнения котор ого соединен с первым входом логических условий блока-управления, второй выход которого соединен с входом записи блока памяти, группа информационных входов которого соединена с группой выходов признака тестового слова блока памяти тестов, вход разрешения считывания слова признаков входов (выходов), вход считьюания, вход разрешения считывания следующего тестового слова и вход адреса

метки, конец тестового набора блока памяти тестов соединен с третьим четвертым, пятым и шестым выходами блока управления, седьмой, восьмой, девятый, десятый и одиннадцатый выходы которого соединены с перзьм, вторым, третьим, четверти и пятым входами блока анализа места неисправностей, первьй выход которого г соединен с вторым входом логических условий блока управления, группа входов (выходов) коьй утатора соединена с группой входов (выходов) диагностируемого дискретного блока, при этом блок анализа места неисправностей содержит первую схему сравнения, регистр номеров, группа выходов признака текущего адреса тестового слова которого соединена с первой группой информационных входов первой схемы сравнения, о личающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения контроля дискретных блоков, содержащих комбинационные схемы и схемы, содержащие элементы памяти, оно содержит блок регистрации адресов, блок индикации, а в блок анализа места неисправностей введены счетчик текущго адреса тестового слова, счетчик но мера дефекта, вторая схема сравнёТШ элемент ИЛИ и блок памяти адресов, причем суммирующий вход счетчика номера дефекта соединен с седьмым выходом блока управления, восьмой выход которого соединен с входом считьгоания блока памяти адресов, группа выходов которого соединена с группой информационных входов регистра номеров, группа выходов признака текущего адреса которого соединены с второй группой информационных входов первой схемы сравнения.

т

10

15

20

, е-я, 1254488

выход несравнения которой соединегГ с первым вхбдом элемента. ИЛИ, второй вход которого соединен с выходом несравнения второй схемы сравне- 5 ния, первая ti вторая группы информационных входов которой соединены с группой разрядных выходов счетчика номера дефекта и с группой выходов признака номера дефекта в текущем тестовом слове регистра ров соответственно, при этом группа разрядных выходов счетчика тгку- щего адреса тестового слова и группа выходов счетчика номера дефекта соединены с первой и второй группами информационных входов блока регистрации адресов, а группа разрядных выходов счетчика текущего адреса соединена с первой группой информационных входов блока индикации, входы сброса счетчика текущего адреса тестового слова и счетчика номера дефекта соединены с десятым и девятьм выходами блока управления, 25 суммирующий вход счетчика текущего адреса тестового слова соединен с одиннадцатым выходом блока управления, выход элемента ИЛИ соединен с вторьи входом логических условий блока управления, гвуппа выходов которого соединена с группой управляющих входов коммутатора, двенадцатый, тринадцатый и четырнадцатый выходы блока управления соединены с входом сброса, входом синхронизации и входом записи блока регистрации адресов соответственно, пятнадцатый и шестнадцатый выходы блока управления соединены с информационными входами блока индикации, вторая группа информационных входов которого соединена с группой выходов блока регистрации адресов, группа выходов признака микрооперации блока памяти тестов соединена с группой входов логической операции, блока управления , группа выходов признака тестов блока памяти тестов соединена с группой информационных входов коммутатора, группа выходов которого соединена с первой группой информационных входов блока сравнения, вторая группа информационных входов которого соединена с группой выходов признака эталонного отклика блока памяти, вход разрешения которого соединен с входом пуС- ка устройства, при этом блок управления содержит регистр микрокоманд.

У)

- 35

40

50

55

19

триггер пуска, триггер управления, девять элементов ИЛИ, восемь элементов задержки, три элемента НЕ и десять элементов И, причем группа информационных входов регистра микркоманд соединена с группой входов логической операции блока управления , первый вход логического услови которого соединен с первым входом первого элемента И и через первый элемент НЕ - с первым входом второго элемента И, второй вход логического условия которого соединен с первьши входами третьего и четвертого элементов И и через второй элемент НЕ - с первым входом пятого элемента И, вход запуска блока управления соединен с третьим выходом блока управления, первым входом первого элемента ИЛИ, с нулевыми входами триггера пуска и триггера управления, с первым входом второго элемента ИЛИ, с девятым и двенадцатым выходами блока управления, перв выход которого соединен с выходом третьего элемента ИЛИ, первый вход которого соединен с выходом первого элемента задержки-и через второй элемент задержки - с первым входом шестого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ и первьм входом четвертого элемента ИЛИ, выход которого соединен с-пятым выходом блока управления, второй выход которого соединен с выходом пятого элемента ИЛИ первый вход которого соединен с выходом признака конца тестового набора для контроля комбинационных схем регистра микрокоманд и с входом первого элемента задержки, группа выходов признаков входов (выходов) регистра микрокоманд соединена с группой информационных входов регистра, группа выходов которого соеди-. нена с группой выходов блока управ- ления, выход признака конца коммутационного теста регистра микрокоманд соединен с первьм входом седьмого элемента И, с вторым входом четвертого элемента ИЛИ и третьим входом первого элемента ИЛИ, выход которого соединен с четвертью выходом блока управления, шестой выход которого соединен с выходом третьего элемента И и через третий элемент НЕ - с вторым входом шестого элемента И, выход признака конца тестового набора в режиме диагностики элементов

25

25448820

памяти регистра микрокоманд соединен с первым входом шестого элемента ИЛИ и через третий элемент задержки - с вторыми входами первого , и второго элементов И и первым входом восьмого элемента И, выход которого соединен с первым входом седьмого элемента ИЛИ, выход которого соединен с вторым входом пято1Q го элемента ИЛИ и через четвертый элемент задержки - с вторым входом третьего элемента ИЛИ, и через четвертый элемент задержки - с вторым входом пятого элемента И, выход коf5 торого соединен с единичным входом триггера пуска, с четырнадцатым выходом блока управления, через шестой элемент задержки - с первым входом восьмого элемента ИЛИ и с три-:

20 надцатым выходом блока управления,

выход начальной установки регистра микрокоманд соединен с вторым входом второго элемента ИЛИ, с единичным входом триггера управления, с одиннадцатым выходом блока управления и через седьмой элемент задержки - с четвертым входом первого элемента ИЛИ и третьим входом четвертого элемента ИЛИ, выход признака конца теста поиска дефектов в режиме контроля комбинационных- схем регистра микрокоманд соединен с третьим входом второго элемента ИЛИ и первым входом девятого элемента ИЛИ, второй выход которого соединен с выходом признака конца контроля регистра микрокоманд, выход признака конца теста поиска дефектов в режиме контроля элементов памяти которого соединен с шестнадцатым выходом блока управления, пятнадцатый выход

30

40

которого соединен с выходом девятого элемента ИЛИ, седьмой, восьмой и десятый выходы блока управления соединены с выходом шестого элемента ИЛИ, с выходом восьмого элемента ИЛИ и выходом второго элемента ИЛИ соответственно, при этом выход восьмого элемента и соединен через восьмой элемент задержки с пятым входом первого элемента ИЛИ и четвертым выходом четвертого элемента ИЛИ, единичный выход триггера пуска соединен с третьим входом первого элемента И, с третьим входом второго элемента И и первым входом девятого элемента И, выход которого соединен с вторьн входом восьмого элемента

21

ИЛИ, нулевой выход триггера пуска соединен с вторым входом восьмого элемента И и первым входом десятого элемента И, второй.вход которого соединен с вьрсодом четвертого элемента И и вторым входом девятого элемента И, единичный выход триггера управления соединен с вторым входом четвертого элемента И, нулевой выход триггера управления соединен с вторыми входами третьего и седьмого элементов И, выход которого соединен с вторым входом шестого

448822.

элемента ИЛИ, выход первого элемента И соединён с шестым и пятым входами соответстве шого первого и четвертого элементов ИЛИ, выход второ- 5 го элемента И соединен с вторьм

входом седьмого элемента ШШ, с восьмым входом первого элемента ИЛИ, соединенного с входом перепуска устройства при обнаружении дефектов, 10 выход десятого элемента И соединен с седьмым входом первого элемента ИЛИ и с шестым входом четвертого элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поиска дефектов цифровых узлов | 1985 |

|

SU1302282A2 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для поиска дефектов логических блоков | 1984 |

|

SU1221654A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для диагностирования группы из @ логических узлов | 1985 |

|

SU1390611A1 |

| Устройство для контроля цифровых печатных узлов | 1983 |

|

SU1179233A1 |

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

Изобретение относится к области автоматики и вычислительной техники: к устройствам контроля работоспособности и поиска дефектов дискретных узлов и блоков. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля схем и дискретных блоков, содержащих комбинационные схемы и элементы памяти. Устройство содержит блок памяти тестов, блок памяти, блок сравнения, блок анализа места неисправности, блок управления, коммутатор, блок регистрации адресов и блок индикации. В первом режиме диагностики проверяются комбинационные схемы, а во .втором - последовательные схемы, те же, что содерзкат элементы памяти. Обеспечен режим переадресации при вьгавлении дефекта. Автоматически фиксируются адреса тестовых наборов и номера дефектов, 10 ил. с S (Л

Omln. в ftCPS

Явт я

;---§ гг -да Hh

-dEEEH

ifim

т

вт1л9

ш

14«E« J

I

9ив «

I Иаиам йя установм I вяем у1уо6 вна, fmna

«

vix/nu уг оаявния, ОЛОКа pfeucmpota адреса

f-i1::.

Cwmieonif lraммymвцu нею itfcma. Пебч/мчтие OucufMniHoK вяна Wffi мигмуяютар я вмтм мимяяи

а авненил

Ягт

firm

MeMWHt ма fAimnif tettfHntMete evtmrnxa ноMtpa маеев мЛиввлттныя fff fftnio6

Е

vtemfudmta

я етвдвм навара е вмиа МвОвв iMf тиапи

9ив.9

Г

ф

Общ/ленив cvimwHa

номера я/юсса 3Keuga/ tm i ift Mimae

tHOwmifte fSian инвотции соУертимвк cv#«wm MtMw ююсев

квавампттх дв еяаюв

Д.

( WAifUj

CpaiHtwe ввлом гуювмвния einftmaS teamtttu от виагретме вяот е мтваиюЛ оаЛчпмой f«an4Ufu

ЛРЯ

W.J-

I Пювмвтна

MtPjMywwwtf дометт

IНПРП

fut. Л

Г

нoм

Овпуяение счетчика номера гпвспюйойо HaSoita

.«.

I УОетченив т едим1цу 1Яввришмвеа счётчика яуией

Начаг ай уьлюяовт дискретюы йлока

з:

-.fg.

I воереЛюев I ткгповоео HoSopa в djiw памяти

НнЛтаци в Seoxf

IaHffumvuu номеров тктовы

JJт

I OMVMMtw на гЛшачу I совчаяимово etinrnu I , ff Tfio6o поборе

Сравтте в вмт ераОнения ответной реакции от Оиеирвтиаавм- иа с атЛггмвЛ ваентаб рвамца

Г

йыйщ аврвса cMOtflo- ито тюпойовонввё в V oftfffff оЛлсв .

29

Срабнете 9 блонв сравнения ответное реакции от виекреа- нога блока comaOat- мвй опЛвтпа рвтчойд

Heift

Г Установка ринима I переаврвсовми J

Г Зато, I теетовога яавора I из Люна авовеа в б/юк цееаапрвв

Г

л

стаин мрмвчш 9 важ fftuemppe

ол

Pvi.S

«в

НОМ№

-1-44-1л У

.f i S k S е 7 а в ft ii. Ивмц тветввоав 9и 10

Редактор И.Касарда

Составитель А.Сиротская

Техред И.Попович Корректор А.Обручар

4722/53

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Устройство для контроля и диагностики дискретных объектов | 1980 |

|

SU942025A1 |

| Устройство для контроля и диагностики дискретных объектов | 1983 |

|

SU1109756A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-30—Публикация

1985-01-11—Подача