1

Изобретение относится к автоматике и вычислительной технике, а именно к устройствам контроля работоспособности и диагностирова1шя цифровы узлов и блоков, и является усоверше ствованием устройства по авт.св. № 962957,

Целью изобретения является повышние достоверности контроля.

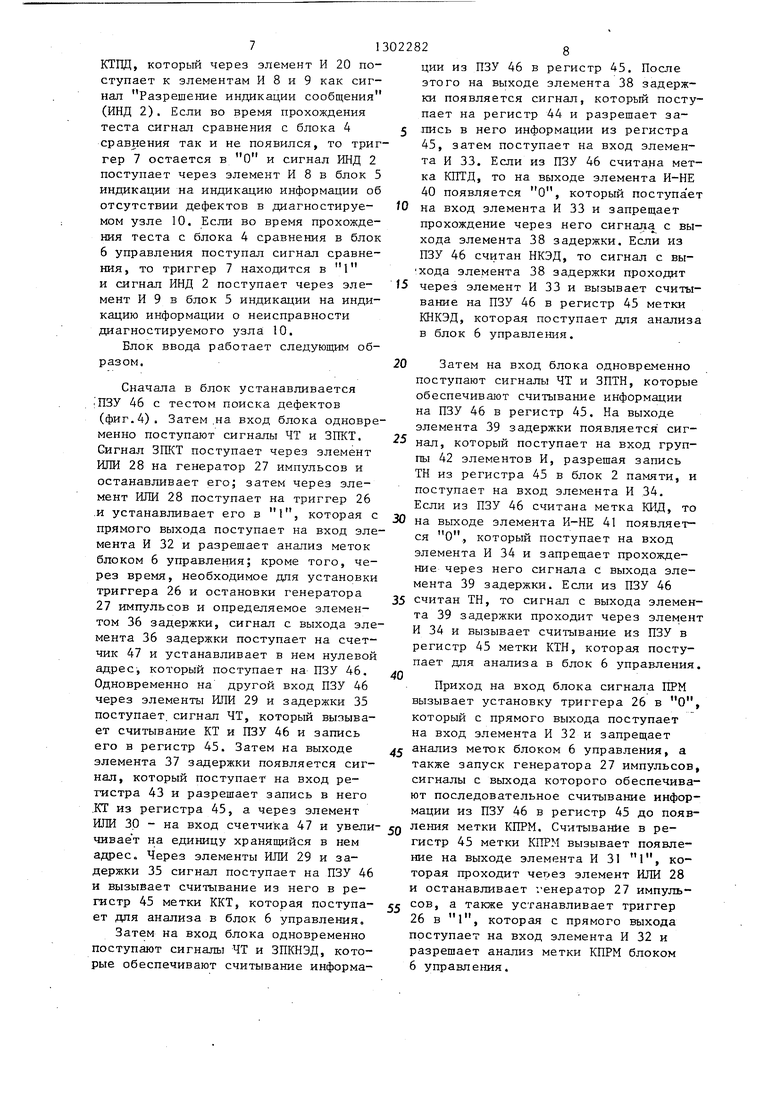

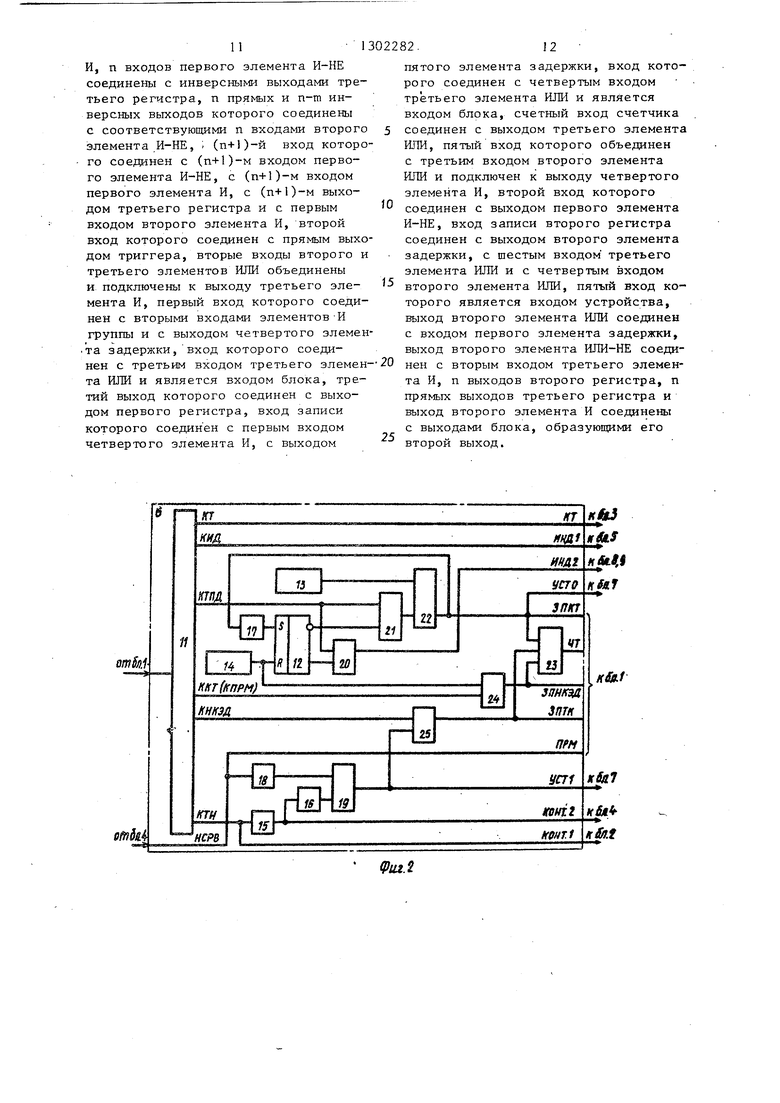

Для осуществления процесса.диагностирования используется тест поиска дефектов из идентификаторов, оргнизованный следующим образом. В каждом идентификаторе выбирается один тестовый набор, обладающий наибольшей обнаруживаемой способностью к возможным дефектам. Этот тестовый нбор становится в идентификаторе на первое место. Множество таких наборов дпя всех идентификаторов теста поисков дефектов образует проверяющий тест, на котором обнаруживаются проявляющиеся на тесте дефекты. Таким образом, с помощью теста поиска дефектов осуществляется поиск дефектов, а с помощью содержащегося в тесте поиска дефектов проверяющего теста обнаруживаются такие дефекты, при которых в проверяющем тесте искжаются ответные реакции, но остановка на тесте поиска дефектов не проиходит .

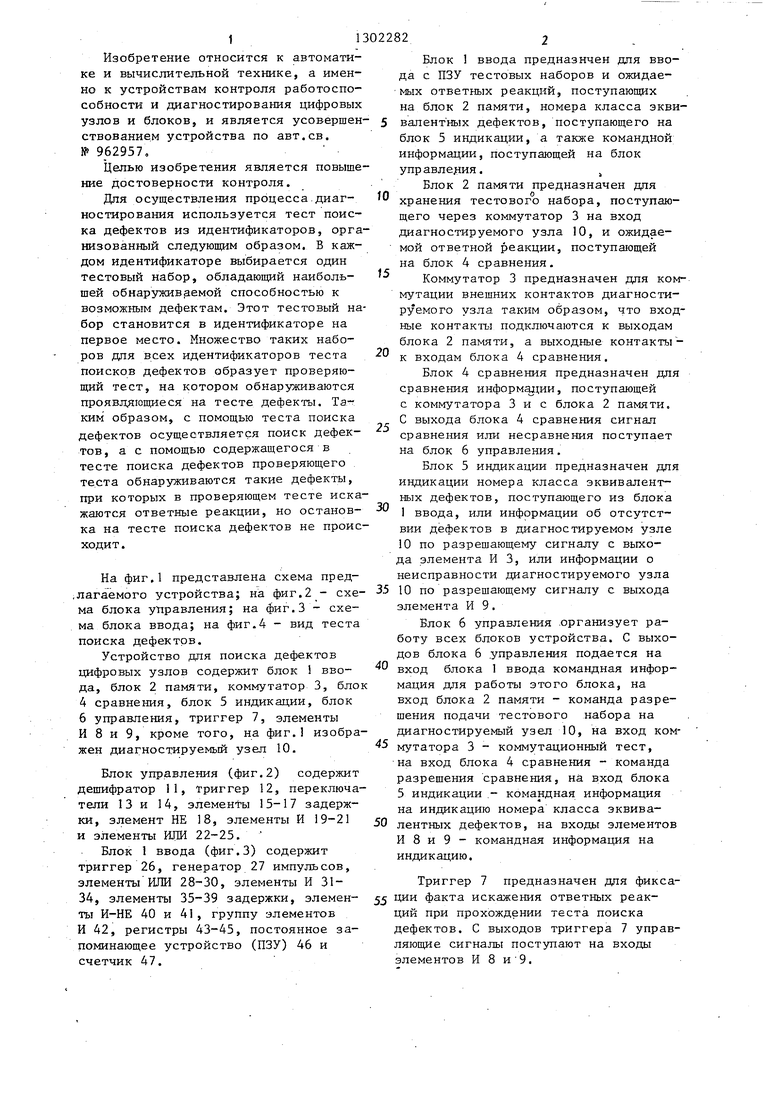

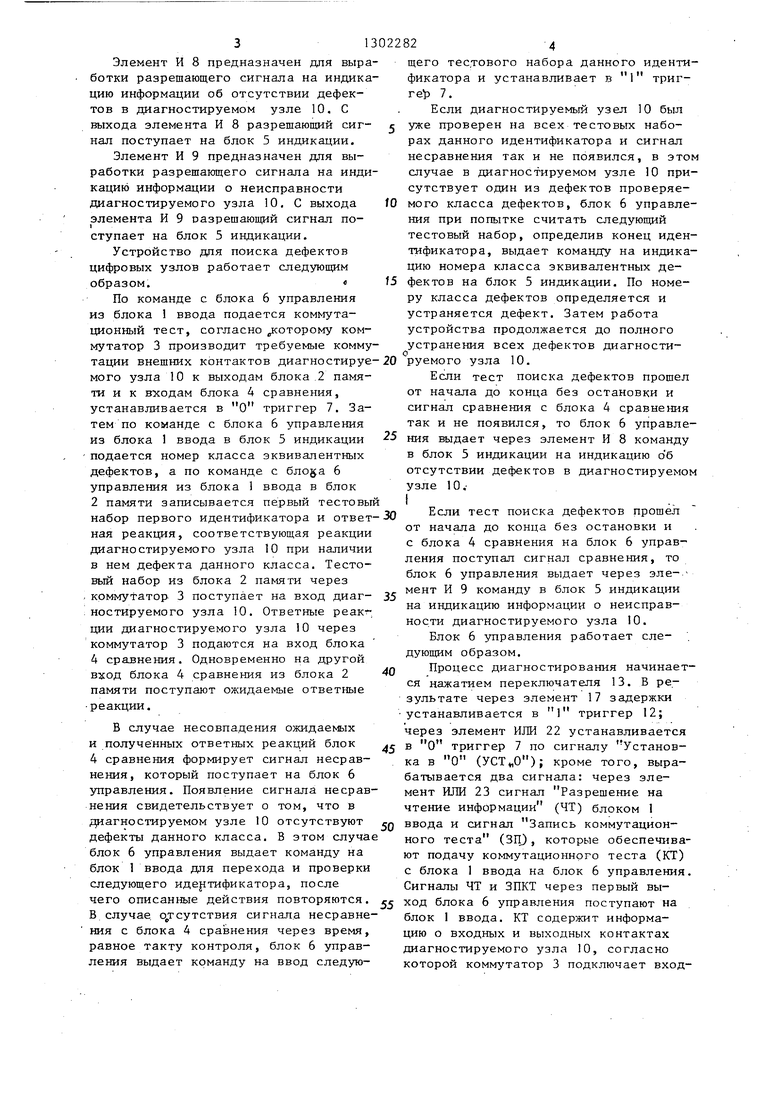

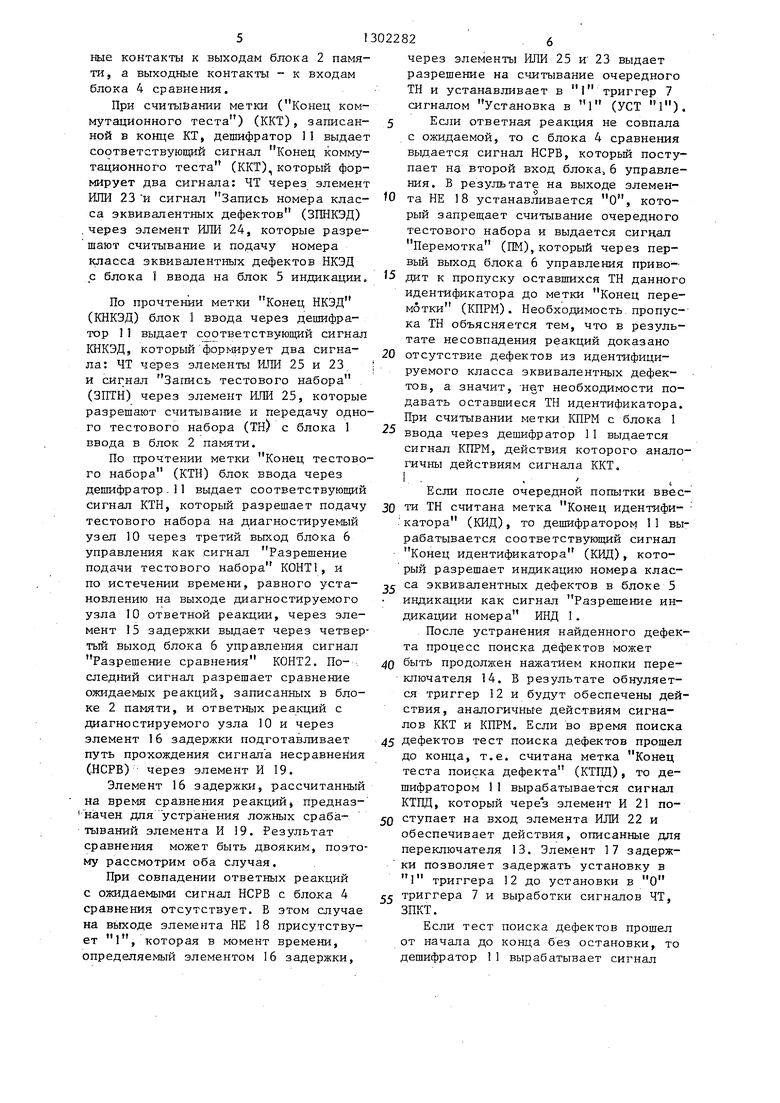

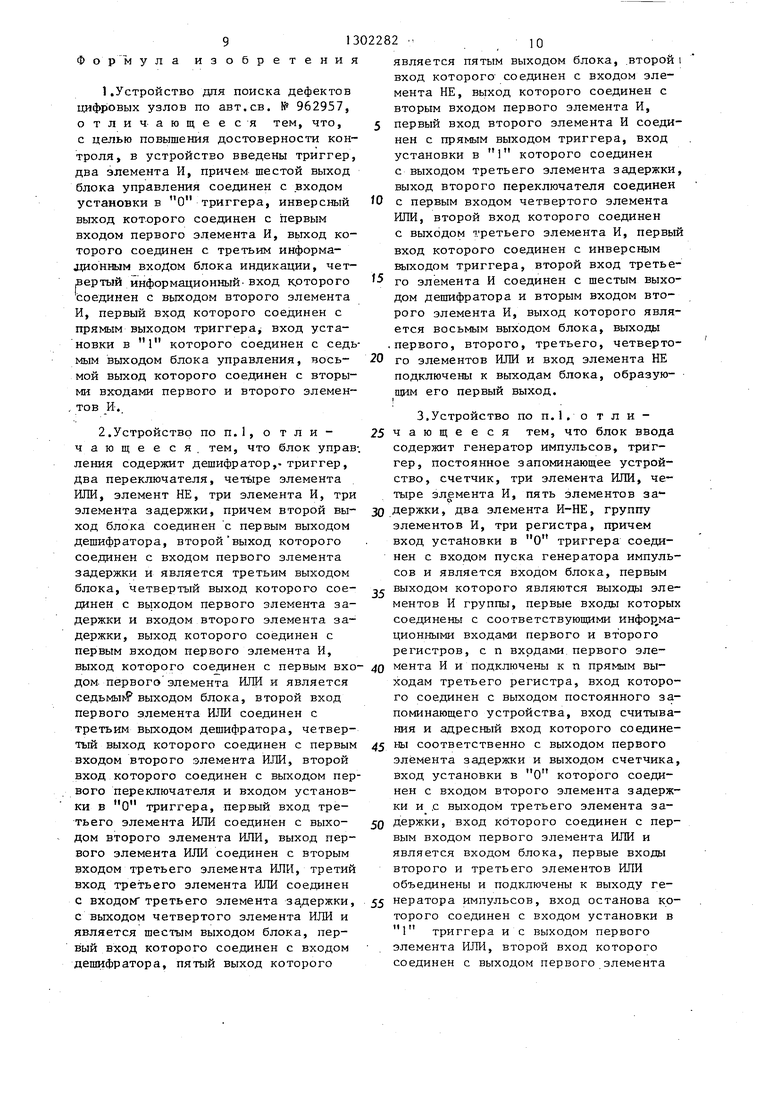

На фиг,1 представлена схема пред- .лагаемого устройства; на фиг.2 - схема блока управления; на фиг.З - схема блока ввода; на фиг.4 - вид теста поиска дефектов.

Устройство для поиска дефектов цифровых узлов содержит блок 1 ввода, блок 2 памяти, коммутатор 3, бло 4 сравнения, блок 5 индикации, блок 6 управления, триггер 7, элементы И 8 и 9, кроме того, на фиг.1 изображен диагностируемый узел 10.

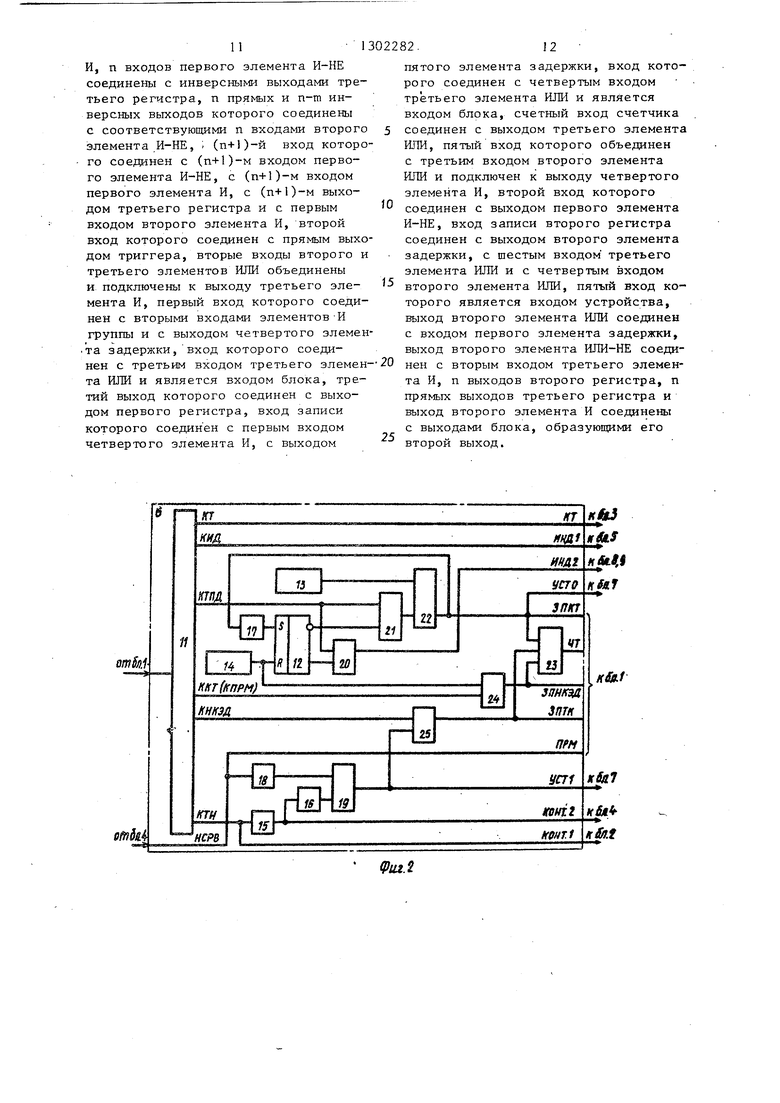

Блок управления (фиг.2) содержит дешифратор 11, триггер 12, переключатели 13 и 14, элеменфы 15-17 задержки, злемент НЕ 18, элементы И 19-21 и элементы ИЛИ 22-25.

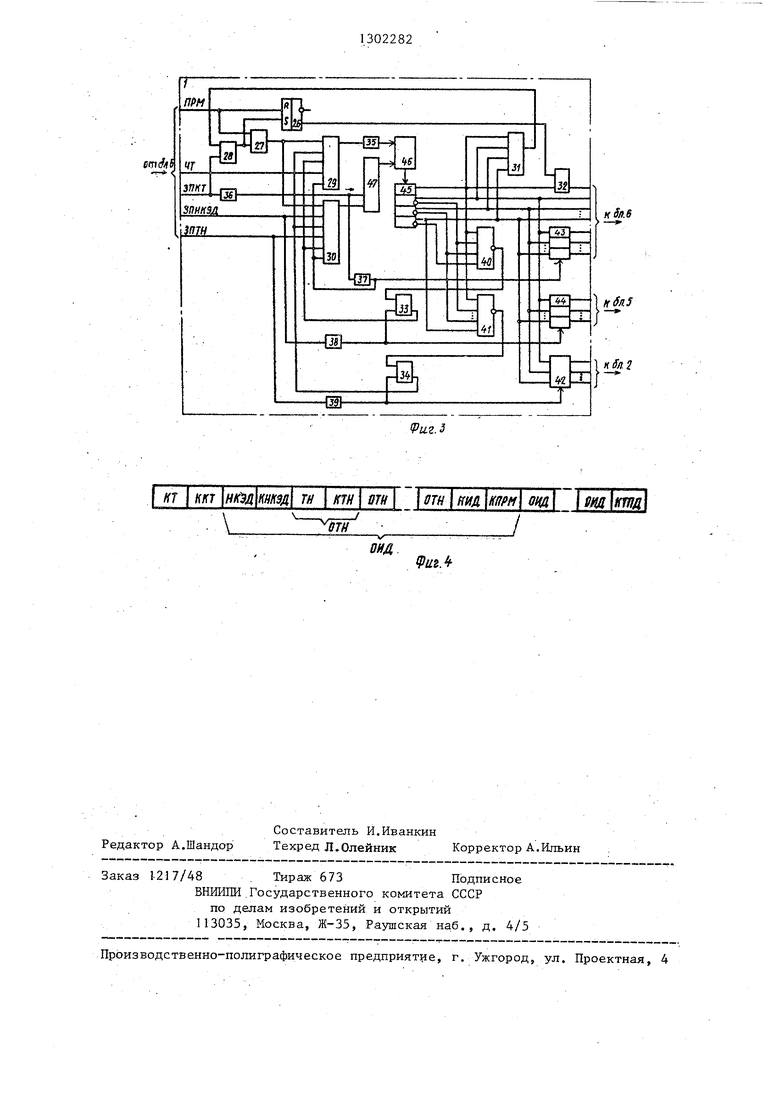

Блок 1 ввода (фиг.З) содержит триггер 26, генератор 27 импульсов, элементы ИЛИ 28-30, элементы И 31- 34, элементы 35-39 задержки, элементы И-НЕ 40 и 41, группу элементов И 42, регистры 43-45, постоянное за- цоминающее устройство (ПЗУ) 46 и счетчик 47.

Блок 1 ввода предназнчен дпя ввода с ПЗУ тестовых наборов и ожидаемых ответных реакций, поступающих на блок 2 памяти, номера класса экви- валент ных дефектов, поступающего на блок 5 индикации, а также командной

0

5

5

0

5

0

информации, поступающей на блок упр авледия.

Блок 2 памяти предназначен для

о

хранения тестового набора, поступающего через коммутатор 3 на вход диагностируемого узла 10, и ожидаемой ответной реакции, поступающей на блок 4 сравнения.

Коммутатор 3 предназначен для коммутации внешних контактов диагностируемого узла таким образом, что входные контакты подключаются к выходам блока 2 памяти, а выходные контакты- к входам блока 4 сравнения.

Блок 4 сравнения предназначен для сравнения информздщи, поступающей с коммутатора 3 и с блока 2 памяти, С выхода блока 4 сравнения сигнал сравнения или несравнения поступает на блок 6 управления.

Блок 5 индикации предназначен для индикации номера класса эквивалентных дефектов, поступающего из блока 1 ввода, или информации об отсутствии дефектов в диагностируемом узле 10 по разрешающему сигналу с выхода элемента И 3, или информации о неисправности диагностируемого узла 5 10 по разрешающему сигналу с выхода элемента И 9.

Блок 6 управления .организует работу всех блоков устройства, С выходов блока 6 управления подается на вход блока 1 ввода командная информация для работы этого блока, на вход блока 2 памяти - команда разрешения подачи тестового набора на диагностируемый узел 10, на вход ком- 5 мутатора 3 - коммутационный тест, на вход блока 4 сравнения - команда разрешения сравнения, на вход блока 5 индикации ,- командная информация на индикацию номера класса эквива- 0 лентных дефектов, на входы элементов И 8 и 9 - командная информация на индикацию.

Триггер 7 предназначен дпя фикса- 5 Ции факта искажения ответных реакций при прохождении теста поиска дефектов. С выходов триггера 7 управляющие сигналы поступают на входы элементов И 8 и 9.

0

Элемент И 8 предназначен для выработки разрешающего сигнала на индикацию информации об отсутствии дефектов в диагностируемом узле 10, С выхода элемента И 8 разрешающий сигнал поступает на блок 5 индикации.

Элемент И 9 предназначен для выработки разрешающего сигнала на индикацию информации о неисправности диагностируемого узла 10, С выхода элемента И 9 разрешающий сигнал поступает на блок 5 индикации.

Устройство для поиска дефектов цифровых узлов работает следующим образом.«

По команде с блока 6 управления из блока 1 ввода подается коммутационный тест, согласно оторому коммутатор 3 производит требуемые коммутации внешних контактов диагностируе-20 руемого узла 10.

мого узла 10 к выходам блока 2 памяти и к входам блока 4 сравнения, устанавливается в О триггер 7. Затем по команде с блока 6 управления из блока 1 ввода в блок 5 индикации

подается номер класса эквивалентных дефектов, а по команде с 6 управления из блока 1 ввода в блок 2 памяти записывается первый тестовый набор первого идентификатора и ответ- -30 ная реакция, соответствующая реакции диагностируемого узла 10 при наличии в нем дефекта данного класса. Тестовый набор из блока 2 памяти через

коммутатор 3 поступает на вход диагностируемого узла 10. Ответные реакг ции диагностируемого узла 10 через коммутатор 3 подаются на вход блока 4 сравнения. Одновременно на другой вход блока 4 сравнения из блока 2 памяти поступают ожидаемые ответные

реакции.

В случае несовпадения ожидаемых полученных ответных реакций блок 4 сравнения формирует сигнал несравнения, который поступает на блок 6 управления. Появление сигнала несравнения свидетельствует о том, что в диагностируемом узле 10 отсутствуют Q дефекты данного класса. В этом случае блок 6 управления выдает команду на блок 1 ввода для перехода и проверки следующего идентификатора, после

25

35

40

45

чего описанные действия повторяются. ход блока 6 управления поступают на В случае, отсутствия сигнала несравне- блок 1 ввода. КТ содержит информа- ния с блока 4 сравнения через время, равное такту контроля, блок 6 управления выдает команду на ввод следуюцию о входных и выходных контактах диагностируемого узла 10, согласно которой коммутатор 3 подключает вход

щего тестового набора данного идентификатора и устанавливает в 1 триг- те р 7.

Если диагностируемый узел 10 был

уже проверен на всех тестовых наборах данного идентификатора и сигнал несравнения так и не появился, в этом случае в диагностируемом узле 10 присутствует один из дефектов проверяемого класса дефектов, блок 6 управления при попытке считать следующий тестовый набор, определив конец идентификатора, выдает команду на индикацию номера класса эквивалентных дефектов на блок 5 индикации. По номеру класса дефектов определяется и устраняется дефект. Затем работа устройства продолжается до полного устранения всех дефектов диагности0

Q

Если тест поиска дефектов прошел от начала до конца без остановки и сигнал сравнения с блока 4 сравнения так и не появился, то блок 6 управле- 5 ния выдает через элемент И 8 команду в блок 5 индикации на индикацию о б отсутствии дефектов в диагностируемом узле 10 .

I

Если тест поиска дефектов прошел

от начала до конца без остановки и с блока 4 сравнения на блок 6 управления поступал сигнал сравнения, то блок 6 управления выдает через эле- - мент И 9 команду в блок 5 индикации на индикацию информации о неисправности диагностируемого узла 10.

Блок 6 управления работает сле- дyюшJ м образом.

Процесс диагностирования начинается нажатием переключателя 13. В результате через элемент 17 задержки устанавливается в 1 триггер 12; через элемент ИЛИ 22 устанавливается в О ка в

батывается два сигнала: через элемент ИЛИ 23 сигнал Разрешение на чтение информации (ЧТ) блоком 1 ввода и сигнал Запись коммутационного теста (ЗП), которые обеспечивают подачу коммутационного теста (КГ) с блока 1 ввода на блок 6 управления. Сигналы ЧТ и ЗПКТ через первый вы5

0

5

триггер 7 по сигналу Установ- 0 (); кроме того, выраход блока 6 управления поступают на блок 1 ввода. КТ содержит информа-

цию о входных и выходных контактах диагностируемого узла 10, согласно которой коммутатор 3 подключает входные контакты к выходам блока 2 памяти, а выходные контакты - к входам блока 4 сравнения.

При считывании метки (Конец коммутационного теста) (ККТ), записанной в конце КТ, дешифратор 11 выдает соответствующий сигнал Конец коммутационного теста (ККТ), который формирует два сигнала: ЧТ через элемент ИЛИ 23 и сигнал Запись номера класса эквивалентных дефектов (ЗПНКЭД) через элемент ИЛИ 24, которые разре- тают считывание и подачу номера класса эквивалентных дефектов НКЭД с блока 1 ввода на блок 5 индикации.

По прочтении метки Конец НКЭД (КНКЭД) блок 1 ввода через дешифратор 11 выдает соответствующий сигнал КНКЭД, который формирует два сигнаа; ЧТ через элементы ИЛИ 25 и 23 | сигнал Запись тестового набора , (ЗПТН) через элемент ИЛИ 25, которые азрешают считывание и передачу одного тестового набора (ТН) с блока 1 ввода в блок 2 памяти.

По прочтении метки Конец тестового набора (КТН) блок ввода через ешифратор -i1 выдает соответствующий сигнал КТН, который разрешает подачу тестового набора на диагностируемь й узел 10 через третий выход блока 6 управления как сигнал Разрешение подачи тестового набора КОНТ1, и по истечении времени, равного установлению на выходе диагностируемого узла 10 ответной реакции, через элемент 15 задержки вьщает через четвертый выход блока 6 управления сигнал Разрешение сравнения КОНТ2. По- . следний сигнал разрешает сравнение ожидаемых реакций, записанных в блоке 2 памяти, и ответных реакций с диагностируемого узла 10 и через элемент 16 задержки подготавливает путь прохождения сигнала несравнения (НСРВ) через элемент И 19.

Элемент 16 задержки, рассчитанный на время сравнения реакций предназ- начен для устранения ложных срабатываний элемента И 19. Результат сравнения может быть двояким, поэтоу рассмотрим оба случая.

При совпадении ответных реакций ожидаемыми сигнал НСРВ с блока 4 равнения отсутствует. В этом случае

а выходе элемента НЕ 18 присутству- II t tf

т

, которая в момент времени.

определяемый элементом 16 задержки.

через элементы ИЛИ 25 и 23 выдает разрешение на считывание очередного ТН и устанавливает в 1 триггер 7 сигналом Установка в Г (УСТ 1).

Если ответная реакция не совпала с ожидаемой, то с блока 4 сравнения выдается сигнал НСРВ, которьй поступает на второй вход блока, 6 управления. В результате на выходе элемента НЕ 18 устанавливается О, который запрещает считывание очередного тестового набора и выдается сигнал Перемотка (ПМ), который через первый выход блока 6 управления приво-дит к пропуску оставшихся ТН данного идентификатора до метки Конец перемотки (КПРМ). Необходимость, пропус- ка ТН объясняется тем, что в результате несовпадения реакций доказано

отсутствие дефектов из идентифицируемого класса эквивалентных дефектов, а значит, необходимости подавать оставшиеся ТН идентификатора. При считывании метки КПРМ с блока 1 ввода через дешифратор 11 выдается сигнал КПРМ, действия которого аналогичны действиям сигнала ККТ.

Если после очередной попытки ввести ТН считана метка Конец идентифи- катора (КИД), то дешифратором 1 1 вырабатывается соответствующий сигнал Конец идентификатора (КИД), кото- рый разрешает индикацию номера класса эквивалентных дефектов в блоке 5 индикации как сигнал Разрешение индикации номера ИНД 1.

. После устранения найденного дефекта процесс поиска дефектов может

быть продолжен нажатием кнопки переключателя 14. В результате обнуляется триггер 12 и будут обеспечены действия, аналогичны-е действиям сигналов ККТ и КПРМ. Если во время поиска

дефектов тест поиска дефектов прошел до конца, т.е. считана метка Конец теста поиска дефекта (КТЦД), то дешифратором 11 вырабатывается сигнал КТПД, который чере з элемент И 21 поступает на вход элемента Р1ПИ 22 и обеспечивает действия, описанные для переключателя 13. Элемент 17 задержки позволяет задержать установку в 1 триггера 12 до установки в О

триггера 7 и выработки сигналов ЧТ, ЗПКТ.

Если тест поиска дефектов прошел от начала до конца без остановки, то дешифратор 11 вырабатывает сигнал

КТПД, который через элемент И 20 поступает к элементам И 8 и 9 как сигнал Разрешение индикации сообщения (ИНД 2). Если во время прохождения теста сигнал сравнения с блока 4 сравнения так и не появился, то триггер 7 остается в О и сигнал ИНД 2 поступает через элемент И 8 в блок 5 индикации на индикацию информации об отсутствии дефектов в диагностируемом узле 10. Если во время прохождения теста с блока 4 сравнения в блок 6 управления поступал сигнал сравнения, то триггер 7 находится в 1 и сигнал ИНД 2 поступает через элемент И 9 в блок 5 индикации на индикацию информации о неисправности диагностируемого узла 10.

Блок ввода работает следующим образом.

Сначала в блок устанавливается ;ПЗУ 46 с тестом поиска дефектов (фиг.4). Затем .на вход блока одновременно поступают сигналы ЧТ и ЗГЖТ. Сигнал ЗПКТ поступает через элемент ИЛИ 28 на генератор 27 импульсов и останавливает его; затем через элемент ИЛИ 28 поступает на триггер 26 .и устанавливает его в 1, которая с прямого выхода поступает на вход элемента И 32 и разрешает анализ меток блоком 6 управления; кроме того, через время, необходимое для установки триггера 26 и остановки генератора 27 импульсов и определяемое элементом 36 задержки, сигнал с выхода элемента 36 задержки поступает на счетчик 47 и устанавливает в нем нулевой адрес, который поступает на ПЗУ 46. Одновременно на другой вход ПЗУ 46 через элементы ИЛИ 29 и задержки 35 поступает, сигнал ЧТ, который вызывает считывание КТ и ПЗУ 46 и запись его в регистр 45. Затем на выходе элемента 37 задержки появляется сигнал, который поступает на вход регистра 43 и разрешает запись в него .КТ из регистра 45, а через элемент ИЛИ 3.0 - на вход счетчика 47 и увели- чивае т на единицу хранящийся в нем адрес. Через элементы ИЛИ 29 и задержки 35 сигнал поступает на ПЗУ 46 и вызывает считывание из него в регистр 45 метки ККТ, которая поступает для анализа в блок 6 управления.

Затем на вход блока одновременно поступают сигналы ЧТ и ЗПКНЭД, которые обеспечивают считывание информации из ПЗУ 46 в регистр 45. После этого на выходе элемента 38 задержки появляется сигнал, который поступает на регистр 44 и разрешает за5 лись в него информации из регистра 45, затем поступает на вход элемента И 33. Если из ПЗУ 46 считана метка КПТД, то на выходе элемента И-НЕ 40 появляется О, который поступает

0 на вход элемента И 33 и запрещает прохождение через него сигнала с выхода элемента 38 задержки. Если из ПЗУ 46 считан НКЭД, то сигнал с вы- хода элемента 38 задержки проходит

5 через элемент И 33 и вызывает считывание на ПЗУ 46 в регистр 45 метки КНКЭД, которая поступает для анализа в блок 6 управления.

0 Затем на вход блока одновременно поступают сигналы ЧТ и ЗПТН, которые обеспечивают считыва1ше информации на ПЗУ 46 в регистр 45. На выходе элемента 39 задержки появляется сиг5 нал, который поступает на вход группы 42 элементов И, разрешая запись ТН из регистра 45 в блок 2 памяти, и поступает на вход элемента И 34. Если из ПЗУ 46 считана метка КИД, то

0 на выходе элемента И-НЕ 41 появляется о, который поступает на вход элемента И 34 и запрещает прохождение через него сигнала с выхода элемента 39 задержки. Если из ПЗУ 46

5 считан ТН, то сигнал с выхода элемента 39 задержки проходит через элемент И 34 и вызывает считывание из ПЗУ в регистр 45 метки КТН, которая поступает для анализа в блок 6 управления.

0

Приход на вход блока сигнала ИРМ

вызывает установку триггера 26 в О, который с прямого выхода поступает на вход элемента И 32 и запрещает

j анализ меток блоком 6 управления, а также запуск генератора 27 импульсов, сигналы с выхода которого обеспечивают последовательное считывание информации из ПЗУ 46 в регистр 45 до появQ ления метки КПРМ. Считывание в регистр 45 метки КПРМ вызывает появление на выходе элемента И 31 1, которая проходит через элемент ИЛИ 28 и останавливает . енератор 27 импуль-

с сов, а также устанавливает триггер 26 в 1, которая с прямого выхода поступает на вход элемента И 32 и разрешает анализ метки КПРМ блоком 6 управления.

о р м у л а и

9 зоб

1302282

р е т е н и я

яв вх ме вт

1.Устройство для поиска дефектов цифровых узлов по авт.св. № 962957, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены триггер два элемента И, причем шестой выход блока управления соединен с входом установки в О триггера, инверсный выход которого соединен с первым входом первого элемента И, выход которого соединен с третьим информа- дщонным входом блока индикации, четвертый информационный вход которого соединен с выходом второго элемента И, первый вход которого соединен с прямым выходом триггера, вход установки в 1 которого соединен с седьмым выходом блока управления, восьмой выход которого соединен с вторыми входами первого и второго элемен- , тов И-.,

2.Устройство по п.1, о т л и - чающееся, тем, что блок управ ления содержит дешифратор,-триггер. Два переключателя, четьфе элемента ИЛИ, элемент НЕ, три элемента И, три элемента задержки, причем второй выход блока соединен с первым выходом дешифратора, второй выход которого соединен с входом первого элемента задержки и является третьим выходом блока, четвертый выход которого соединен с выходом первого элемента задержки и входом второго элемента задержки, выход которого соединен с первым входом первого элемента И,

45

выход которого соединен с первым вхо- 40 мента И и подключены к п прямым вы- дом. первого элемента ИЛИ и является седьмыгР выходом блока, второй вход первого элемента ИЛИ соединен с третьим выходом дешифратора, четвертый выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом первого переключателя и входом установки в о триггера, первый вход третьего элемента ШШ соединен с выходом второго элемента ИЛИ, выход первого элемента РШИ соединен с вторым входом третьего элемента ИЛИ, третий вход третьего элемента ИЛИ соединен с ВХОДОМ третьего элемента за,даржки, с выходом четвертого элемента ИЛИ и является шестым выходом блока, первый вход которого соединен с входом дешифратора, пятый выход которого

50

55

ходам третьего регистра, вход которо го соединен с выходом постоянного за поминающего устройства, вход считыва ния и адресный вход которого соедине ны соответственно с выходом первого элемента задержки и выходом счетчика вход установки в О которого соединен с входом второго элемента задерж ки и с выходом третьего элемента задержки, вход которого соединен с пер вым входом первого элемента ИЛИ и является входом блока, первые входы второго и третьего элементов ИЛИ объединены и подключены к выходу генератора импульсов, вход останова ко торого соединен с входом установки в 1 триггера и с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента

10

является пятым выходом блока, .второй i вход которого- соединен с входом элемента НЕ, выход которого соединен с вторым входом первого элемента И,

первый вход второго элемента И соединен с прямым выходом триггера, вход установки в 1 которого соединен с выходом третьего элемента задержки, выход второго переключателя соединен

с первым входом четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с инверсным выходом триггера, второй вход третьего элемента И соединен с шестым выходом дешифратора и вторым входом второго элемента И, выход которого является восьмым выходом блока, выходы первого, второго, третьего, четвертого элементов ИЛИ и вход элемента НЕ подключены к выходам блока, образующим его первый выход.

25

3.Устройство по п.1. о т л и - чающееся тем, что блок ввода содержит генератор импульсов, триггер, постоянное запоминающее устройство, счетчик, три элемента ИЖ, четыре элемента И, пять элементов за- 30 держки, два элемента И-НЕ, группу элементов И, три регистра, причем вход установки в О триггера соединен с входом пуска генератора импульсов и является входом блока, первым выходом которого являются выходы элементов И группы, первые входы которых соединены с соответствующими инфо1зма- ционными входами первого и второго регистров, с п входами первого эле35

мента И и подключены к п прямым вы-

ходам третьего регистра, вход которого соединен с выходом постоянного запоминающего устройства, вход считывания и адресный вход которого соединены соответственно с выходом первого элемента задержки и выходом счетчика, вход установки в О которого соединен с входом второго элемента задержки и с выходом третьего элемента задержки, вход которого соединен с первым входом первого элемента ИЛИ и является входом блока, первые входы второго и третьего элементов ИЛИ объединены и подключены к выходу генератора импульсов, вход останова которого соединен с входом установки в 1 триггера и с выходом первого элемента ИЛИ, второй вход которого соединен с выходом первого элемента

11

И, п входов первого элемента И-НЕ соединены с инверсными выходами третьего регистра, п прямых и n-m инверсных выходов которого соединены с соответствующими п входами второг элемента И-НЕ, ; (п+1)-й вход которго соединен с (п+1)-м входом первого элемента И-НЕ, с (п+1)-м входом первого элемента И, с (п+1)-м выходом третьего регистра и с первым входом второго элемента И, второй вход которого соединен с прямым выхдом триггера, вторые входы второго третьего элементов ИЛИ объединены и подключены к выходу третьего элемента И, первый вход которого соединен с вторыми входами элементов-И группы и с выходом четвертого элеме та задержки, вход которого соединен с третьим входом третьего элеме та ИЛИ и является входом блока, третий выход которого соединен с выходом первого регистра, вход записи которого соединен с первым входом четвертого элемента И, с выходом

2282.

0

15

5

J2

пятого элемента задержки, вход которого соединен с четвертым входом третьего элемента ИЛИ и является входом блока, счетный вход счетчика соединен с выходом третьего элемента ИЛИ, пятый вход которого обьединен с третьим входом второго элемента РШИ и подключен к выходу четвертого элемента И, второй вход которого соединен с выходом первого элемента И-НЕ, вход записи второго регистра соединен с выходом второго элемента задержки, с шестым входом третьего элемента ИЛИ и с четвертым входом второго элемента ИЛИ, пятый вход которого является входом устройства, выход второго элемента ИЛИ соединен с входом первого элемента задержки, выход второго элемента ШШ-НЕ соединен с вторым входом третьего элемента И, п выходов второго регистра, п прямых выходов третьего регистра и выход второго элемента И соединень с выходами блока, образующими его второй выход.

стЛ

KSff.6

д-Лг/

к1л2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1149779A1 |

| Устройство для поиска дефектов цифровых блоков | 1987 |

|

SU1520519A1 |

| Устройство для поиска дефектов логических блоков | 1984 |

|

SU1221654A1 |

| Устройство для контроля и диагностики дискретных блоков | 1985 |

|

SU1254488A1 |

| Устройство для диагностирования дискретных блоков | 1986 |

|

SU1520516A1 |

| Устройство для диагностирования дискретных узлов | 1988 |

|

SU1681305A1 |

| Устройство для поиска дефектов дискретных блоков | 1985 |

|

SU1379784A1 |

| Устройство для контроля программно-аппаратных средств эвм | 1987 |

|

SU1513454A1 |

| Устройство для диагностирования цифровых узлов | 1986 |

|

SU1520517A1 |

| Устройство для диагностирования группы логических узлов | 1987 |

|

SU1520520A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в устройствах контроля работоспособности и диагностирования цифровых узлов и блоков. Цель изобретения - повышение достоверности контроля. Устройство содержит блок 1 ввода, блок 2 памяти. коммутатор 3, блок 4 сравнения, блок 5 индикации, блок 6 управления, триггер 7, элементы И 8 и 9. Для осуществления процесса диагностирования используется тест поиска дефектов- из идентификаторов. В каждом идентификаторе выбирается один тестовый набор, обладающий наибольшей обнаруживающей способностью, который ставится в идентификаторе на первое место. Множество этих наборов образует проверяющий тест, который совместно с тестом поиска дефектов осуществляет контроль и диагностику цифрового узла. Повьш1ение достоверности контроля достигается за счет введения триггера и двух элементов И, позволяющих использовать проверяющий тест. 2 з.п. ф-лы, 4 ил. с (О (Л со о ГС ГчЭ оо го N) (Риг.1

Редактор А.Шандор

Составитель И.Иванкин

Техред Л.ОлейникКорректор А.Ильин

Заказ 1.217/48. Тираж 673Подписное

ВНИИГЕИ .Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

аил

fpuz.

| Устройство для поиска дефектов цифровых узлов | 1980 |

|

SU962957A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-04-07—Публикация

1985-10-05—Подача