У

ОО 00

lu

00 CD

1138

Изобретение относится к вычислительной технике и может быть исполь- зонано для сложения и вычитания чисел в избыточной минимальной системе счисления.

Цель изобретения - расширение функциональных вoзмoжнocteй устройства за счет организации вычитания, а также повышение быстродействия уст- ройства.

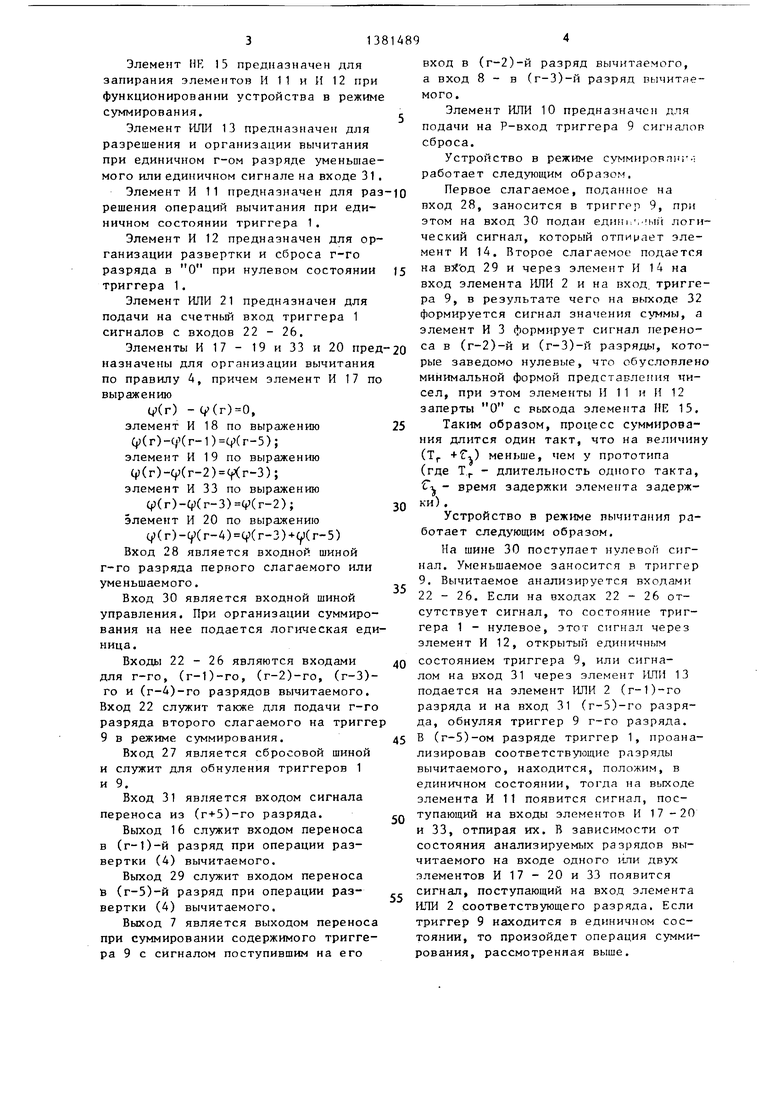

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство содержит счетный триггер 1, элемент ИЛИ 2, элемент И 3, вход 4 переноса из (г+5)-го разряда, вход 5 переноса из ()-го разряда, вход 6 переноса из (г+5)-го разряда выходы 7 и 8 переносов в (г-2)-й и (г-З)-й разряды, RS-триггер 9, эле- мент ИПИ 10, элементы И 11 и 12, элемент ИЛИ 13, элемент И 14, элемент НЕ 15 Быход 16 переноса в (г-1)-й разряд, элементы И 17 - 20, элемент ИЛИ 21, вход 22 первого операнда, входы 23 - 26 из (г-1)-го, (г-2)-го, (г-З)-го и (г-4)-го разрядов устройства, вход 27 сброса, вход 28 второг операнда, выход 29 (г-5)-го разряда, вход 30 управления сложением-вычита- нием, вход 31 из (г-5)-го разряда, выход 32 результата, элемент И 33 и выходы ЗА - 38 вычитания.

натуральное числа А в двоичной минимальной системе счисления мо жет быть записано в виде

, с(г), (1)

Г 1

где a,,l

О при г О, .1 при Oir i 1, (2) V(r-2)+(t (r-3) при г 1

Значение ц(п-И) определяют мощность п-разрядных минимальных кодов

Особенностью изображений в минимальной форме является наличие в общем случае между двумя ближайшими логическими единицами не менее четырех нулей,

Из выражения (2) можно вывести следующие правила вычитания: )-(j.4r)0; (+ (r)-v(r-1)V(r-5); i|Xr)-(r-2)V(r-3); 9(г)-()(г-3) (у(г-4);

C(r)-i(r-4) v(r-3) + V(r-5). (3) 1

Исходя из выражения (3), представим алгоритм вычитания.

JQ

5 0 5 0

5

С

5

0

5

1.Анализируется состояние г-го, (г-1)-го, (г-2)-го, (г-З)-го и (г-4)- го разрядов вычитаемого при условии, что разряд уменьшаемого содержит логическую единицу, если в г-ом (г-1)- ом, (г-2)-ом, (г-4)-ом, (г-4)-ом разрядах вычитаемого имеется разряд, содержащий логическую единицу, то производим вычитание по правилам (3) (следует заметить, что в анализируемых разрядах возможно наличие лишь одной логической единицы, что определяется формой представления изображений в двоичной минимальной системе счисления). Происходит сброс в О триггера г-го разряда и установка в 1 триггера (триггеров) в соответствии с правилом.

2.Если анализ г-го, (г-1)-го, (г-2)-го, (г-З)-го и (г-4)-го разрядов вычитаемого выявил отсутствие единичного разряда, то г-й разряд уменьшаемого развертывается по правилу

ф(г)((г-1)+(г-5), (4)

I

причем тригге р (г-1)-го разряда установится сразу в единичное состояние, а в (г-5)-ом разряде с учетом состояния (г-5)-го, (г-б)-го, (г- 7)- го и (г-8)-го разрядов вычитаемого производится либо вычитание в соответствии с пунктом 1, либо развертка н соответствии с пунктом 2.

Сущность предлагаемого изобретения заключается в реализации данного алгоритма и применении для суммирования RS-триггера.

Триггер 1 предназначен для анализа и хранения результата анализа г-го, (г-1)-го, (г-2)-го, (г-З)-го и (г-4)-го разрядов вычитаемого.

Триггер 9 предназначен для организации процесса сложения и вычитания .

Элемент ИЛИ 2 предназначен для выборки поступающих на S-вход триггера 9 сигналов.

Элемент И 3 предназначен для формирования сигнала переноса из г-го разряда в (г-2)-й и (г-З)-й разряды уменьшаемого или одного из слагаемых (в зависимости от режимов работ).

Элемент И 14 предназначен для подключения г-го разряда второго слагаемого при суммировании на вход элемента ИЛИ 2.

Элемент НЕ 15 предназначен для запирания элементов И 11 и И 12 при функционировании устройства в режиме суммирования.,

Элемент ИЛИ 13 предназначен для разрешения и организации вычитания при единичном г-ом разряде уменьшаемого или единичном сигнале на входе 31,

Элемент И 11 предназначен для раз-ю решения операций вычитания при единичном состоянии триггера 1 .

Элемент И 12 предназначен для организации развертки и сброса г-го разряда в О при нулевом состоянии 15 триггера 1.

Элемент ИЛИ 21 предназначен для подачи на счетный вход триггера 1 сигналов с входов 22 - 26.

вход в (г-2)-й разряд вычитаемого, а вход 8 - в (г-З)-й разряд вычитаемого.

Элемент ИЛИ 10 предназначен для подачи на Р-вход триггера 9 сигналов сброса.

Устройство в режиме суммировшч .; работает следующим образом.

Первое слагаемое, поданное на вход 28, заносится в триггер 9, при этом на вход 30 подан едини ,. ый логический сигнал, который отпирает элемент И 14. Второе слагаемое подается на вй од 29 и через элемент И 14 на вход элемента ИЛИ 2 и на вход, триггера 9, в результате чего на выходе 32 формируется сигнал значения суммы, а элемент И 3 формирует сигнал переноЭлементы И 17 - 19 и 33 и 20 пред-20 (г-2)-й и (г-З)-й разряды, котоназначены для организации вычитания по правилу 4, причем элемент И 17 п выражению

()(г) - д(г)0,

элемент И 18 по выражению С(г)-(.Чг-1)ф(г-5);

элемент И 19 по выражению ф(г)-(г-2) (Х;г-3);

элемент И 33 по выражению ф(г)-ф(г-3)ф(г-2);

элемент И 20 по выражению ((r)-y(r-4)q)(r-3)-t-((r-5)

Вход 28 является входной шиной г-го разряда первого слагаемого или уменьшаемого.

Вход 30 является входной шиной управления. При организации суммирования на нее подается логическая единица .

Входы 22-26 являются входами для г-го, (г-1)-го, (г-2)-го, (г-3)- го и (г-4)-го разрядов вычитаемого. Вход 22 служит также для подачи г-го разряда второго слагаемого на тригге 9 в режиме суммирования.

Вход 27 является сбросовой шиной и служит для обнуления триггеров 1 и 9.

Вход 31 является входом сигнала переноса из (г+5)-го разряда.

Выход 16 служит входом переноса в (г-1)-й разряд при операции развертки (4) вычитаемого.

Выход 29 служит входом переноса В (г-5)-й разряд при операции развертки (4) вычитаемого.

Выход 7 является выходом переноса при суммировании содержимого триггера 9 с сигналом поступившим на его

вход в (г-2)-й разряд вычитаемого, а вход 8 - в (г-З)-й разряд вычитаемого.

Элемент ИЛИ 10 предназначен для подачи на Р-вход триггера 9 сигналов сброса.

Устройство в режиме суммировшч .; работает следующим образом.

Первое слагаемое, поданное на вход 28, заносится в триггер 9, при этом на вход 30 подан едини ,. ый логический сигнал, который отпирает элемент И 14. Второе слагаемое подается на вй од 29 и через элемент И 14 на вход элемента ИЛИ 2 и на вход, триггера 9, в результате чего на выходе 32 формируется сигнал значения суммы, а элемент И 3 формирует сигнал перено5

0

5

0

5

0

5

рые заведомо нулевые, что обусловлено минимальной формой представления чисел, при этом элементы И 11 и И 12 заперты О с выхода элемента НЕ 15.

Таким образом, процесс суммирования длится один такт, что на ве1П1чину (Т ) меньше, чем у прототипа (где Т, - длительность одного такта, Г - время задержки элемента задержки) .

Устройство в режиме вычитания работает следующим образом.

На шине 30 поступает нулевой сигнал. Уменьшаемое заносится в триггер 9, Вычитаемое анализируется входами 22 - 26. Если на входах 22 - 26 отсутствует сигнал, то состояние триггера 1 - нулевое, этот сигнал через элемент И 12, открытый единичным состоянием триггера 9, или сигналом на вход 31 через элемент Ш1И 13 подается на элемент ИЛИ 2 (г-1)-го разряда и на вход 31 (г-5)-го разряда, обнуляя триггер 9 г-го разряда. В (г-5)-ом разряде триггер 1, проанализировав соответствующие разряды вычитаемого, находится, положим, в единичном состоянии, тогда на выходе элемента И 11 появится сигнал, поступающий на входы элементов И 17 -20 и 33, отпирая их. В зависимости от состояния анализируемых разрядов вычитаемого на входе одного и.пи двух элементов И 17 - 20 и 33 появится сигнал, поступающий на вход элемента ИЛИ 2 соответствующего разряда. Если триггер 9 находится в единичном состоянии, то произойдет операция суммирования, рассмотренная выше.

Таким образом, если вычитаемое и уменьшаемое подаются одновременно, то весь процесс вычитания длится два такта. Формула изобретения

Устройство для сложения и вычитания чисел в избыточной минимальной системе счисления, содержащее в каж- дом разряде счетный триггер, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, первый, второй, третий, четвертый элементы ИЛИ, причем вход сброса устройства соединен с входом сброса счетного триггера, вход первого операнда устройства подключен к первому входу первого элемента ИЛИ второму, третьему, четвертому входам которого подключены соответственно с входами переноса из ()-го, (г+3) го, (г-|-5)-го разрядов устройства, к выходу первого элемента ИЛИ подключен первый вход первого элемента И, вы- ход которого соединен с выходом переноса в (г-2)-й и (г-З)-й разряды устройства, отличающееся тем, что, с целью расщирения функциональных возможностей за счет органи- зации операции вычитания и повышения быстродействия, в него дополнительно введены RS-триггер и элемент НЕ, причем прямой выход RS-триггера соединен информационным выходом устройства с вторым входом первого элемента И и первым входом второго элемента ИЛИ, второй вход которого подключен к входу переноса из (г+5)-го разряда устройства, выход второго элемента ИЛИ соединен с первыми входами третьего и второго - элементов И, второй вход второго элемента И подключен к прямому выходу счетного триггера, второй вход третьего элемента И подключен

к инверсному выходу счетного триггера, выход второго элемента И подклюг 0 5 о «

5

5

чен к первым входам пятого, шестого, седьмого, 1етввртого и девятого элементов И, выход третьего элемента И соединен с входом первого элемента ИЛИ (г-1)-го разряда, входом второго элемента ИЛИ (г-5)-го разряда и первым входом третьего элемента ИЛИ г-го разряда, выход первого элемента ИЛИ соединен с S-входом триггера, выход третьего элемента ИЛИ - с R-входом триггера, второй вход третьего элемента ИЛИ подключен к входу сброса устройства, первый вход восьмого элемента И подключен к входу управления сложением-вычитанием, второй вход восьмого элемента И является входом второго операнда устройства, выход восьмого элемента И соединен с пятым входом первого элемента ИЛИ, выход четвертого элемента ИЛИ подключен к счетному входу счетного триггера со счетным входом, первый вход которого является входом вычитаемого г-го разряда, второй - входом (г-1)-го разряда, третий - ()-го разряда, четвертый - (г-З)-го разряда, пятый (г-4)-го разряда, вход четвертого элемента И соединен с входом вычитаемого (г)-го разряда, пятого элемента И - с входом (г-1)-го разряда, шестого и седьмого элементов И - с входами (г-2)-го, (г-З)-го разрядов, девятого элемента И - с входом (г-4)-го разряда, выходы пятого, шестого, девятого элементов И подключены к соответствующим входам первых элементов ИЛИ соответственно (г-5)-го, (г-3)- го, (г-2)-го разрядов, выход девятого элемента И соединен с входами первых элементов ИЛИ (г-З)-го, (г-5)-го разрядов, выход четвертого элемента И соединен с третьим входом третьего элемента ИЛИ, вход элемента НЕ подключен к входу управления сложением- вычитанием, а выход - к третьим входам второго и третьего элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Накапливающий сумматор | 1991 |

|

SU1800454A1 |

| Накапливающий сумматор | 1980 |

|

SU920706A2 |

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для контроля последовательного сумматора-вычитателя | 1981 |

|

SU968818A1 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Устройство для сложения длительностей импульсов | 1987 |

|

SU1548796A1 |

| ДВОИЧНО-ДЕСЯТИЧНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР | 1971 |

|

SU293241A1 |

Изобретение относится к области вычислительной техники и может быть использовано для сложения и вычитания чисел в избыточной минимальной системе счисления. Цель изобретения - расширение функциональных возможностей, за счет организации операции вычитания, повышение быстродействия. Устройство содержит в каждом i-м разряде триггер со счетным входом 1, RS-триг- гер 9, четыре элемента ИЛИ 2,10,13, 21, девять элементов И 3,11,12,14,17, 18,19,33, элемент НЕ 15, входные шины 28,22,23,24,25,26, шину сброса 27, шину управления 30, информационный выход 32, входы переносов 4,5,6,31, выходы переносов 7,8,.выходы вычитания 34,35,36,37,38. Работа устройства основана на алгоритме прямого вычитания. Предлагаемое устройство может быть использовано для построения универсальных арифметических усройств, обладающих высоким быстродействием и помехоустойчивостью. 1 ил. (Л

| Голышев Л.К | |||

| Электронные цифровые вычислительные машины | |||

| Киев: Техника, 1965, с.201 | |||

| Накапливающий сумматор | 1985 |

|

SU1278835A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-15—Публикация

1986-08-19—Подача