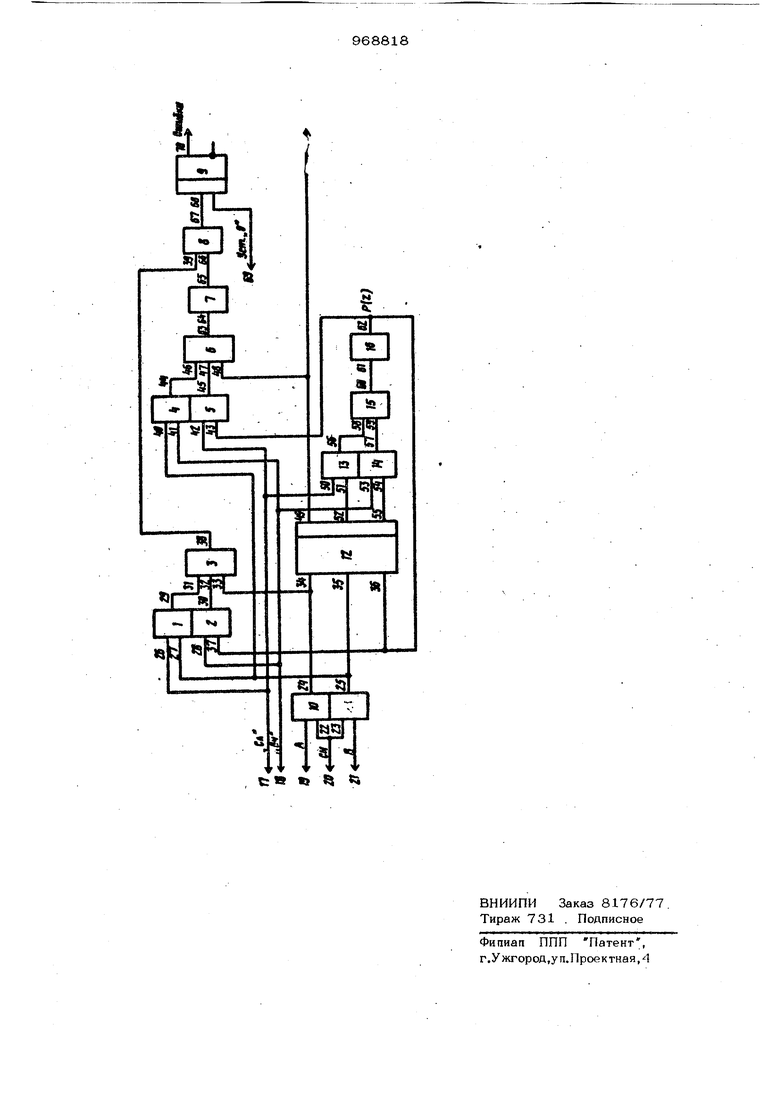

входами первого, второго и третьего элементов И, вход управления вычитанием соединен с первыми входами четвертого пятого и шестого элементов И, входы первого и второго операндов устройства соединены с первыми входами соответственно седьмого и восьмого элементов И, вход синхронизации устройства соединен с вторыми входами седьмого и восьмого элементов И, выход седьмого элемента И соединен с входом первого операнда одноразрядного сумматора, выход вось- . мого элемента И соединен с входом второ го операнда одноразрядного сумматора, с вторыми входами первого и пятого элементов И(. выход суммьг, переноса и заем одноразрядного сумматсфа соединен соответственна с выходом результата устрбй ства, с вторыми входами третьего и шеетого элементов И, выходы которых соединень с первым и вторым входакш первбго элемента ИЛИ, выход первого элема1та ИЛИ через элемент задержки соединен с вторыми входами второго и четвфтого элементов И и с входом переноса однораз рядного сумматора, введены первый и второй сумматоры по модулю два и триггер со счет1вым входом, причем выходы Первого, четвертого к седьмого элементов И соединены соответственно с первым, и третьим входами первого сумма тора по модулю два, выход которого соединен с первым входом второго элемента ИЛИ, выходы второго и пятого элементов И и выход суммы одноразрядного сумматора соединены соответственно с первьгм, вторым и третьим входами второго сумматора по модулю два, выход которого через второй элемент задержки соединен с вторым входом второго элемента ИЛИ, . выход второго, элемента ИЛИ соединен со счетным входом триггера, единичный выход которого является контрольным выходом устройства, установочный вход устройства соединен с нулевым входом триг гера. На чертеже приведена функциональная схема устройства, для контроля последовательного сумматора-вычитателя. Устройство содержит элементы И 1 и 2, сумматор 3 по модулю два, элементы И 4 и 5, сумматор 6 по модулю два, элемент 7 задержки, элемент ИЛИ 8, триггер 9, элементы И 1О и 11, которьге подключены к входам и-выходам контролируемого сумматора-вычитателя, в состав которого входят собственно одноразрядный сумматор 12 и цепи обратной связи для элементы И 13 и 14, эпеменг ИЛИ 15 и элемент 16 задержки. Входы 17 и 18 1галяются входами устройства и по ним в устройство поступают соответственно признаки операций сложения и вычитания. Повходу 19 в устройство поступает код первого слагаемого (уменьшаемого) А, по входу 2О - синхронизирующие импульсы (СИ), по вхО(Ду 21 - код второго слагаемого (и 1чнтаемого) В. Вход 22 элемента И 10 и вход 2.3 элемента И 11 соединешл с входом 2О устройства. С выхода 24 элемента И 10 снимается код первого слагаемого (уменьшаемого), а с выхода 25 элемента И 11 - код второго слагаемого (вычитаемого). Входы 26 и 27 элемента.И 1 соединены соответственнос входом 17 устройства и выходом 25 элемента И 11. Вход 28 элемента И 2 соединен с входом 18 устройства. Выход. 29 элемента И 1 и вход 30 элемента И 2 соединены соответственно с входами 31 и 32 сумматор 3 по модулю два, а вход 33 последнего соединен с входом 34 сумматора-вычитателя. 12 и выходом 24 элемента И 1О. Входы 35 и 36 сумматора-вычитателя 12 соединены соответственно с выходом 25 эле- мента И 11 и. с входом 37 элемента И 2, Выход 38 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 3 соединен с входом 3 9 элемента ИЛИ 8. Входы 40 и 41 элемента И 4 соответственно соединены с выходом 25 элемента И 11 и входом устройства 18. Входы 42 и 43 элемента И 5 соединены соответственно с входом 17 устройства и с входом 36 одноразрядного сумматора 12. Выходы 44 и 45 элементов И 4 и 5 соответственно соединены с входами 46 и 47 сумматора 6, вход 48 которого соединен с выходом 49 одноразрядного сумматора. Входы 50 и 5 Г элемента И 13 соединены с входом 17 устройства и выходом 52 сумматора-вычитателя 12 соответственно. Входы 53 и 54 элемента И 14 соединены с входом 18 устройства и: выход ом 55 сумматора-вычитателя 12 соответственно. Выходы 56 и 57 элементов И 13 и 14 соответственно соединены с входами 58 и 59 элемента И 15, выход 6О которого соединен с входом 61 элемента 16 задержки, который своим выходом 62 соединен с входом 36 сумматора-вычитателя 12 и с входом 43 элемента И 5. Выход 63 сумматора 6 соединен с входом 64 элемента 7 задержки, выход 65 которого соединен с входом 66 элемента ИЛИ 8, выход 67 596 которого соединен с входом 68 триггера 9, на вход 69 которого подается сигнал установки в ноль. Сигнал ошибки снимается с выхода 7О триггера 9. Общий принцип работы устройства контропя последовательного сумматора-вычитателя основан на том, что по завершении операции сложения суммарное количество единиц суммы и возникающих при сложении единиц переноса, а также суммарное количество едтшиц в кодах спагаемых допжно быть одинаковым. Переходя к наименьшим вычетам по модулю два, это свойство можно описать математической зависимостью ., (1) где 1 А , Г з , г. и Гр - соответственно суммы по модулю два единиц кодов слагаемых А и В, суммы С и единиц переноса Р; @ - символ операции сложения по модулю два. При выполнении операции вычитания одинаковыми должны быть суммарное количество единиц кода уменьшаемого и единиц займа с одной стороны, и суммарное количество единиц кодов вычитаемого и разности с другой стороны. Это свойство описывается следующей математической зависимостью: . Г -Г I где I с 2. сУ п° модулю два соответственно единиц кода уменьшаемого, Вычитаемого, разности и займа. Устройство контроля сумматора-вычитателя работает следующим образом. -, При выполнении операции сложения слагаемые А и В по входам 19 и 21 элементов И 1О и 11 соответственно, синхронизируемые синхронизирующими импульсами, подаваемыми на входы 22 vi 23 элементов И 10 и 11, с выходов 24 к 25 соответственно этих элементов подаются на .входы 34 и 35 одноразрядного сумматора. Одновременно слагаемое А с выхода 24 элемента И 10 поступает на вход 33 сумматора 3. Слагаемое В с выхода 25 элемента И 11 поступает на вход 27 элемента И 1, на второй вход 26 которого подается признак сложения, поступающий в схему устройства контроля по входу 17. В режиме сложения признак вычитания Вч.Свход 18 устройства контроля) раве1 логическому нулю, и поэтому на выходе 30 элемента И 2 всегда будет логический ноль. Слагаемое В с выхода 29 элемента 18i И 1 подается на вход 31 сумматора 3. На выходе 38 сумматора 3 формируется сумма по модулю два очередных разрядов слагаемых, которая поступает на вход 39 элемента Р1ЛИ 8 и с его выхода 67 на вход 68 триггера 9. Перед началом операции триггер 9 устанавливается в нулевое состояние по входу 69 сигналом Начальная установка, Если сигнал суммы по модулю два очередных разрядов слагаемых равен логической единице, то триггер 9 устанавливается в единичное состояние. Разряды суммы с выхода 49 сумматора-вычитателй пост тпают на вход 48 сумматора 6. Единицы переноса с выхода 52 одноразрядного сумматора 12 подаются на вход 51 элемента И 13, на второй вход 5О которого поступает признак сложения, и с выхода 56 этого элемента поступают на вход 58 элемента ИЛИ 15, а с его выхода 60 - на вход 61 элемента 16 задержки. С выхода 62 этого элемента едшппи 1 переноса подаются на вход 43 элемента И 5, на второй вход 42 которого поступает признак сложения. С выхода 45 элемента И 15 сигналы единиц переноса поступают на вход 47 сумматора 6, в результате чего на выходе 63 этого элемента формируется сумма по модулю два очередного разряда суммы и единицы переноса. Эта сумма с иыхода 63 сумматора 6 подается на вход 64элемента 7 задержки, с его выхода 65подается на вход 66 элемента ИЛИ 8, а с выхода 67 последнего поступает на счетный вх)д 68 триггера 9. Если сигнал на выходе 67 элемента 8 равен логической единице, то триггер 9 переI водится в противоположное состояние. Таким образом, если сумма по модулю ;два кодов слагаемых равна сумме по модулю два кода суммы и единиц переноса, то триггер 9 к концу операции находится в нулевом состоянии. В противном случае триггер 9 окажется в единичном состоянии и на единичном выходе 7О триггера сформируется сигнал ошибки. Таким образом, сумматор 3 совместно с триггером 9 реализует левую часть соотношения (1), сумматор 6 совместно с триггерса 4 9 - правую часть соотношения (l), а триггер 9, кроме того, осуществляет сравнение левой и правой частей соотношения (1). При вьшолнешга соотноше- ; ния (1) триггер 9 всегда после окончания всей операции должен находиться в нулевом состоянии, что свидетельствует об отсутствии ошибок при сложении.

Работа устройства контрапя последовательного сумматора-вычитателя при выполнении операции вычитания аналогична работе при выполнении сятерации сложения, отличаясь следующими особенности ми

Уменьшаемое А по цепи вход 19 элемента И 10 - выход 24 этого элемента поступает на вход 34 сумматора-вычитатля и на вход 33 сумматора 3. Сигнал займа Z. , формируемый на выходе 55 сумматора-вычитателя, поступает на вход 54 элемента И 14. На второй вх)д 53 этого элемента подается признак вычитания, поступ аюший в устройство по входу 18. С выхода 57 элемента И 14 сигналы займа подаются на вход 59 элемента ИЛИ 15, с выхода 60 этого элеманта на вход 61 элемента 16 задержки, а с выхода 62 элемента задержки на вход

37элемента И 2 поступает признак вычитания. С выхода 30 элементу И 2 сигналы займа подаются на вход 32 сумматора 3, в результате чего на выходе

38этого элемента формируется сумма по модулю два очередных разрядов уменьшаемого и займа. Эта сумма поступает

на вход 68 триггера 9 по цепи вход 39 и выход 67 элемента ИЛИ 8 - выход тригера 9. Вычитаемое В по цепи вход 21 и выход 25 элемента И 11 - вход 44 элемента И 4 поступает на вход 46 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 6. На вход 48 этого же элемента с выхода 49 сумматора-вычитателя поступает разность С.

Так как в режиме вычитания признак сложения равен логическому нулю, то всегда на выходе 45 элемента И 5 будет логический ноль, и поэтому на выходе 63 сумматора 6 формируется сумма по модулю два разрядов кода разности и вычитаемого, которая по цепи . вход 64 и выход 65 элемента задержки 7 - вход 66 и выход 67 элемента ИЛИ 8 поступает на счетный вход 68 триггера 9, Таким образом, сумматор 3 совместно с триггером 9 реализует левую часть соотнесения (2). а сумматор 6 совместно с триггером 9 - правую часть соотношения (2), а триггер 9 вьшолняет также сравнение левой и правой частей соотношения (2). Единичное состояние триггера 9 свидетельствует об ошибке.

Предлагаемое устройство для контроля последовательного сумматора-вычитателя значительно проще известного, содержашего два разрядных счетчика, т.е. 2К триггеров и одну К-разрядную схему сравнения (на 2К входов) кодов счетчиков.

так как имеет один триггер и два сумматора по модулю два на три входа каждый. Например, при и 16, выигрыш в объеме оборудования будет не менее чем в 8 раз.

Формула изобретения Устройство для контроля последовательного сумматора-вычитателя, содержащее первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элементы И, одноразрядный сумматор, первый и второй элементы ИЛИ, первый и второй элементы задержки, причем вход управления сложением соединен с первым входами первого, второго и третьего элементов И, вход управления вы.чнтанием соединен с первыми входами четвертого, пятого и шестого элементов И, входы первого и второго операндов устройства -соединены с первыми входами соответственно седьмого и восьмого элементов И, вход синхронизашга устройства соединен с вторыми входами седьмого и восьмого элементов И, выход седьмого элемента И соединен с входом первого операнда одноразрядного сумматора, выход восьмого элемента И соединен с входом второго операнда одноразрядного сумматора, с вторыми входами первого и пятого элементов И, выход суммы, переноса и заема одноразрядного сумматора соединены соответственно с выходом результата устройства, с вторыми входами третьего и шестого элементов И, выходы которых соединены с первым и .вторым входами первого элемента ИЛИ, выход первого элемента ИЛИ через элемент задержки соединен с вторыми входами второго и четвертого элементов И и с входом переноса одноразрядного сумматора, отличающееся тем, fro, с целью улрсацения устройства, в него введены первый и. второй сумматоры по модулю два и триггер со счетным входом, причем выходы первого, четвертого и седьмого элементов И соединены соответственно с первым, вторым и третьим входами первого сумматора по модулю два, выход которого соединен с первым входом второго элемента ИЛИ, выходы второго и пятого элементов И и выход суммы одноразрядного сумматора соединены соответственно с первым, вторым и третьим входами второго сумматора по модулю два, выход которого через элемент задержки соединен с вторым входом второго элемента ИЛИ, выход второго эле-

96881810

мента ИЛИ соединен со счетным входом1. Авторское свидетельство СССР

триггера единичный выход которого являет Ni 603990, кл. G06F 11/00, 1973. ся контрольным выходом устройства, уста-2. Авторское свидетельство СССР

новочный вход устройства соединен с№ 739535, кл. G06 F 11/ОО, 1980. нулевым входом триггера. 5 3. Авторское свидетельство СССР

Источники информации,по заявке М 2949649/18-24, 1980

принятые во внимание при экспертизе(прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для контроля сумматора-вычитателя последовательного действия | 1980 |

|

SU926661A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ, ВЫЧИТАНИЯ И УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛЮ | 2019 |

|

RU2711051C1 |

| Устройство для обнаружения ошибок | 1972 |

|

SU502859A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

Авторы

Даты

1982-10-23—Публикация

1981-05-11—Подача