Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах,

Целью изобретения является повышение быстродействия.

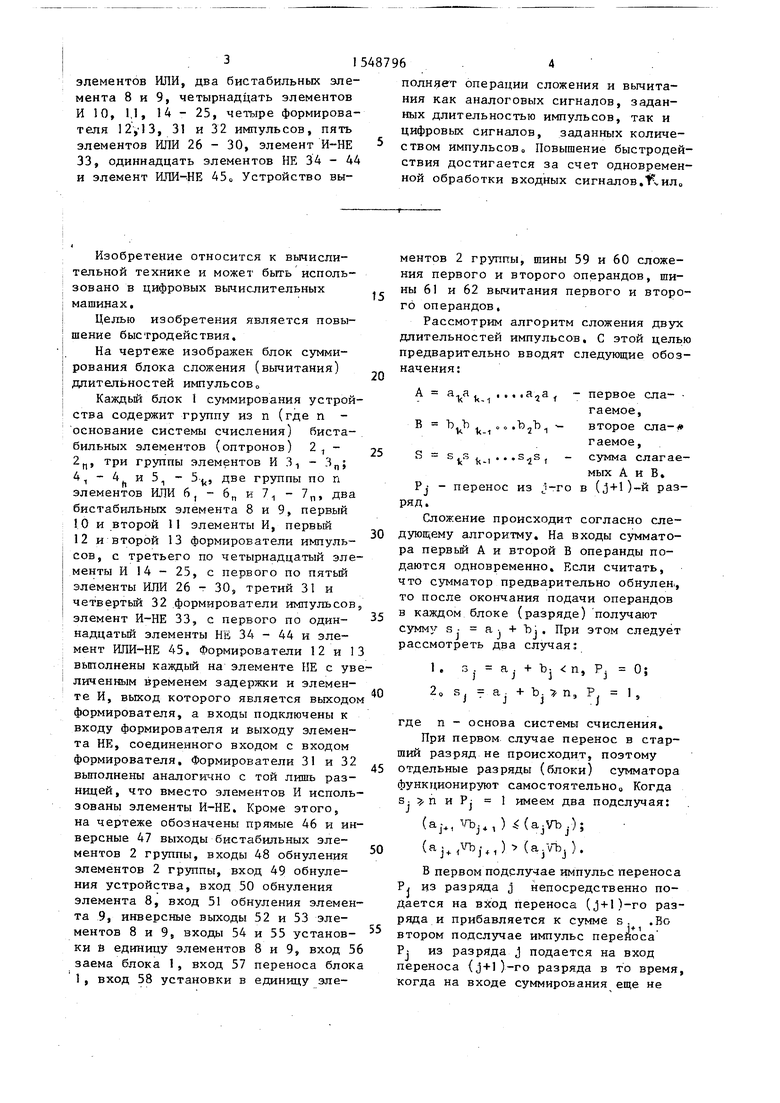

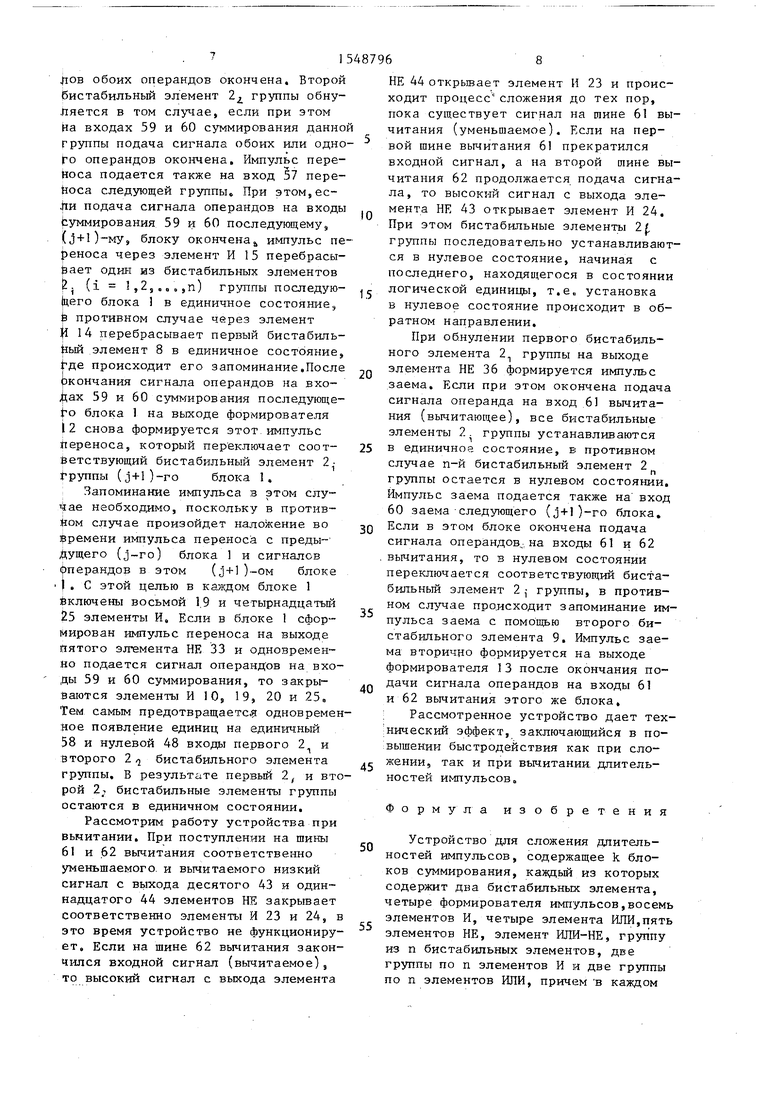

На чертеже изображен блок суммирования блока сложения (вычитания) длительностей импульсов

Каждый блок 1 суммирования устройства содержит группу из п (где п - основание системы счисления) бистабильных элементов (оптронов) 21 п

три группы элементов И 31 - Зп;

41-4и51 5, две группы по п элементов ИЛИ 6,-6пи71 7П, два бистабильных элемента 8 и 9, первый 10 и второй 11 элементы И, первый 12 и второй 13 формирователи импульсов, с третьего по четырнадцатый элементы И 14 - 25, с первого по пятый элементы ИЛИ 26 - 30, третий 31 и четвертый 32 формирователи импульсов, элемент И-НЕ 33, с первого по одиннадцатый элементы На 34 - 44 и элемент ИЛИ-НЕ 45. Формирователи 12 и 13 выполнены каждый на элементе НЕ с увеличенным временем задержки и элементе И, выход которого является выходом формирователя, а входы подключены к входу формирователя и выходу элемента НЕ, соединенного входом с входом формирователя. Формирователи 31 и 32 выполнены аналогично с той лишь разницей, что вместо элементов И использованы элементы И-НЕ. Кроме этого, на чертеже обозначены прямые 46 и инверсные 47 выходы бистабильных элементов 2 группы, входы 48 обнуления элементов 2 группы, вход 49 обнуления устройства, вход 50 обнуления элемента 8, вход 51 обнуления элемента 9, инверсные выходы 52 и 53 элементов 8 и 9, входы 54 и 55 установки в единицу элементов 8 и 9, вход 56 заема блока 1, вход 57 переноса блока 1, вход 58 установки в единицу эле

ментов 2 группы, шины 59 и 60 сложения первого и второго операндов, шины 61 и 62 вычитания первого и второго операндов.

Рассмотрим алгоритм сложения двух длительностей импульсов, С этой целью предварительно вводят следующие обозначения:

А а,а .

V fc-i

,,.,aaat - первое слагаемое,

5

0

5

0

5

В Ъ.Ъ .

V.

,Ъ2Ъ1 S S 1cS fc-1 S1S I

второе ела- гаемое,

- сумма слагаемых А и В. Р.- - перенос из j-ro в (j + O-й раз- ряд.

Сложение происходит согласно следующему алгоритму. На входы сумматора первьй А и второй В операнды подаются одновременно. Если считать, что сумматор предварительно обнулен, то после окончания подачи операндов в каждом блоке (разряде) получают сумму s а . + Ъ . При этом следует рассмотреть два случая;

1. з } + Ъ n, PJ 0; 2„ Sj а.} + Ь n, Р, 1 ,

где п - основа системы счисления.

При первом случае перенос в старший разряд не происходит, поэтому отдельные разряды (блоки) сумматора функционируют самостоятельно0 Когда s- п и Р: 1 имеем два подслучая:

J

( Vbj41) (а3УЪр;

() (ajVbj).

В первом подслу-iae импульс переноса Р, из разряда j непосредственно подается на вход переноса (j+l)-ro разряда и прибавляется к сумме s. .Во втором подслучае импульс переноса Р: из разряда J подается на вход переноса {j+1)-го разряда в то время, когда на входе суммирования еще не

окончена подача разрядов а:+1 и bjr1 операндов. При этом, чтобы исключить наложение сигналов операндов а,м и Ъ 1 и переноса Р , происходит запоминание переноса PJ на промежуточ- - ных элементах памяти и выдается на вход переноса разряда (j + 0-й после окончания сигналов а.- + , и bj+1 0

Устройство работает следующим образ ом о

Устройство оперирует как с аналоговым сигналами (заданными длительностью импульсов), так и с цифровыми сигналами (заданными количеством импульсов).

Рассмотрим функционирование устройства с аналоговыми сигналами. До начала процесса суммирования высокий потенциал подается на шину 49 обнуления и, пройдя через элементы ИЛИ 61 - 6„ первой группы и первый 26 и второй 27 элементы ИЛИ группу би- стабильных элементов 2 t - 2 п и би- стабильные элементы 8 и 9 всех групп переводит в нулевое состояние.

При поступлении информации (единичных сигналов) на шины 59 и 60 сложения j-ro блока I низкий потенциал с выхода элемента И-НЕ 33 поступает на входы восьмого 19 и четырнадцатого 25 элементов И и закрывает их. Одновременно этот сигнал,пройдя седьмой элемент НЕ 40, открывает элемент И 20 (при этом на вход элемента И 20 с выхода формирователя 32 подается высокий потенциал). Высокий сигнал с выхода элемента И 20 через первьй 71 и второй 1 элементы ИЛИ второй группы переключают первый 21 и второй 25 бистабильные элементы группы в единичное состояние, и на выходах 46 этих элементов появляется высокий потенциал. Высокий потенциал с выхода 46 второго бистабиль- ного элемента 22 группы через первьй элемент И 5, (которой в это время в открытом состоянии) третьей группы и через третий 73 и четвертый 7, элементы ИЛИ второй группы подается на единичные входы 58 третьего 2j и четвертого 24 биста- бильных элементов группы, которые переключает в единичное состояние и т.д. Если на шины 59 и 60 сложения в этот момент прекращается подача одного из входных сигналов, то элемент И-НЕ 33 закрывается, низкий

0

5

сигнал, пройдя через восьмой, элемент НЕ 41 или девятый элемент НЕ 42,, открывает соответственно или элемент И 22, или элемент И 21.

Высокий сигнал с выхода элемента И 22 или элемента И 21, пройдя элемент ИЛИ 28, открывает первый элемент И 10 (при этом на первый вход элемента И 10 с выхода формирователя 32 подается высокий потенциал)а Одновременно этот сигнал, пройдя шестой элемент НЕ 39, закрывает элемент И 19. Высокий сигнал с выхода первого элемента И 10, пройдя через четвертый элемент И 34 первой группы и через пятый элемент ИЛИ 7 второй группы, переключает пятый бистабиль- ный элемент 25 группы в единичное

0 состояние. Следовательно, на выходе 46 этого элемента появляется высокий потенциал. Высокий потенциал с выхода 46 пятого бистабильного элемента 2f группы через пятьй элемент И 3

5 (который в это время в открытом состоянии) первой группы и через шестой элемент ИЛИ 7, второй группы подается на единичный вход 58 шестого бистабильного элемента 2t групQ пы, которьй переключает в единичное состояние и т.д.

Переход в единичное состояние би- стабильных элементов 21-2f) группы заканчивается после прекращения входных сигналов. Количество переключенных бистабильных элементов группы в j-м блоке 1 соответствует сумме дли- тельностей входных сигналов. Последний бистабильный элемент 2h группы при установке в состояние логической 1 дает разрешение на формирование импульса. Импульс переноса формируется с помощью четвертого формирователя импульсов 32 и пятого элемента НЕ 38. При появлении на выходе последнего элемента И 3h j-ro блока на выходе формирователя 32 устанавливается низкий потенциал, которьй подается на третьи входы всех 6э-6„,кроме первого 6., и второго 6г, элементов ИЛИ первой группы этой () группы.

Импульс с выхода пятого элемента НЕ 38 обнуляет все бистабильные элементы группы, кроме первого 2, и второго 21( Первьй бистабильные элемент 2Л группы обнуляется в том случае, если при этом на входы 59 и 60 суммирования данной группы подача сигна5

0

5

0

5

.fiOB обоих операндов окончена. Второй бистабильный элемент 2Z группы обнуляется в том случае, если при этом На входах 59 и 60 суммирования данно группы подача сигнала обоих или одно Го операндов окончена. Импульс переноса подается также на вход 57 переноса следующей группы При этом,ес- JIH подача сигнала операндов на входы суммирования 59 и 60 последующему, (j + 0-му, блоку окончена, импульс переноса через элемент И 15 перебрасывает один из бистабильных элементов &. (i 1,2,..,,п) группы последую- |цего блока в единичное состояние, Ј противном случае через элемент Ji 14 перебрасывает первый бистабиль- йый элемент 8 в единичное состояние, где происходит его запоминание.После ркончания сигнала операндов на входах 59 и 60 суммирования последующе- t o блока 1 на выходе формирователя I2 снова формируется этот импульс Переноса, который переключает соответствующий бистабильный элемент 2- Группы (j+l)-го блока 1.

Запоминание импульса в этом случае необходимо, поскольку в против- йом случае произойдет наложение во времени импульса переноса с предыдущего (j-ro) блока 1 и сигналов перандов в этом (j + 1)-ом блоке ). С этой целью в каждом блоке 1 включены восьмой 19 и четырнадцатый 25 элементы И. Если в блоке 1 сформирован импульс переноса на выходе Пятого элемента НЕ 33 и одновременно подается сигнал операндов на входы 59 и 60 суммирования, то закрываются элементы И 10, 19, 20 и 25, Тем самым предотвращаете одновременное появление единиц на единичный 58 и нулевой 48 входы первого 2Л и второго 2 ,j бистабильного элемента группы. В результате первый 2, и второй 2; бистабильные элементы группы остаются в единичном состоянии.

Рассмотрим работу устройства при Вычитании. При поступлении на шины 61 и 62 вычитания соответственно уменьшаемого и вычитаемого низкий сигнал с выхода десятого 43 и одиннадцатого 44 элементов НЕ закрывает соответственно элементы И 23 и 24, в это время устройство не функционирует. Если на шине 62 вычитания закончился входной сигнал (вычитаемое), то высокий сигнал с выхода элемента

to

15

87968

НЕ 44 открывает элемент И 23 и происходит процесс сложения до тех пор, пока существует сигнал на шине 61 вычитания (уменьшаемое). Если на первой шине вычитания 61 прекратился входной сигнал, а на второй шине вычитания 62 продолжается подача сигнала, то высокий сигнал с выхода элемента НЕ 43 открывает элемент И 24. При этом бистабильные элементы 2Ј группы последовательно устанавливаются в нулевое состояние, начиная с последнего, находящегося в состоянии логической единицы, т.е. установка в нулевое состояние происходит в обратном направлении.

При обнулении первого бистабиль0

5

.,-

0

5

0

0

5

ного элемента 21 группы на выходе элемента НЕ 36 формируется импульс заема. Если при этом окончена подача сигнала операнда на вход 61 вычитания (вычитающее), все бистабильные элементы 2 группы устанавливаются в единичное состояние, в противном

случае n-й бистабильный элемент 2

п

группы остается в нулевом состоянии. Импульс заема подается также на вход 60 заема следующего (j + 1)-го блока. Если в этом блоке окончена подача сигнала операндов, на входы 61 и 62 вычитания, то в нулевом состоянии переключается соответствующий бистабильный элемент 2 j группы, в противном случае происходит запоминание импульса заема с помощью второго бистабильного элемента 9. Импульс заема вторично формируется на выходе формирователя 13 после окончания подачи сигнала операндов на входы 61 и 62 вычитания этого же блока.

Рассмотренное устройство дает технический эффект, заключающийся в повышении быстродействия как при сложении, так и при вычитании длительностей импульсов.

Формула изобретения

Устройство для сложения длительностей импульсов, содержащее k блоков суммирования, каждый из которых содержит два бистабильных элемента, четыре формирователя импульсов,восемь элементов И, четыре элемента ИЛИ,пять элементов НЕ, элемент ИЛИ-НЕ, группу из п бистабильных элементов, две группы по п элементов И и две группы по п элементов ИЛИ, причем в каждом

91548796

-м () блоке суммирования каждый -й () бистабильньш элемент руппы соединен прямым выходом с перым входом i-ro элемента И первой руппы, инверсным выходом - с первым ходом 1-го элемента И второй групэв п г м в р х т с эл т ч к и к j с И т и г вх г ч в вв эл т эл n ( по вы гр вя ве пе ро вх то ты вт гр пе вы эл до ше по эл до се се ры вы кл

пы, входом обнуления - с выходом 1-г элемента ИЛИ первой группы, а входом установки в 1 - с выходом 1-го элемента ИЛИ второй группы, причем каждый i-й элемент И первой группы,кроме n-го элемента, подключен вторым входом к выходу первого элемента И и первому входу первого элемента ИЛИ второй группы, а выходом - к первому входу (i+l)-ro элемента ИЛИ второй группы, первый вход каждого i-элемента ИЛИ первой группы, кроме n-го элемента, соединен с выходом (i+1)-го элемента И второй группы, вторые входы элементов И второй группы подключены к выходу второго элемента И и первому входу n-го элемента ИЛИ второй группы, вторые входы элементов ИЛИ первой группы соединены с шиной обнуления устройства и первыми входами первого и второго элементов ИЛИ, подключенных выходами к входам обнуления первого и второго бистабильных элементов, первьй бистабильный элемент соединен входом установки в 1 с выходом третьего элемента И, а инверсным выходом - с входом первого формирователя импульсов, соединенного выходом с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу четвертого элемента И, соединенного первым входом с выходом первого элемен- та НЕ и вторым входом первого элемента ИЛИ, а вторым входом - с первым входом третьего элемента И и входом переноса (j-1)-го блока суммирования причем второй бистабильный элемент подключен инверсным выходом к входу второго формирователя импульсов, а входом установки в 1 - к выходу пятого элемента И, соединенного первым входом с входом заема (j+l)-ro блока суммирования и первым входом шестого элемента И, второй вход которого подключен к выходу второго элемента НЕ и второму входу второго элемента ИЛИ,выход первого элемента И второй группы соединен с входом третьего формирователя импульсов,подключенного выходом к первому входу второго элемента И и входу третьего

10

0

5

5

0

0 п

5

5

0

5

элемента НЕ, выход которого является выходом заема j-го блока суммирования и соединен с вторыми входами первых п-1 элементов ИЛИ второй группы и первым входом седьмого элемента И, подключенного выходом к второму входу n-го элемента ИЛИ второй группы, а вторым входом - к выходу элемента ИЛИ-НЕ и входу четвертого элемента НЕ, выход которого соединен с вторым входом второго элемента И, причем выход n-го элемента И первой группы подключен через четвертый формирователь импульсов к первому входу первого элемента И и входу пятого элемента НЕ, выход которого является выходом переноса j-ro блока суммирования и соединен с первым входом восьмого элемента И и с третьими входами всех элементов ИЛИ первой группы, кроме первого и второго элементов, а выход восьмого элемента И подключен к третьему входу первого элемента ИЛИ первой группы, отличающееся тем, что, с целью повышения быстродействия, в каждый j-й блок суммирования введены с девятого по четырнадцатый элементы И, пятый элемент ИЛИ, с шестого по одиннадцатый элементы НЕ, элемент И-НЕ и третья группа из n/2-l элементов И, причем каждый k-й (1 Ј k ; п/2-) элемент И третьей группы подключен первым входом к прямому выходу 2k-ro бистабильного элемента группы, вторым входом - к выходу девятого элемента И, первому входу четвертого элемента ИЛИ и третьим входом первого и второго элементов ИЛИ второй группы, а выходом - к третьим входам (2k+l)-ro и (2k+2)-ro элементов ИЛИ второй группы, причем четвертый элемент ИЛИ подключен выходом к второму входу n-го элемента И первой группы, а вторым входом - к выходу первого элемента И, соединенного пер- вым входом с первым входом девятого элемента И, а вторым входом - с выходом третьего элемента ИЛИ и входом шестого элемента НЕ, выход которого подключен к второму входу восьмого элемента И, соединенного третьим входом с выходом элемента И-НЕ и входом седьмого элемента НЕ, причем выход седьмого элемента НЕ соединен с вторым входом девятого элемента И и первым входом пятого элемента ИЛИ,подключенного вторым входом к выходу

десятого элемента И и третьему входу третьего элемента ИЛИ, третьим входом - к выходу одиннадцатого элемента И и четвертому входу третьего элемента ИЛИ, а выходом - к входу первого элемента НЕ и второму входу третьего элемента И, причем десятый элемент И соединен первым входом с шиной сложения первого операнда устройства,nep вым входом элемента И-НЕ и вхрдом восьмого элемента НЕ, выход которого подключен к первому входу десятого элемента И, одиннадцатый элемент И соединен первым входом с шиной сложе- ния второго операнда устройства,вторым входом элемента И-НЕ и входом девятого элемента НЕ, подключенного выходом к второму входу десятого эле- ента И, третий элемент ИЛИ соединен пятым входом с выходом двенадцатого элемента И9 подключенного первым

входом к шине вычитания первого операнда устройства и входу десятого элемента НЕ, а вторым входом - к выходу одиннадцатого элемента НЕ,соединенного входом с шиной вычитания второго операнда устройства и первым входом тринадцатого элемента И,подключенного вторым входом к выходу десятого элемента НЕ, а выходом - к второму входу пятого элемента И,входу второго элемента НЕ и первому входу элемента ИЛИ-НЕ, соединенного вторым входом с выходом второго формирователя импульсов, а третьим входом - с выходом шестого элемента И, причем четырнадцатый элемент И подключен первым входом к выходу элемента И-НЕ, вторым входом - к выходу пятого элемента НЕ, а выходом - к третьему входу второго элемента ИЛИ первой группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения длительностей импульсов | 1988 |

|

SU1608702A1 |

| Устройство для сложения длительностей импульсов | 1986 |

|

SU1332337A1 |

| Устройство для суммирования длительностей импульсов | 1987 |

|

SU1430970A1 |

| Устройство для сложения длительностей импульсов | 1980 |

|

SU951330A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Оптоэлектронный десятичный сумматор | 1982 |

|

SU1151954A1 |

| Последовательный сумматор-вычитатель | 1986 |

|

SU1363191A1 |

| Оптоэлектронное устройство вычитания десятичных чисел | 1983 |

|

SU1136157A1 |

| Накапливающий сумматор | 1982 |

|

SU1104506A1 |

Изобретение относится к области вычислительной техники. Цель изобретения - повышение быстродействия. Устройство для сложения длительностей импульсов содержит группу блоков (разрядов) суммирования, каждый из которых содержит группу из N (N - основание системы счисления) бистабильных элементов 2, три группы 3, 4 и 5 элементов И, две группы 6 и 7 элементов ИЛИ, два бистабильных элемента 8 и 9, четырнадцать элементов И 10, 11, 14 - 25, четыре формирователя 12, 13, 31 и 32 импульсов, пять элементов ИЛИ 26 - 30, элемент И-НЕ 33, одиннадцать элементов НЕ 34 - 44 и элемент ИЛИ-НЕ 45. Устройство выполняет операции сложения и вычитания как аналоговых сигналов, заданных длительностью импульсов, так и цифровых сигналов, заданных количеством импульсов. Повышение быстродействия достигается за счет одновременной обработки входных сигналов. 1 ил.

Авторы

Даты

1990-03-07—Публикация

1987-04-22—Подача