со

00

ел ьо

1

Изобретение относится к вычислительной технике и может быть использовано в составе приставок-адаптеров к логическим анализаторам либо в качестве независимого логического анализатора временных диаграмм при наладке сложных 1Ц1фровых устройств и систем.

Целью изобретения является повышение эффективности использования оборудования,

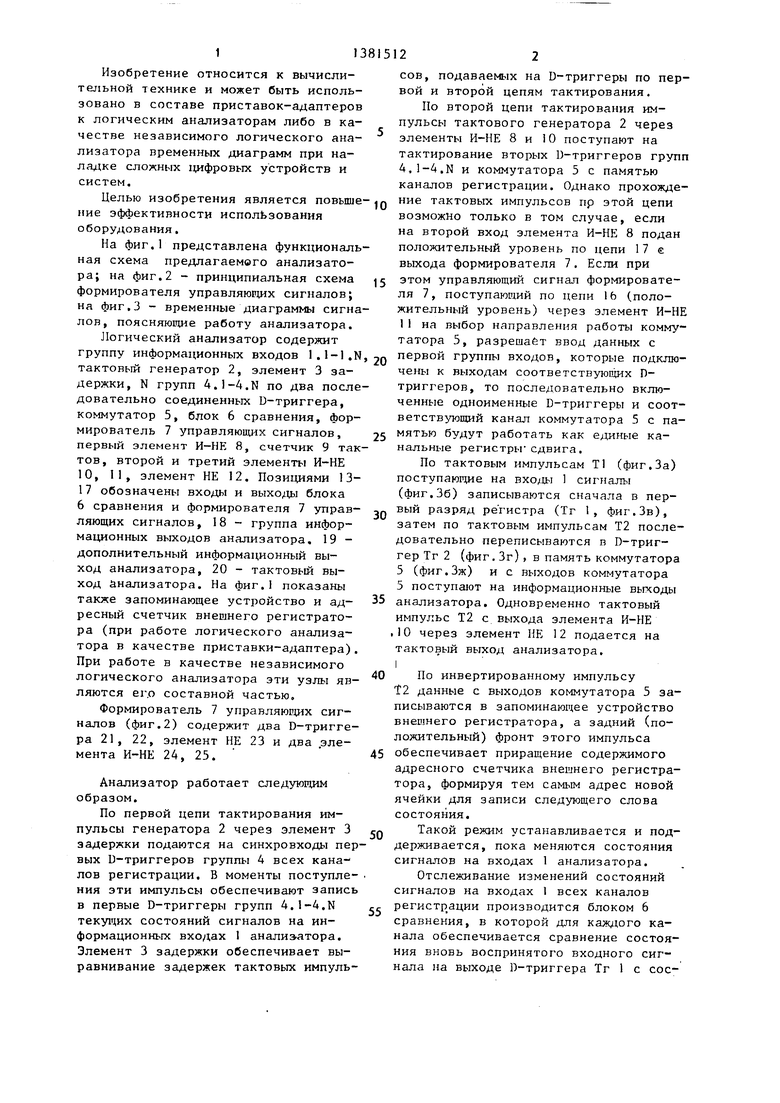

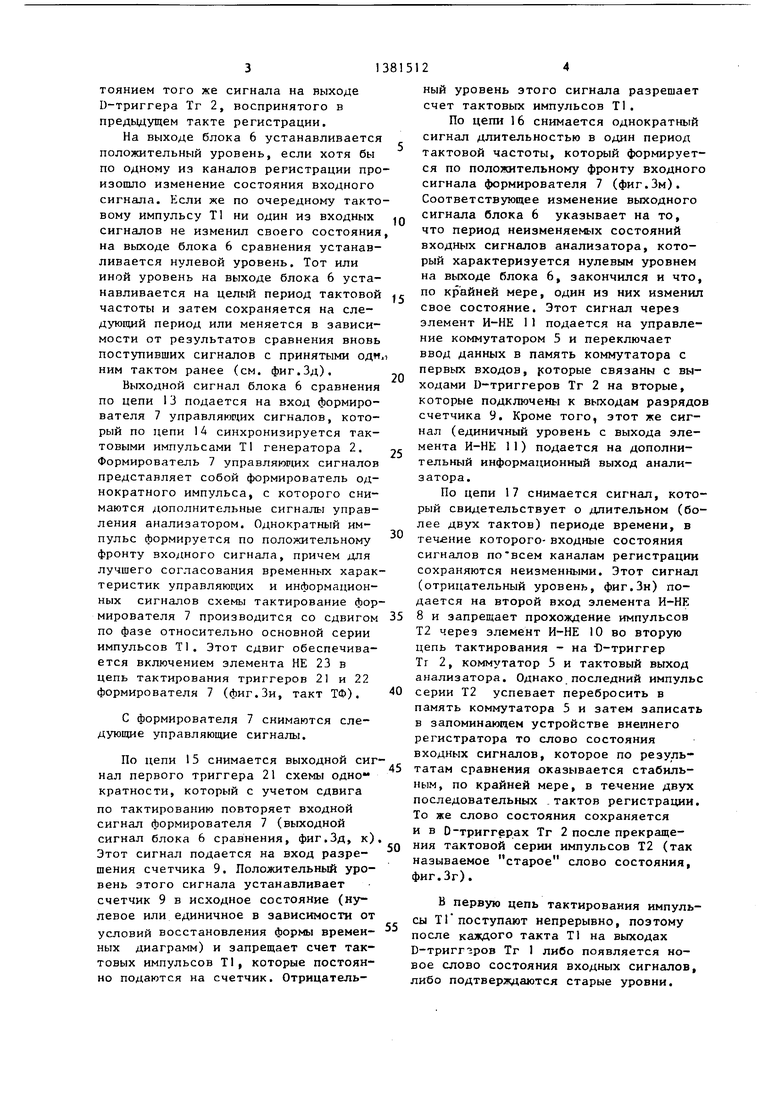

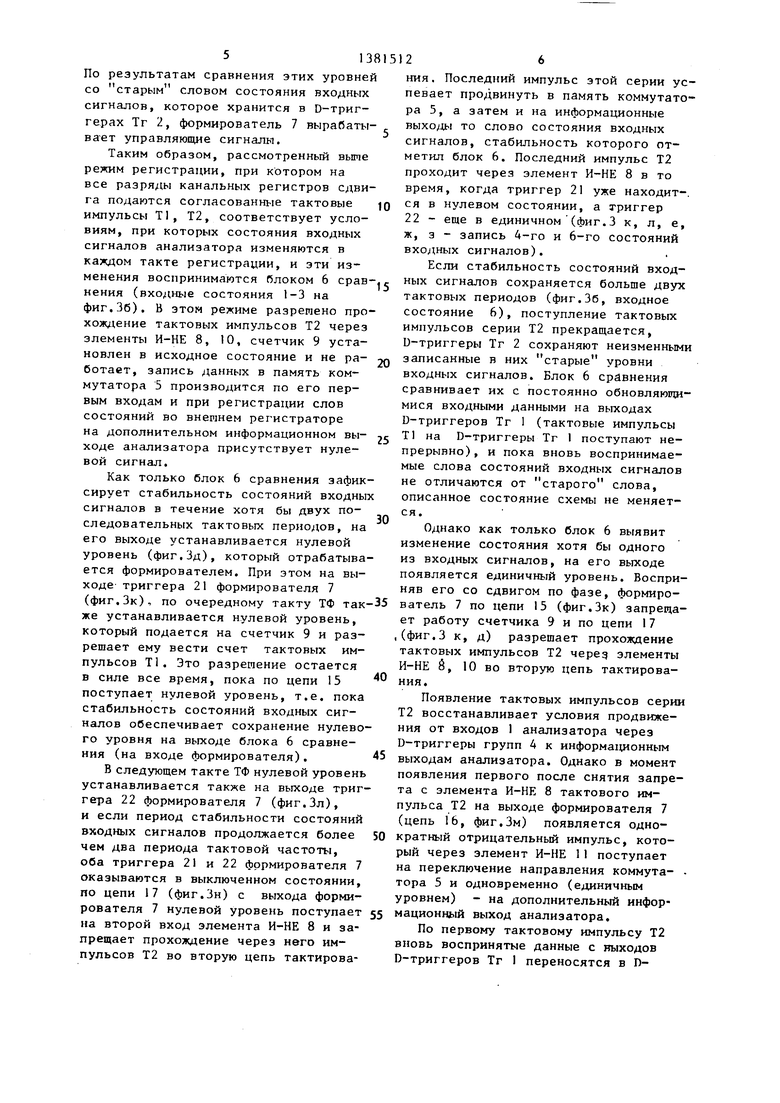

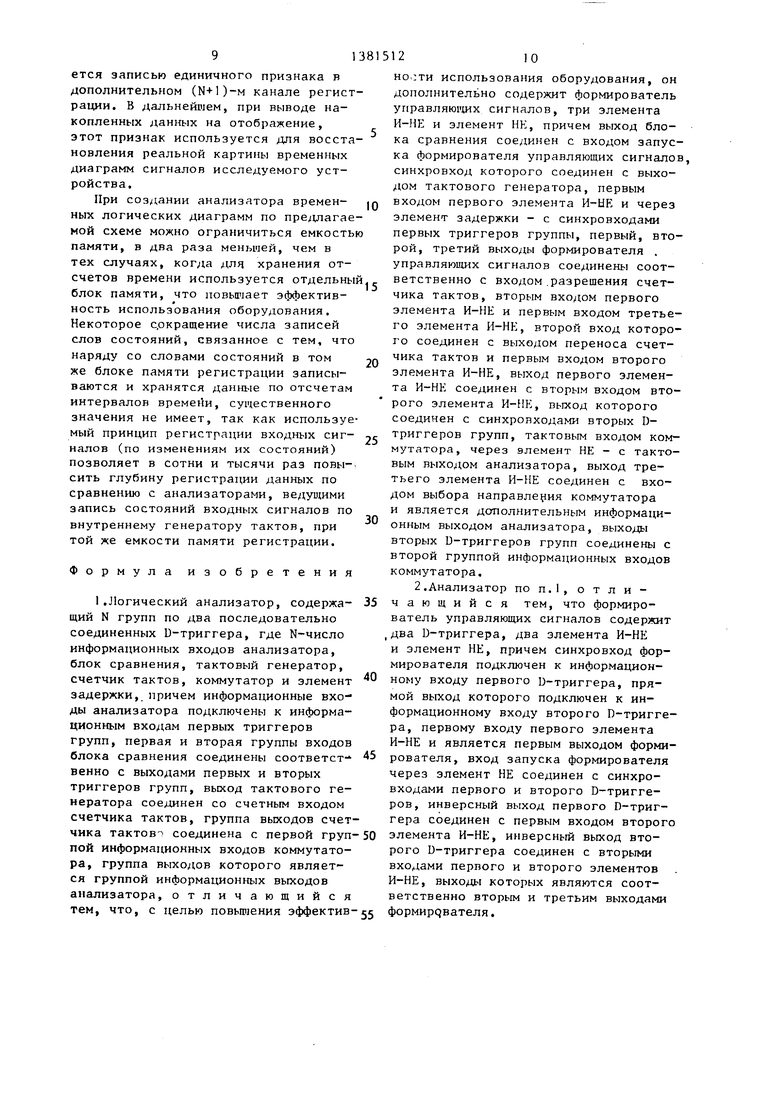

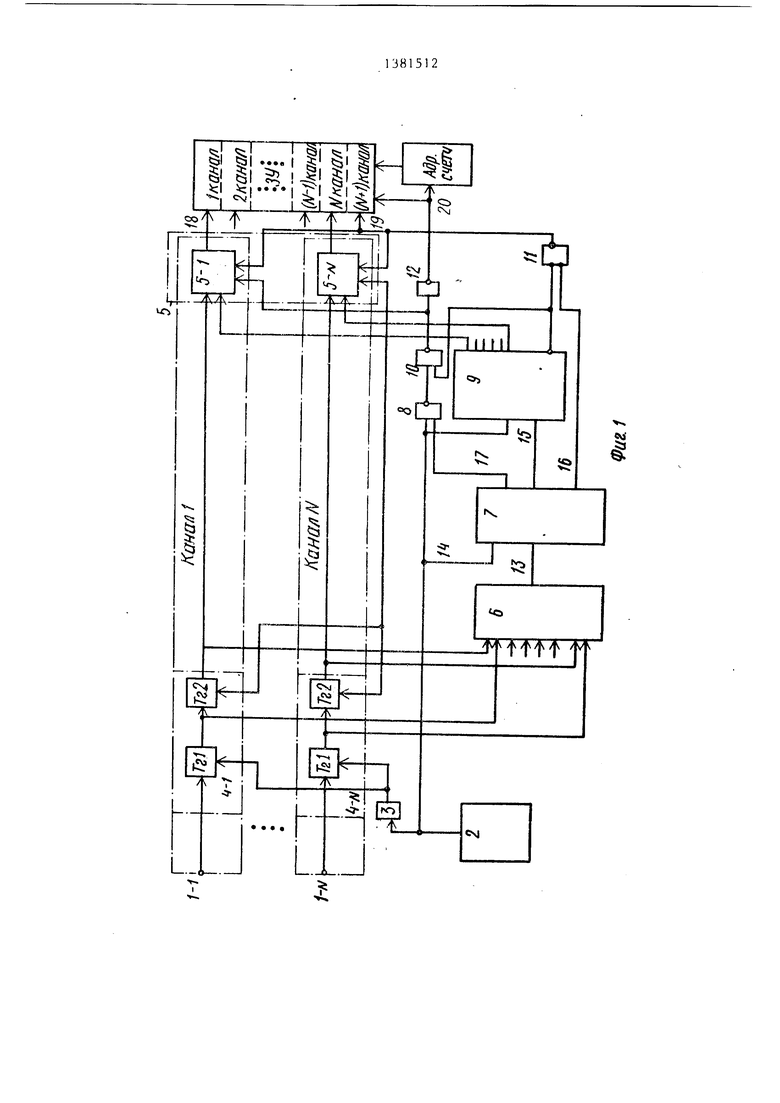

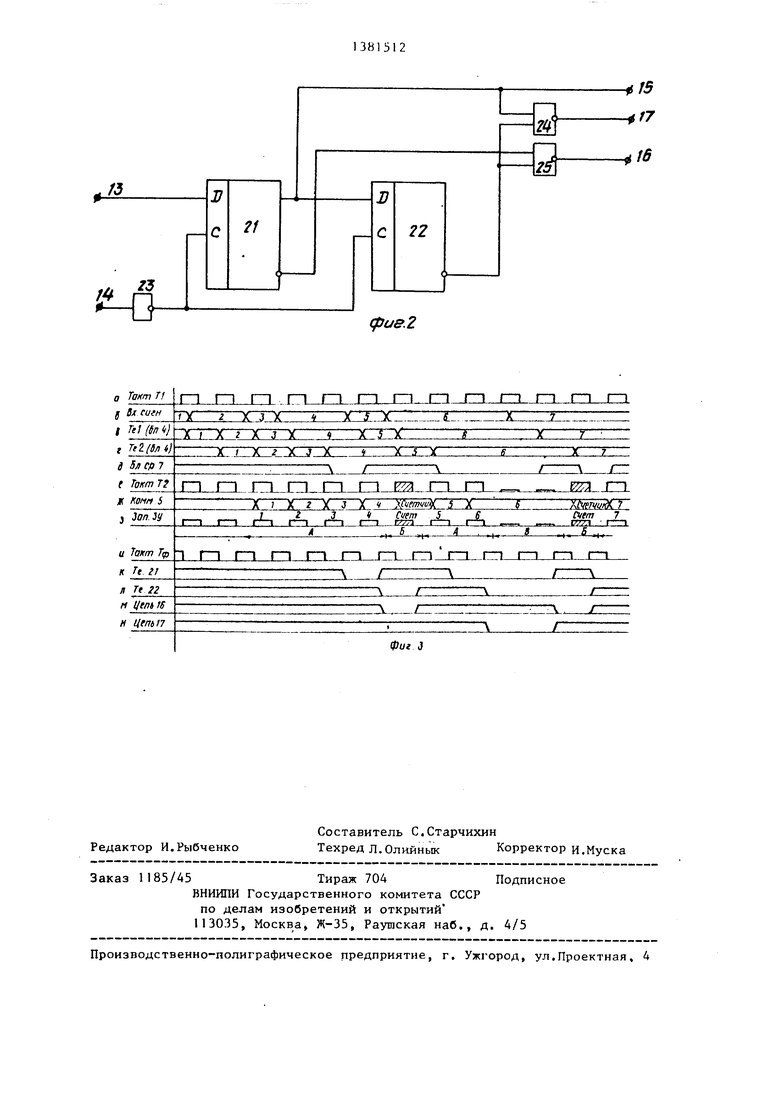

На фиг.1 представлена функциональная схема предлагаемого анализатора; на фиг,2 - принципиальная схема формирователя управляющих сигналов; на фиг.З - временные диаграммы сигналов, поясняющие работу анализатора.

Логический анализатор содержит группу информационных входов 1.1-1.N тактовый генератор 2, элемент 3 задержки, N групп 4.I-4.N по два последовательно соединенных D-триггера, коммутатор 5, блок 6 сравнения, формирователь 7 управляющих сигналов, первый элемент И-НЕ 8, счетчик 9 тактов, второй и третий элементы И-НЕ 10, II, элемент НЕ 12. Позициями 13- 17 обозначены входы и выхода блока 6 сравнения и формирователя 7 управляющих сигналов, 18 - группа информационных выходов анализатора. 19 - дополнительный информационный выход анализатора, 20 - тактовый выход анализатора. На фиг.1 показаны также запоминающее устройство и адресный счетчик внешнего регистратора (при работе логического анализатора в качестве приставки-адаптера). При работе в качестве независимого логического анализатора эти узлы являются ег.о составной частью.

Формирователь 7 управляюг91Х сигналов (фиг.2) содержит два D-триггера 21, 22, элемент НЕ 23 и два элемента И-НЕ 24, 25.

13

Анализатор работает следующим образом.

По первой цепи тактирования импульсы генератора 2 через элемент 3 задержки подаются на синхровходы первых D-триггеров группы 4 всех каналов регистрации, В моменты поступле- ния эти импульсы обеспечивают запись в первые В-триггары групп 4,1-4,N текущих состояний сигналов на информационных входах I анализатора. Элемент 3 задержки обеспечивает выравнивание задержек тактовых импуль

, 10

15

20

Q 815122

сов, подаваемых на D-триггеры по первой и второй цепям тактирования.

По второй цепи тактирования импульсы тактового генератора 2 через элементы И-НЕ 8 и 10 поступают на тактирование вторых 1)-триггеров групп 4.1-4.N и коммутатора 5 с памятью каналов регистрации. Однако прохождение тактовых импульсов пр этой цепи возможно только в том случае, если на второй вход элемента И-НЕ 8 подан положительный уровень по цепи 17 е выхода формирователя 7. Если при этом управляющий сигнал формирователя 7, поступаюпшй по цепи 1Ь (положительный уровень) через элемент И-НЕ 11 на выбор направления работы коммутатора 5, разрешает ввод данных с первой группы входов, которые подключены к выходам соответствующих П- триггеров, то последовательно включенные одноименные D-триггеры и соответствующий канал коммутатора 5 с па25 мятью будут работать как единые канальные регистры сдвига.

По тактовым импульсам Т1 (фиг,За) поступающие на входы 1 сигналы (фиг.Зб) записываются сначала в первый разряд регистра (Тг 1, фиг.Зв), затем по тактовым импульсам Т2 последовательно переписываются в D-триг- гер Тг 2 (фиг. Зг) , в память коммутатора 5 (фиг,3ж) и с выходов коммутатора 5 поступают на информационные ВЬРСОДЫ

35 анализатора. Одновременно тактовый импульс Т2 с выхода элемента И-НЕ ,10 через элемент НЕ 12 подается на тактовый выход анализатора.

I 40 По инвертированному импульсу

t2 данные с выходов коммутатора 5 записываются в запоминающее устройство внешнего регистратора, а задний (положительный) фронт этого импульса 45 обеспечивает приращение содержимого адресного счетчика внешнего регистратора, формируя тем самым адрес новой ячейки для записи следующего слова состояния.

Такой режим устанавливается и поддерживается, пока меняются состояния сигналов на входах 1 анализатора.

Отслеживание изменений состояний сигналов на входах 1 всех каналов регистр ации производится блоком 6 сравнения, в которой для каждого канала обеспечивается сравнение состояния вновь воспринятого входного сигнала на выходе D-триггера Тг 1 с сос30

55

тоянием того же сигнала на выходе D-триггера Тг 2, воспринятого в предыдущем такте регистрации.

На выходе блока 6 устанавливается положительный уровень, если хотя бы по одному из каналов регистрации произошло изменение состояния входного сигнала. же по очередному тактовому импульсу Т1 ни один из входных сигналов не изменил своего состояния на выходе блока 6 сравнения устанавливается нулевой уровень. Тот или иной уровень на выходе блока 6 устанавливается на целый период тактовой частоты и затем сохраняется на следующий период или меняется в зависимости от результатов сравнения вновь

поступивших сигналов с принятыми ОДМ

ним тактом ранее (см. фиг.Зд).

Выходной сигнал блока 6 сравнения по цепи 13 подается на вход формирователя 7 управляющих сигналов, который по цепи 14 синхронизируется тактовыми импульсами Т1 генератора 2. Формирователь 7 управляюпшх сигналов представляет собой формирователь однократного импульса, с которого снимаются дополнительные сигналы управления анализатором. Однократный импульс формируется по положительному фронту входного сигнала, причем для лучшего согласования временных характеристик управляюршх и информационных сигналов схемы тактирование формирователя 7 производится со сдвигом по фазе относительно основной серии импульсов Т1. Этот сдвиг обеспечивается включением элемента НЕ 23 в цепь тактирования триггеров 21 и 22 формирователя 7 (фиг.Зи, такт ТФ).

С формирователя 7 снимаются следующие управляющие сигналы.

По цепи 15 снимается выходной сигнал первого триггера 21 схемы одно кратности, который с учетом сдвига по тактированию повторяет входной сигнал формирователя 7 (выходной сигнал блока 6 сравнения, фиг.Зд, к). Этот сигнал подается на вход разрешения счетчика 9. Положительный уровень этого сигнала устанавливает счетчик 9 в исходное состояние (нулевое или единичное в зависимости от условий восстановления формы временных диаграмм) и запрещает счет тактовых импульсов TI, которые постоянно подаются на счетчик. Отрицатель0

д

5

ный уровень этого сигнала разрешает счет тактовых импульсов Т1 .

По цепи 16 снимается однократный сигнал длительностью в один период тактовой частоты, который формируется по положительному фронту входного сигнала формирователя 7 (фиг.3м). Соответствующее изменение выходного сигнала блока 6 указывает на то, что период неизменяемых состояний входных сигналов анализатора, который характеризуется нулевым уровнем на выходе блока 6, закончился и что, по крайней мере, один из них изменил свое состояние. Этот сигнал через элемент И-НЕ 11 подается на управление коммутатором 5 и переключает ввод данных в память коммутатора с первых входов, роторые связаны с выходами D-триггеров Тг 2 на вторые, которые подключены к выходам разрядов счетчика 9. Кроме того, этот же сигнал (единичный уровень с выхода элемента И-НЕ 11) подается на дополнительный информационный выход анализатора.

По цепи 17 снимается сигнал, который свидетельствует о длительном (более двух тактов) периоде времени, в течение которого- входные состояния сигналов по всем каналам регистрации сохраняются неизменными. Этот сигнал (отрицательный уровень, фиг.Зн) подается на второй вход элемента И-НЕ 5 8 и запрещает прохождение импульсов Т2 через элемент И-НЕ 10 во вторую цепь тактирования - на D-триггер Тг 2, коммутатор 5 и тактовый выход анализатора. Однако последний импульс серии Т2 успевает перебросить в память коммутатора 5 и затем записать в запоминающем устройстве внешнего регистратора то слово состояния входных сигналов, которое по результатам сравнения оказывается стабильным, по крайней мере, в течение двух последовательных .тактов регистрации. То же слово состояния сохраняется и в О-триггерах Тг 2 после прекращения тактовой серии импульсов Т2 (так

0

0

5

0

5

называемое старое слово состояния, фиг.Зг).

В первую цепь тактирования импульсы Т Г поступают непрерывно, поэтому после каждого такта Т1 на выходах D-тритров Тг 1 либо появляется новое слово состояния входных сигналов, либо подтверждаются старые уровни.

5138

По результатам сравнения этих уровней со старым словом состояния входных сигналов, которое хранится в D-триг- герах Тг 2, формирователь 7 выраВаты- ва-ет управляющие сигналы.

Таким образом, рассмотренный выше режим регистрации, при котором на все разряды канальных регистров сдвига подаются согласованные тактовые импульсы Т1, Т2, соответствует условиям, при которых состояния входных сигналов анализатора изменяются в каждом такте регистрации, и эти изменения воспринимаются блоком 6 сравнения (входные состояния 1-3 на фиг.Зб). В этом режиме разрегаено прохождение тактовых импульсов Т2 через элементы И-НЕ 8, 10, счетчик 9 установлен в исходное состояние и не ра- ботает, запись данных в память коммутатора 5 производится по его первым входам и при регистрации слов состояний во внешнем регистраторе на дополнительном информационном вы- ходе анализатора присутствует нулевой сигнал.

Как только блок 6 сравнения зафиксирует стабильность состояний входных сигналов в течение хотя бы двух по- следовательных тактовых периодов, на его выходе устанавливается нулевой уровень (фиг.Зд), который отрабатывается формирователем. При этом на выходе- триггера 21 формирователя 7 (фиг.Зк), по очередному такту ТФ также устанавливается нулевой уровень, который подается на счетчик 9 и разрешает ему вести счет тактовых импульсов Т1. Это разрешение остается в силе все время, пока по цепи 15 поступает нулевой уровень, т.е. пока стабильность состояний входных сигналов обеспечивает сохранение нулевого уровня на выходе блока 6 сравнения (на входе формирователя).

В следующем такте ТФ нулевой уровень устанавливается также на выходе триггера 22 формирователя 7 (фиг.3л), и если период стабильности состояний входных сигналов продолжается более чем два периода тактовой частоты, оба триггера 21 и 22 формирователя 7 оказываются в выключенном состоянии, по цепи 17 (фиг.Зн) с выхода формирователя 7 нулевой уровень поступает на второй вход элемента И-НЕ 8 и запрещает прохождение через него импульсов Т2 во вторую цепь тактирова26

ния. Последний импульс этой серии успевает продвинуть в память коммутатора 5, а затем и на информационные выходы то слово состояния входных сигналов, стабильность которого отметил блок 6. Последний импульс Т2 проходит через элемент И-НЕ 8 в то время, когда триггер 21 уже находится в нулевом состоянии, а триггер 22 - еще в единичном (фиг.3 к, л, е, ж, 3 - запись 4-го и 6-го состояний входных сигналов).

Если стабильность состояний входных сигналов сохраняется больше двух тактовых периодов (фиг.Зб, входное состояние 6), поступление тактовых импульсов серии Т2 прекращается, D-триггеры Тг 2 сохраняют неизменным записанные в них старые уровни входных сигналов. Блок 6 сравнения сравнивает их с постоянно обновляющимися входными данными на выходах D-триггеров Тг 1 (тактовые импульсы Т1 на D-триггеры Тг I поступают непрерывно) , и пока вновь воспринимаемые слова состояний входных сигналов не отличаются от старого слова, описанное состояние схемы не меняется.

Однако как только блок 6 выявит изменение состояния хотя бы одного из входных сигналов, на его выходе появляется единичный уровень. Восприняв его со сдвигом по фазе, формирователь 7 по цепи 15 (фиг.Эк) запрещает работу счетчика 9 и по цепи 17 ,(фиг.З к, д) разрешает прохождение тактовых импульсов Т2 черед элементы И-НЕ 8, 10 во вторую цепь тактирования.

Появление тактовых импульсов сери Т2 восстанавливает условия продвижения от входов 1 анализатора через D-триггеры групп 4 к информахщонным выходам анализатора. Однако в момент появления первого после снятия запрета с элемента И-НЕ 8 тактового импульса Т2 на выходе формирователя 7 (цепь 16, фиг.3м) появляется однократный отрицательный импульс, который через элемент И-НЕ 11 поступает на переключение направления коммута- тора 5 и одновременно (единичным уровнем) - на дополнительный информационный выход анализатора.

По первому тактовому импульсу 12 вновь воспринятые данные с выходов П-триггеров Тг I переносятся в D71

триггеры Тг 2, при этом хранившееся в D-триггерах Тг 2 старее слово состояния теряется, так как в это время ввод данных в память коммутатора 5 разрешается не с первых, а с вторых входов, которые подключены к выходам разрядов счетчика 9, В результате по первому после перерыва тактовому импульсу Т2 в память комму татора 5, а затем и в запоминающее устройство внешнего регистратора записывается накопленное к этому времени содержимое счетчика 9, причем одновременно в /(ополнительный (N+ +1)-й каиал запоминающего устройства записывается единичный признак, указывающий на то, что данная ячейка хранит отсчет времени, а не слово состояния входных сигналов.

Потеря старого слова состояния при считывании его с выходов П-триг- геров не имеет значения, так как оно уже записано в запоминающем устройст ве.

Очередное слово состояния с выходов D-триггеров Тг 2 через первые входы коммутатора 5 записывается в его память, а затем и в запоминающее устройство, причем эта запись сопровождается введением нулевого признака в дополнительный (Ы+1)-й канал регистрации этого устройства.

Если входные уровни остаются стабильными только в течение двух последовательных периодов тактовой час тоты (фиг.Зб, входное сос тояние 4), работа устройства не меняется, так как уровень запрета прохождения тактов Т2 через элемент И-Ш1 8 не успевает сформироваться, прерывание так- товой серии Т2 не производится. В этом случае стабильные в течение двух последовательных тактов состояния входных сигналов (состояние 4, фиг.Зб) записываются в память комму- татора 5, а затем в запоминающее устройство внешнего регистратора по такту Т2 описанным вьщ1е образом (при нулевом состоянии триггера 21 и положительном состоянии триггера 22, см. фиг.Зж, 3, л, к), а следующий тактовый импульс Т2 совпадает по времени с появлением однократного импульс переключения коммутатора 5 по цепи 16 (фиг.3м), в связи с чем в память коммутатора 5 вместо повторной записи стабильных состояний с выходов D-триггеров Тг 2 записывается содер

12

8

Q 0

5

5 0 5

0

жимое счетчика 9, который в этой ситуации успевает просчитать только один тактовый импульс. Одновременно записывается единица в дополнительный (N+1)-H служебный канал регистрации запоминающего устройства.

Если же состояния входных сигналов остаются неизменными столь длительное время, что счетчик 10 успевает заполниться до предела, выходной сигнал переноса этого счетчика через элемент И-НЕ 11 поступает на переключение входов памяти коммутатора 5 и на дополнительный информационный ход анализатора. Этот же сигнал переноса через элемент И-НЕ 10 вводится во вторую цепь тактирования и обеспечивает запись сначала в память коммутатора 5, а затем и в запоминающее устройство содержимого счетчика 9, сопроводив его записью единичного признака в дополнительный (Ы+О-й канал регистрации запоминающего устройства.

В описанном порядке устройство работает до полного завершения регист- рации, в результате которой в запоминающем устройстве внешнего регистратора оказываются записанными все поступившие на входы 1 анализатора слова состояний входных сигналов. При этом каждое слово состояния, существовавшее на входах анализатора не более одного тактового периода,занимает по одной ячейке запоминающего устройства.

Если слово состояния не изменяется на входах устройства в течение двух и более тактов,, его запись в запоминающем устройстве занимает две ячейки. В первой из зтих ячеек записывается само слово состояния входных сигналов, а в следующей - двоичный отсчет времени существования этогр сигнала состояния, который сопровождается записью единичного признака в дополнительном (N+1)-M канале регистрации.

Если состояния входных сигналов не меняются в течение столь длительного периода времени, что счетчик 9 успевает переполниться, число ячеек для записи отсчетов времени возрастает (по одной ячейке на интервал времени, соответствующий полной емкости счетчика 9). Запись каждого отсчета времени, в том числе и отсчета по переполненному счетчику, сопровожда-

ется записью единичного признака в дополнительном (Н+О-м канале регистрации. В дальнейшем, при выводе накопленных данных на отображение, этот признак используется для восстановления реальной картины временных диаграмм сигналов исследуемого устройства.

При создании анализатора времен- ных логических диаграмм по предлагаемой схеме можно ограничиться емкостью памяти, в два раза меньшей, чем в тех случаях, когда для хранения от|Q

151210

но.:ти использования оборудования, он дополнительно содержит формирователь управляющих сигналов, три элемента И-НЕ и элемент НЕ, причем выход блока сравнения соединен с входом запуска формирователя управляющих сигналов, синхровход которого соединен с выходом тактового генератора, первым входом первого элемента И-ЫЕ и через элемент задержки - с синхровходами первых триггеров группы, первый, второй, третий выходы формирователя . управляющих сигналов соединены соот

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Логический анализатор | 1986 |

|

SU1363211A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛА ДОПОЛНИТЕЛЬНОЙ ИНФОРМАЦИИ СОВМЕСТНО С ТЕЛЕВИЗИОННЫМ СИГНАЛОМ ИЗОБРАЖЕНИЯ И ВАРИАНТЫ СИСТЕМ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1994 |

|

RU2033704C1 |

| Устройство для регистрации сигналов, представленных в цифровой форме | 1976 |

|

SU659904A1 |

Изобретение относится к вычислительной технике и может быть использовано при наладке сложных цифровых устройств. Целью изобретения является повьппение эффективности использования оборудования. Отличительной особенностью логического анализатора является то, что он обеспечивает регистрацию входных сигналов не по каждому тактовому импульсу, а лишь по тем тактам, во время которых происходит изменение сигнала хотя бы на одном информационном входе, что позволяет значительно повысить глубину регистрации. При этом отсчеты времени, определяющие такты, на которых происходило изменение информационных сигналов, запоминаются в том же блоке памяти, что и сами слова состояний, что повышает эффективность ис пользования оборудования. ф-лы, 3 ил. 1 з.п.

счетов времени используется отдельный,- ветственно с входом.разрешения счетблок памяти, что повьшшет эффективность использования оборудования. Некоторое с.окращение числа записей слов состояний, связанное с тем, что наряду со словами состояний в том же блоке памяти регистрации записываются и хранятся данные по отсчетам интервалов времени, существенного значения не имеет, так как используемый принцип регистрации входных сигналов (по изменениям их состояний) позволяет в сотни и тысячи раз повы-: сить глубину регистрации данных по сравнению с анализаторами, ведуи;ими запись состояний входных сигналов по внутреннему генератору тактов, при той же емкости памяти регистрации.

Формула изобретения

1 Логический анализатор, содержащий N групп по два последовательно соединенных D-триггера, где N-число информационных входов анализатора, блок сравнения, тактовый генератор, счетчик тактов, коммутатор и элемент задержки,, причем информационные входы анализатора подключены к информационным входам первых триггеров групп, первая и вторая группы входов блока сравнения соединены соответст- венно с выходами первых и вторых триггеров групп, выход тактового генератора соединен со счетным входом счетчика тактов, группа выходов счет20

25

30

35

40

45

чика тактов, вторым входом первого элемента И-ИЕ и первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом переноса счетчика тактов и первым входом второго элемента И-НЕ, выход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ, выход которого соединен с синхровходами вторых I)- триггеров групп, тактовым входом коммутатора, через элемент НЕ - с тактовым выходом анализатора, выход третьего элемента И-НЕ соединен с входом выбора направления коммутатора и является дополнительным информационным выходом анализатора, выходы вторых D-триггеров групп соединены с второй группой информационных входов коммутатора,

чика тактов- соединена с первой груп-50 элемента И-НЕ, инверсный выход втопой информационных входов коммутатора, группа выходов которого является группой информационных выходов анализатора, отличающийся

тем, что, с целью повьго1ения эффектив-дз формирдвателя.

0

5

0

5

0

5

чика тактов, вторым входом первого элемента И-ИЕ и первым входом третьего элемента И-НЕ, второй вход которого соединен с выходом переноса счетчика тактов и первым входом второго элемента И-НЕ, выход первого элемента И-НЕ соединен с вторым входом второго элемента И-НЕ, выход которого соединен с синхровходами вторых I)- триггеров групп, тактовым входом коммутатора, через элемент НЕ - с тактовым выходом анализатора, выход третьего элемента И-НЕ соединен с входом выбора направления коммутатора и является дополнительным информационным выходом анализатора, выходы вторых D-триггеров групп соединены с второй группой информационных входов коммутатора,

рого D-триггера соединен с вторыми входами первого и второго элементов И-НЕ, выходы которых являются соответственно вторым и третьим выходами

a Такт Т

cfJu&.Z

Г-1 f-1 ГП n ГП (-1

| Electronic Design, 1982, Sept | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Топочная решетка для многозольного топлива | 1923 |

|

SU133A1 |

| Гидравлическая дистанционная передача для осуществления обратной связи между золотником сервомотора и золотником датчика | 1951 |

|

SU94976A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-31—Подача