Изобретение относится к вычислитель- внешнего тактирующего сигнала по любому ной технике, в частности к технике средств из действующих входов 6. контроля и наладки сложных цифровыхЗадержка, которую оказывает элемент

устройств и систем.ИЛИ 8 импульсам, поступающим на вход

Цель изобретения - расширение функ- тактирования буферного регистра 2 относи- циональных возможностей за счет обеспе- тельно импульсов, поданных на его входы,

обеспечивает уверенную запись как признаков тактов регистрации в служебные каналы (запись «1 - для действующего в данный- момент такта, «О - для всех

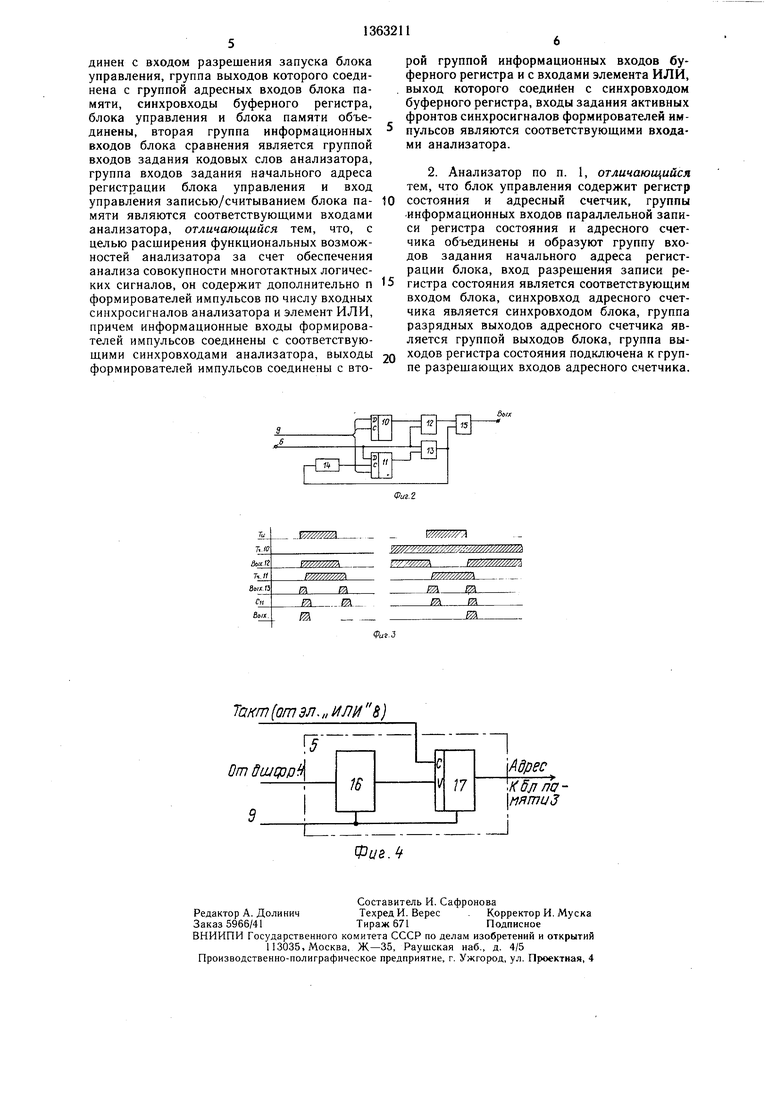

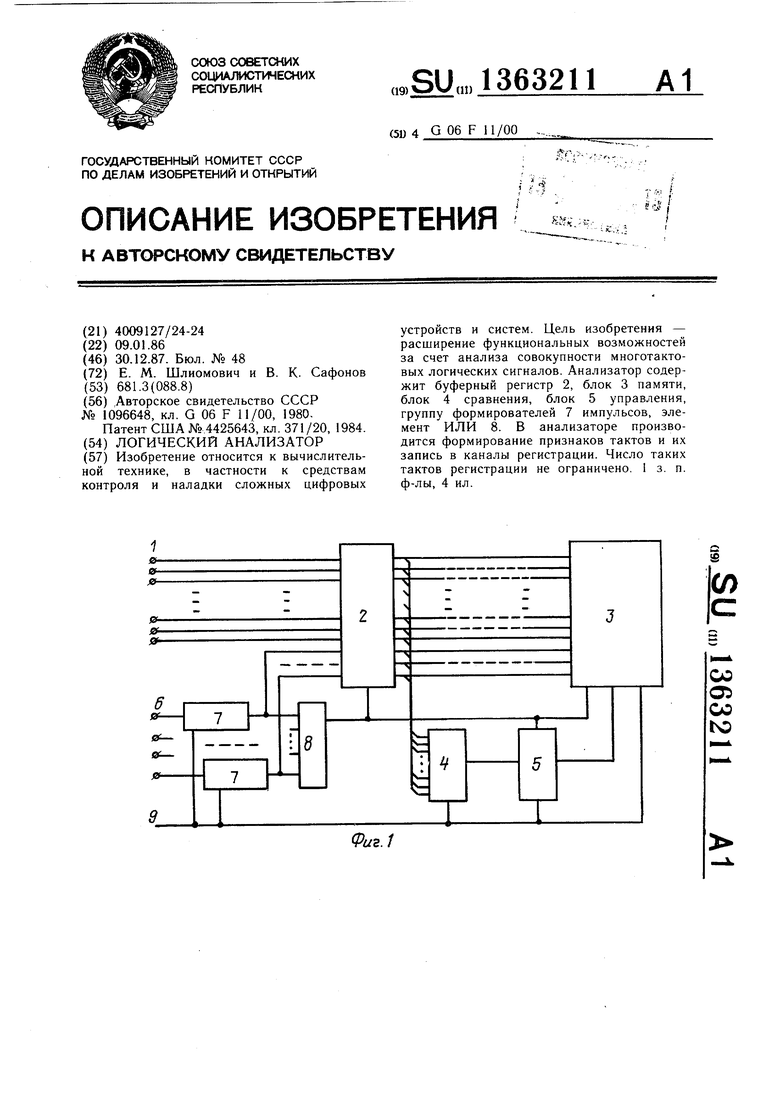

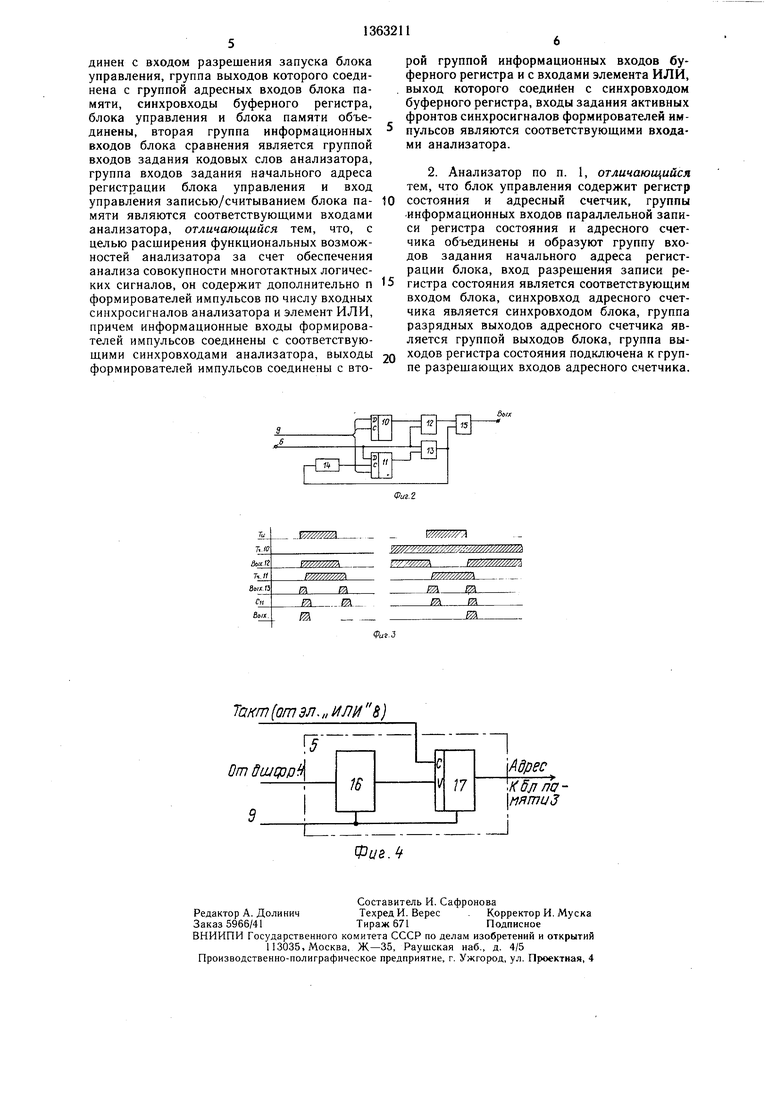

формирователя импульсов; на фиг. 3 - вре- 0 остальных тактов), так и входных дан- менные диаграммы работы формирователя ных в рабочие каналы регистрации, тактовых импульсов; на фиг. 4 - схемаЗаписанные в буферный регистр 2 призблока управления.наки тактов вместе с данными, которые

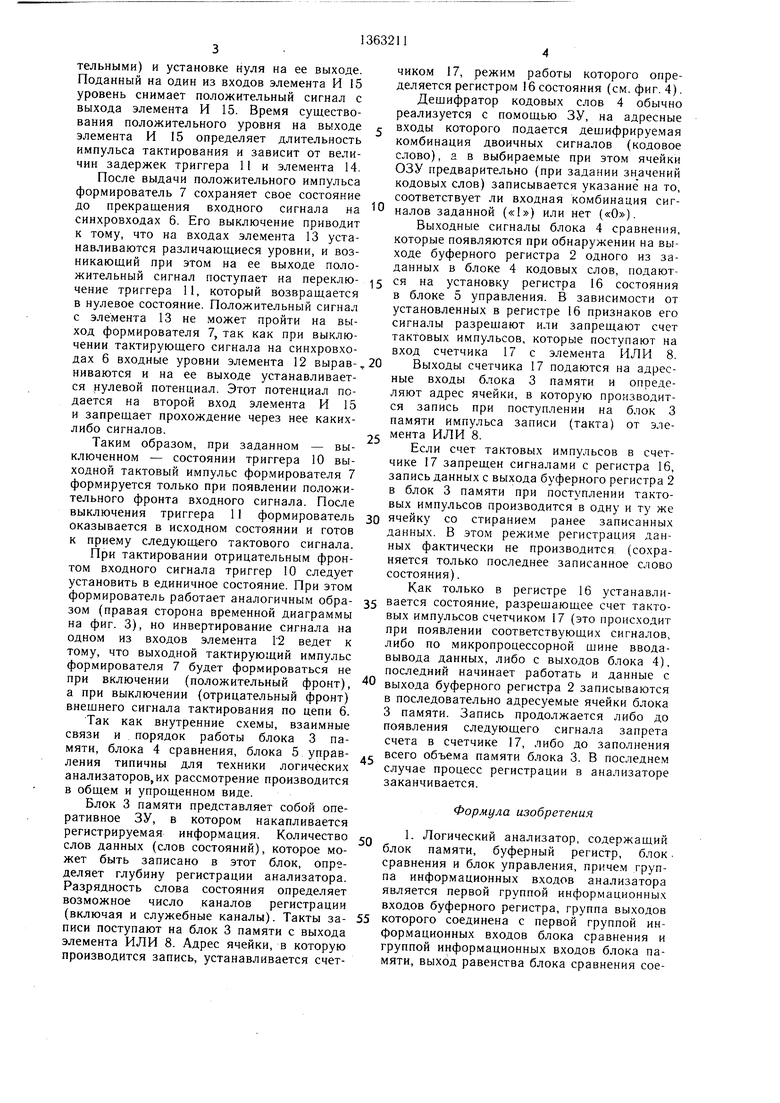

Анализатор содержит группу информа- зарегистрированы в этом такте по другим ционных входов 1, буферный регистр 2, каналам, поступают на первую группу

чения анализа совокупности многотакт- ных логических сигналов.

На фиг. 1 представлена структурная схема анализатора; на фиг. 2 - схема

блок 3 памяти, блок 4 сравнения, блок 5 управления, группу синхровходов 6, группу из п формирователей 7 импульсов, элемент ИЛИ 8, входы 9 задания активных фронтов синхросигналов.

входов блока 4 сравнения и могут быть учтены при задании управляющих кодовых слов. Затем, по разрешающим сигналам блока 5 управления эти признаки в составе полного слова состояний контролируеПри установке триггера 10 в одно из рабочих состояний (например нулевое, левая часть временных диаграмм на фиг. 3), которое производится сигналами с входов 9, триггер 11 выключается. Если входной сигФормирователь сигналов содержит триг- 20 мых точек испытуемого устройства записы- геры 10 и 11, элементы ИСКЛЮЧАЮ- ваются в блок 3 памяти и могут быть ис- ЩЕЕ ИЛИ 12 и 13, элемент 14 задерж- пользованы для идентификации хранимых ки, элемент .И 15.в нем данных.

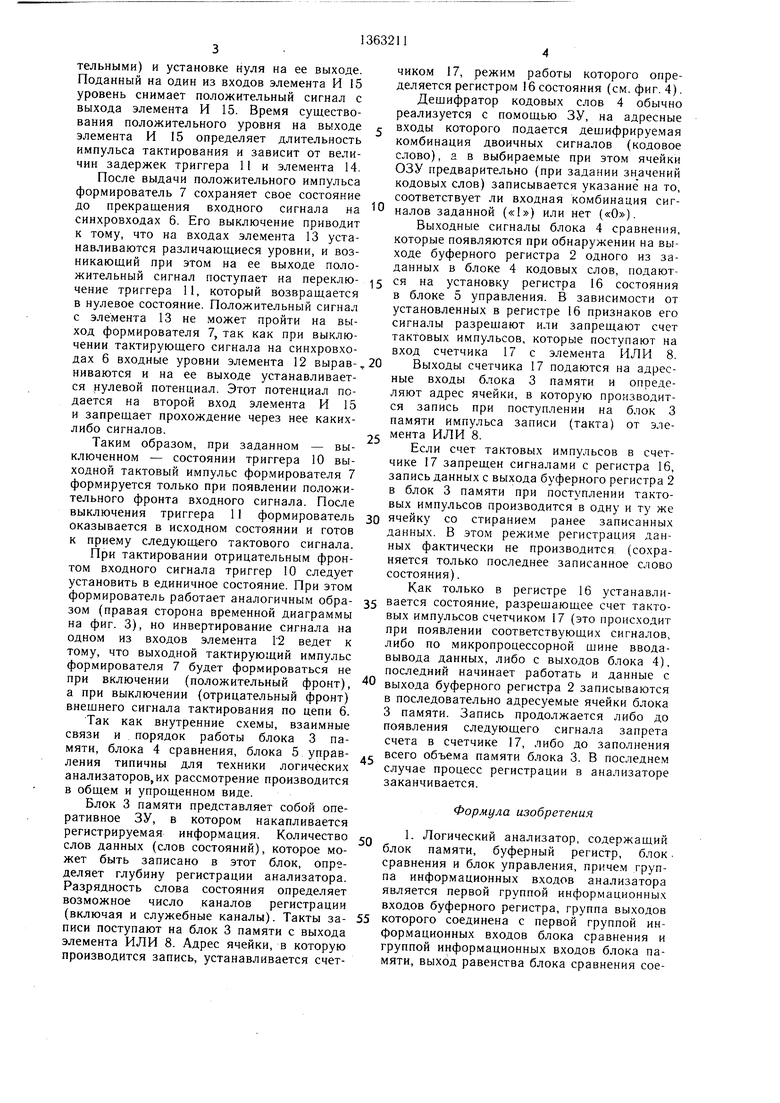

Блок управления содержит регистр 16Формирователь 7 импульсов работает

состояния и адресный счетчик 17. следующим образом.

Анализатор работает следующим обра- - зом.

В процессе работы данные от испытуемого устройства через входы 1 каналов регистрации поступают на входы буферного регистра 2 (элементы присоединения ,Q нал тактирования на синхровходах 6 от- каналов к испытуемому устройству не сутствует, на входах и выходах элементов рассматриваются). Внешние сигналы такти- ИСКЛЮЧАЮШЕЕ ИЛИ 12 и 13 уста- рования от испытуемого устройства подаются навливаются нулевые уровни, которые по- на анализатор через входы 6. Поскольку даются на входы элемента И 15. В ре- при определении условий регистрации в ка- зультате на выходе элемента И 15 (выход честве активного может быть задан как формирователя) также устанавливается ну- положительный, так и отрицательный фронт левой уровень. Если триггер 10 устанав- внешнего тактирующего сигнала произволь- ливается в единичное состояние, положение ной длительности, а для записи приз- не меняется: положительный сигнал с вы- нака в служебный канал и для так- хода элемента 12 запрещается отрицатель- тирования буферного регистра 2, блока 3 ным уровнем с выхода элемента 13 и не памяти и блока 5 управления необходи- 40 проходит через элемент И 15. мы нормированные сигналы в. предлагаемуюПри появлении положительного фронта

схему введены формирователи 7, которые входного сигнала тактирования на синхро- вырабатывают короткие положительные им- входах 6 на каждой паре входов эле- пульсы тактирования.ментов ИСКЛЮЧАЮШЕЕ ИЛИ 2 и 13

дс устанавливаются различающиеся уровни.

Эти импульсы с выхода формировате- что приводит к появлению положительных

сигналов на их выходах. Эти сигналы поступают на входы элемента И 15 и на ее выходе также появляется положительный сигнал. Одновременно положительный эти же сигналы подаются на входы 50 перепад напряжения с выхода элемента общие для всех формирователей и эле- ИСКЛЮЧАЮШЕЕ ИЛИ 13 через элемент 14 мента ИЛИ 8, и с его выхода распре- задержки поступает на тактовый вход деляются по входам тактирования буфер- триггера 11 и переводят его в состоя- ного регистра 2, блока 3 памяти и блока 5 ние, которое соответствует установленному управления. Такое включение обеспечивает в этот момент уровню входного сигнала запись входных данных в буферный регистр 55 тактирования на синхровходах 6 (в данном 2, возможность их перезаписи в блок 3 па- случае - в единичное состояние). Это мяти и тактирование адресного счетчика 17 приводит к выравниванию уровней на вхо- в блоке 5 управления при поступлении дах элемента 13 (они становятся положилей 7 подаются на специально выделенные для них входы буферного регистра 2, которые и являются входами служебных каналов регистрации. Кроме того.

зарегистрированы в этом такте по другим каналам, поступают на первую группу

входов блока 4 сравнения и могут быть учтены при задании управляющих кодовых слов. Затем, по разрешающим сигналам блока 5 управления эти признаки в составе полного слова состояний контролируемых точек испытуемого устройства записы- ваются в блок 3 памяти и могут быть ис- пользованы для идентификации хранимых в нем данных.

При установке триггера 10 в одно из рабочих состояний (например нулевое, левая часть временных диаграмм на фиг. 3), которое производится сигналами с входов 9, триггер 11 выключается. Если входной сигследующим образом.

- нал тактирования на синхровходах 6 от- сутствует, на входах и выходах элементов ИСКЛЮЧАЮШЕЕ ИЛИ 12 и 13 уста- навливаются нулевые уровни, которые по- даются на входы элемента И 15. В ре- зультате на выходе элемента И 15 (выход формирователя) также устанавливается ну- левой уровень. Если триггер 10 устанав- ливается в единичное состояние, положение не меняется: положительный сигнал с вы- хода элемента 12 запрещается отрицатель- ным уровнем с выхода элемента 13 и не проходит через элемент И 15. При появлении положительного фронта

тельными) и установке нуля на ее выходе. Поданный на один из входов элемента И 15 уровень снимает положительный сигнал с выхода элемента И 15. Время существования положительного уровня на выходе элемента И 15 определяет длительность импульса тактирования и зависит от величин задержек триггера II и элемента 14. После выдачи положительного импульса формирователь 7 сохраняет свое состояние

25

чином 17, режим работы которого определяется регистром 16 состояния (см. фиг. 4). Дешифратор кодовых слов 4 обычно реализуется с помощью ЗУ, на адресные с входы которого подается дешифрируемая комбинация двоичных сигналов (кодовое слово), а в выбираемые при этом ячейки ОЗУ предварительно (при задании значений кодовых слов) записывается указание на то, соответствует ли входная комбинация сиг- до прекращения входного сигнала на 0 налов заданной («1) или нет («О), синхровходах 6. Его выключение приводитВыходные сигналы блока 4 сравнения,

к тому, что на входах элемента 13 уста-которые появляются при обнаружении на вынавливаются различающиеся уровни, и воз-ходе буферного регистра 2 одного из заникающий при этом на ее выходе поло- данных в блоке 4 кодовых слов, подают- жительный сигнал поступает на переклю- 15 установку регистра 16 состояния чение триггера 11, который возвращается в блоке 5 управления. В зависимости от в нулевое состояние. Положительный сигнал с элемента 13 не может пройти на выход формирователя 7, так как при выключении тактирующего сигнала на синхровходах 6 входные уровни элемента 12 вырав-,20 ниваются и на ее выходе устанавливается нулевой потенциал. Этот потенциал подается на второй вход элемента И 15 и запрещает прохождение через нее каких- либо сигналов.

Таким образом, при заданном - выключенном - состоянии триггера 10 выходной тактовый импульс формирователя 7 формируется только при появлении положительного фронта входного сигнала. После

выключения триггера 11 формирователь зо ячейку со стиранием ранее записанных оказывается в исходном состоянии и готов данных. В этом режи.ме регистрация дан- к приему следующего тактового сигнала. ных фактически не производится (сохра- При тактировании отрицательным фрон- няется только последнее записанное слово том входного сигнала триггер 10 следует состояния).

установить в единичное состояние. При этомКак только в регистре 16 устанавлиформирователь работает аналогичным обра- 35 вается состояние, разрешающее счет такто- зом (правая сторона временной диаграммы вых импульсов счетчиком 17 (это происходит

при появлении соответствующих сигналов, либо по микропроцессорной шине ввода- вывода данных, либо с выходов блока 4), последний начинает работать и данные с

при включении (положительный фронт), 0 выхода буферного регистра 2 записываются а при выключении (отрицательный фронт)в последовательно адресуемые ячейки блока

внешнего сигнала тактирования по цепи 6. 3 памяти. Запись продолжается либо до Так как внутренние схемы, взаимные появления следующего сигнала запрета связи и порядок работы блока 3 па-счета в счетчике 17, либо до заполнения

мяти, блока 4 сравнения, блока 5 управ- всего объема памяти блока 3. В последнем

ления типичны для техники логических

анализаторов,их рассмотрение производится в общем и упрощенном виде.

Блок 3 памяти представляет собой оперативное ЗУ, в котором накапливается регистрируемая информация. Количество п слов данных (слов состояний), которое может быть записано в этот блок, определяет глубину регистрации анализатора. Разрядность слова состояния определяет возможное число каналов регистрации

установленных в регистре 16 признаков его сигналы разрешают или запрещают счет тактовых импульсов, которые поступают на вход счетчика 17 с элемента ИЛИ 8.

Выходы счетчика 17 подаются на адресные входы блока 3 памяти и определяют адрес ячейки, в которую производится запись при поступлении на блок 3 памяти импульса записи (такта) от элемента ИЛИ 8.

Если счет тактовых импульсов в счетчике 17 запрещен сигналами с регистра 16, запись данных с выхода буферного регистра 2 в блок 3 памяти при поступлении тактовых импульсов производится в одну и ту же

на фиг. 3), но инвертирование сигнала на одном из входов элемента 12 ведет к тому, что выходной тактирующий импульс формирователя 7 будет формироваться не

случае процесс регистрации в анализаторе заканчивается.

Формула изобретения

1. Логический анализатор, содержащий блок памяти, буферный регистр, блок сравнения и блок управления, причем группа информационных входов анализатора является первой группой информационных входов буферного регистра, группа выходов

(включая и служебные каналы). Такты за-55 которого соединена с первой группой инписи поступают на блок 3 памяти с выходаформационных входов блока сравнения и

элемента ИЛИ 8. Адрес ячейки, в которуюгруппой информационных входов блока папроизводится запись, устанавливается счет-мяти, выход равенства блока сравнения сое5

данных в блоке 4 кодовых слов, подают- 5 установку регистра 16 состояния в блоке 5 управления. В зависимости от 0

о ячейку со стиранием ранее записанных данных. В этом режи.ме регистрация дан- ных фактически не производится (сохра- няется только последнее записанное слово состояния).

установленных в регистре 16 признаков его сигналы разрешают или запрещают счет тактовых импульсов, которые поступают на вход счетчика 17 с элемента ИЛИ 8.

Выходы счетчика 17 подаются на адресные входы блока 3 памяти и определяют адрес ячейки, в которую производится запись при поступлении на блок 3 памяти импульса записи (такта) от элемента ИЛИ 8.

Если счет тактовых импульсов в счетчике 17 запрещен сигналами с регистра 16, запись данных с выхода буферного регистра 2 в блок 3 памяти при поступлении тактовых импульсов производится в одну и ту же

случае процесс регистрации в анализаторе заканчивается.

Формула изобретения

1. Логический анализатор, содержащий блок памяти, буферный регистр, блок. сравнения и блок управления, причем группа информационных входов анализатора является первой группой информационных входов буферного регистра, группа выходов

динен с входом разрешения запуска блока управления, группа выходов которого соединена с группой адресных входов блока памяти, синхровходы буферного регистра, блока управления и блока памяти объединены, вторая группа информационных входов блока сравнения является группой входов задания кодовых слов анализатора, группа входов задания начального адреса регистрации блока управления и вход управления записью/считыванием блока па- мяти являются соответствующими входами анализатора, отличающийся тем, что, с целью расширения функциональных возможностей анализатора за счет обеспечения анализа совокупности многотактных логических сигналов, он содержит дополнительно п формирователей импульсов по числу входных синхросигналов анализатора и элемент ИЛИ, причем информационные входы формирователей импульсов соединены с соответствую- ш,ими синхровходами анализатора, выходы формирователей импульсов соединены с вто

рой группой информационных входов буферного регистра и с входами элемента ИЛИ, выход которого соеднйен с синхровходом буферного регистра, входы задания активных фронтов синхросигналов формирователей импульсов являются соответствуюш,ими входами анализатора.

2. Анализатор по п. 1, отличающийся тем, что блок управления содержит регистр состояния и адресный счетчик, группы информационных входов параллельной записи регистра состояния и адресного счетчика объединены и образуют группу входов задания начального адреса регистрации блока, вход разрешения записи регистра состояния является соответствующим входом блока, синхровход адресного счетчика является синхровходом блока, группа разрядных выходов адресного счетчика является группой выходов блока, группа выходов регистра состояния подключена к группе разрешающих входов адресного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Логический анализатор | 1986 |

|

SU1381512A1 |

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Логический анализатор | 1989 |

|

SU1730627A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для сопряжения канала передачи данных с магистралью | 1986 |

|

SU1444787A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

Изобретение относится к вычислительной технике, в частности к средствам контроля и наладки сложных цифровых устройств и систем. Цель изобретения - расширение функциональных возможностей за счет анализа совокупности многотактовых логических сигналов. Анализатор содержит буферный регистр 2, блок 3 памяти, блок 4 сравнения, блок 5 управления, группу формирователей 7 импульсов, элемент ИЛИ 8. В анализаторе производится формирование признаков тактов и их запись в каналы регистрации. Число таких тактов регистрации не ограничено. 1 з. п. ф-лы, 4 ил. оо О5 СО tsD Фи2.1

Такт(отэл.

Составитель И. Сафронова

Редактор А. ДолиничТехред И. Верес . Корректор И. Муска

Заказ 5966/41Тираж 671Подписное

ВНИИПИ Государственного комитета СССР по де.пам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

У///Л/ //////////////, ///////////////Л

l ////////7A7// it

Е1

/

Щ

т

Фи&.

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4425643, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

Авторы

Даты

1987-12-30—Публикация

1986-01-09—Подача