Изобретение относится к вычислительной технике и может быть использовано в качестве многоканального, устройства ввода информации в устрой- ства обработки данных

Целью изобретения является расширение области применения за сГчет обеспечения возможности обработки f данных от групп датчиков с переменной длиной информационного сообщения.

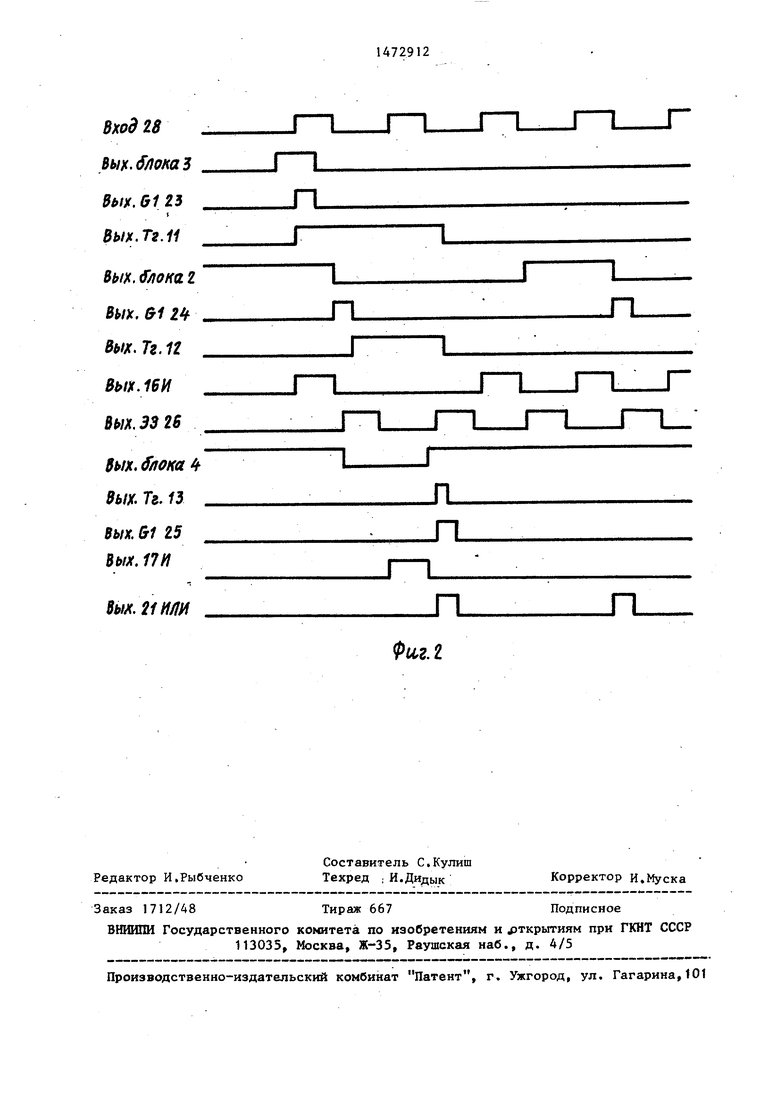

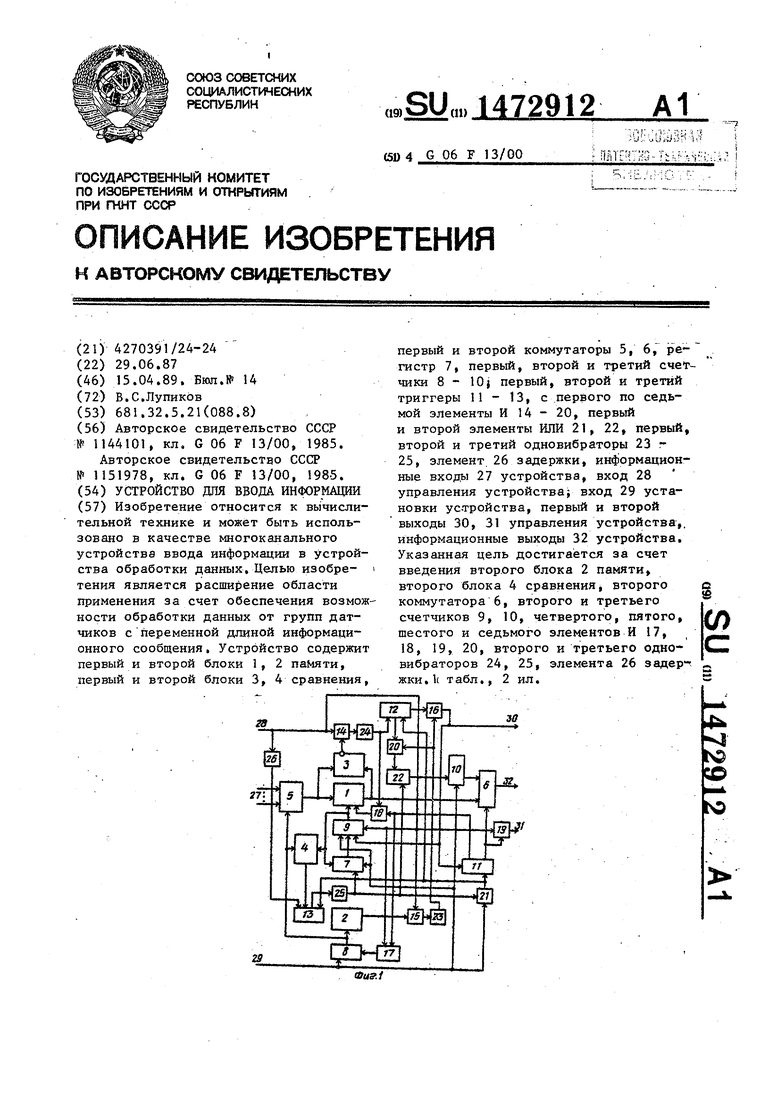

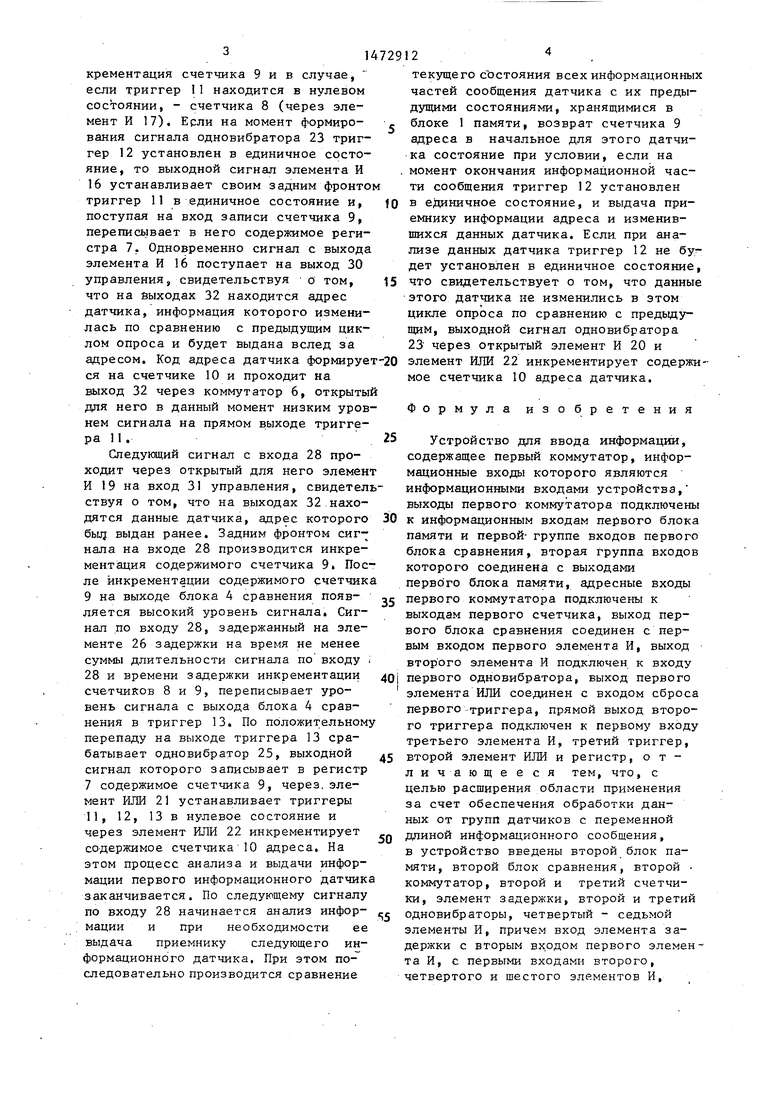

На фиг.1 приведена структурная схема устройства; на фиг. 2 - времен- ные диаграммы его работы.

Устройство содержит первый и вто- рой блоки 1 и 2 памяти, первый и второй блоки 3 и 4 сравнения, первый и второй коммутаторы 5 и 6, регистр 7, первый, второй и третий счетчики 8,

9и 10, первый, второй и третий трш геры II, 12 и 13 с первого по седьмой элементы И 14 - 20 первый и вто рой элементы ИЛИ 21, 22, первый, второй и третий одновибраторы 23,

24 и 25, элемент 26 задержки, инфор- мационные входы 27 устройства, вход 28 управления устройства, вход 29 установки устройства, первый и второ выходы 30 и 31 управления устройства, информационные выходы 32 устрой- ства.

Одним из возможных вариантов pea- лизации блока 2 памяти может быть постоянное запоминающее устройство.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 29 установки регистр 7, счетчики 8,9, 10 и триггеры И, 12, 13 устанавливаются в нулевое состояние. В одноразрядном блоке 2 памяти записаны сигналы, определяющие длины, информационных частей сообщения каждого информационного датчика, подключенного на вход коммутатора 5 (см. таблицу).

Из таблицы видно, что информационная часть сообщения датчика с адресом 000 занимает один вход коммутато ра 5, два входа для датчика с адресо 001, три входа для датчика с адресом

010и т.д.

Работу устройства рассмотрим на примере одного цикла опроса информа- ционных датчиков . В исходном состоянии устройства счетчики 8,9, 10, регистр 7, триггеры 11, 12, 13 находятся в нулевом состоянии, в блоке 1

памяти хранятся данные предыдущего цикла опроса датчиков, в блоке 2 памяти - управляющие биты информации о длинах информационных частей сообщений датчиков. Рассмотрим работу устройства на примере обработки данных первого датчика, информационная часть сообщения которого не превышает разрядности блока 1 памяти. До прихода первого синхросигнала в счетчике 8 хранится нулевое состояние, которое воздействуя на коммутатор 5, обеспечивает подключение сигналов с первого входа коммутатора 5 на вход блока 1 памяти и первый вход блока 3 сравнения, На второй вход блока 3 сравнения поступает считываемая из блока 1 , памяти информация о предыдущем состоянии сигнала, подключенного к первому входу коммутатора 5. Режим считывания для блока 1 памяти задается низким уровнем сигнала на выходе элемента И 18. С приходом первого синхросигнала по входу 28, свидетельствующего о возможности анализа данных датчика, подключенного к первому входу коммутатог ра 5, производится опрос элемента И | 14. Если в этот момент на выходе блока 3 сравнения присутствует высокий уровень сигнала что свидетель- ствует об отличии данных на входах блока 3 сравнения, сигнал с входа 28 проходит через элемент И 14 и своим передним фронтом запускает одновибра- тор 24, выходной сигнал которого, проходя через элемент И 18, обеспечивает запись в блок 1 памяти текущего состояния сигнала на первых входах коммутатора 5 в ячейку с адре- ,сом, сформированным на счетчике 9 (в данный момент с нулевым адресом). Одновременно выходной сигнал одновиб- ратора 24 устанавливает в единичное состояние триггер 12. Сигнал на входе 28 опрашивает также элемент И 15, на другой вход которого считывается из блока 2 памяти управляющий бит данных по адресу, сформированному на счетчике 8 (в данный момент по нулевому адресу). Если считывается из блока 2 памяти единичный бит данных, что свидетельствует об окончании информационной части сообщения датчика, выходной сигнал элемента И 15 по заднему фронту запускает бдновибратор - 23, выходной сигнал которого опрашивает элемент И 16. По заднему фронту сигнала на входе 28 прбизводитея «н314

крементация счетчика 9 и в случае, если триггер 11 находится в нулевом состоянии, - счетчика 8 (через элемент И 17), Если на момент формиро- вания сигнала одновибратора 23 триггер 12 установлен в единичное состояние, то выходной сигнал элемента И 16 устанавливает своим задним фронтом триггер 11 в единичное состояние и, поступая на вход записи счетчика 9, переписывает в него содержимое регистра 7. Одновременно сигнал с выхода элемента И 16 поступает на выход 30 управления, свидетельствуя о том, что на выходах 32 находится адрес датчика, информация которого изменилась по сравнению с предыдущим циклом опроса и будет выдана вслед за адресом. Код адреса датчика формирует ся на счетчике 10 и проходит на выход 32 через коммутатор 6, открытый для него в данный момент низким уровнем сигнала на прямом выходе триггера 11 .

Следующий сигнал с входа 28 проходит через открытый для него элемент И 19 на вход 31 управления, свидетельствуя о том, что на выходах 32 находятся данные датчика, адрес которого был выдан ранее. Задним фронтом сигнала на входе 28 производится инкремент ация содержимого счетчика 9 После инкрементации содержимого счетчика 9 на выходе блока 4 сравнения появ- ляется высокий уровень сигнала. Сигнал по входу 28, задержанный на элементе 26 задержки на время не менее суммы длительности сигнала по входу . 28 и времени задержки инкрементации счетчиков 8 и 9, переписывает уро- вень сигнала с выхода блока 4 сравнения в триггер 13. По положительному перепаду на выходе триггера 13 срабатывает одновибратор 25, выходной сигнал которого записывает в регистр 7 содержимое счетчика 9, через элемент ИЛИ 21 устанавливает триггеры 11, 12, 13 в нулевое состояние и через элемент ИЛИ 22 инкрементирует содержимое счетчика 10 адреса. На этом процесс анализа и выдачи информации первого информационного датчика заканчивается. По следующему сигналу по входу 28 начинается анализ инфор- мации и при необходимости ее выдача приемнику следующего информационного датчика. При этом последовательно производится сравнение

124

текущего состояния всех информационных частей сообщения датчика с их предыдущими состояниями, хранящимися в блоке 1 памяти, возврат счетчика 9 адреса в начальное для этого датчика состояние при условии, если на момент окончания информационной части сообщения триггер 12 установлен в единичное состояние, и выдача приемнику информации адреса и изменившихся данных датчика. Если, при анализе данных датчика триггер 12 не будет установлен в единичное состояние, что свидетельствует о том, что данные этого датчика не изменились в этом цикле опроса по сравнению с предыдущим, выходной сигнал одновибратора 23 через открытый элемент И 20 и элемент ИЛИ 22 инкрементирует содержимое счетчика 10 адреса датчика.

Формула изобретения

Устройство для ввода информации, содержащее первый коммутатор, информационные входы которого являются информационными входами устройства, выходы первого коммутатора подключены к информационным входам первого блока памяти и первой- группе входов первого блока сравнения, вторая группа входов которого соединена с выходами первого блока памяти, адресные входы первого коммутатора подключены к выходам первого счетчика, выход первого блока сравнения соединен с первым входом первого элемента И, выход второго элемента И подключен к входу первого одновибратора, выход первого элемента ИЛИ соединен с входом сброса первого триггера, прямой выход второго триггера подключен к первому входу третьего элемента И, третий триггер, второй элемент ИЛИ и регистр, о т - личающе е ся тем, что, с целью расширения области применения за счет обеспечения обработки данных от групп датчиков с переменной длиной информационного сообщения, в устройство введены второй блок памяти, второй блок сравнения, второй коммутатор, второй и третий счетчики, элемент задержки, второй и третий одновибраторы, четвертый - седьмой элементы И, причем вход элемента задержки с вторым входом первого элемента И, с первыми входами второго, четвертого и шестого элементов И,

514

счетным входом второго счетчика и является входом управления устройства, -выходы второго счетчика подключены к адресным входам первого блока памяти, к первой группе входов второго блока сравнения и к информационным входам регистра, выходы которого соединены с информационными входами второго счетчика, вход записи кото- рого подключен к входу установки первого триггера, к выходу третьего элемента И и является первым выходом управления устройства, вход сброса первого счетчика соединен с входами сброса второго и третьего счетчиков, с входом сброса регистра, с первым входом первого элемента ИЛИ и является входом установки устройства, второй вход первого элемента ИЛИ подключен к первому входу второго элемента ИЛИ, к входу записи регистра и к выходу третьего одновибратора, вход которого соединен с прямым выходом третьего триггера, вход сброса которого подключен к выходу первого элемента ИЛИ и к входу сброса второго триггера, вход установки которого доединен с выходом второго одновибратора и с первым входом пятого элемента И, чвторой вход которого подключен к инверсному выходу первого триггера и к второму входу четвертого элемента И, выход которого соединен со счетным входом первого счетчика,

126

выходы которого подключены к адресным входам второго блока памяти и второй группе входов второго блока сравнения, выход второго блока памяти соединен с вторым входом второго элемента И, вход второго одновибратора соединен с выходом первого элемента И, выход элемента задержки подключен к синхровходу третьего триггера, информационный вход которого соединен с выходом второго блока сравнения, прямой выход первого триггера подключен к второму входу шестого элемента И и к адресному входу второго коммутатора, информационные входы первой и второй групп которого соединены соответственно с выходами первого блока памяти и третьего счетчика, счетный вход которого под- ключей к выходу второго элемента ИЛИ, второй вход которого соединен с выходом седьмого элемента И, первый вход которого подключен к второму входу третьего элемента И и к выходу первого одновибратора, второй вход седьмого элемента И соединен с инверсным выходом второго триггера, выход пятого элемента И подключен к входу записи-чтения первого блока памяти, выходы второго коммутатора являются информационными выходами устройства, выход шестого элемента И является вторым выходом управления устройства.

J1

П

п

ГТ

П

П

П

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1987 |

|

SU1442999A2 |

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1287236A1 |

| Устройство для контроля качества проводного монтажа | 1983 |

|

SU1108466A1 |

| Устройство для сопряжения N абонентов с М ЭВМ | 1988 |

|

SU1564635A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1376091A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Устройство для ввода информации | 1985 |

|

SU1290337A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

Изобретение относится к вычислительной технике и может быть использовано в качестве многоканального устройства ввода информации в устройства обработки данных. Целью изобретения является расширение области применения за счет обеспечения возможности обработки данных от групп датчиков с переменной длиной информационного сообщения. Устройство содержит первый и второй блоки 1, 2 памяти, первый и второй блоки 3, 4 сравнения, первый и второй коммутаторы 5, 6, регистр 7, первый,второй и третий счетчики 8 - 10, первый, второй и третий триггеры 11 - 13, с первого по седьмой элементы И, 14 -20, первый и второй элементы ИЛИ, 21, 22, первый ,второй и третий одновибраторы 23 - 25, элемент 26 задержки, информационные входы 27 устройства, вход 28 управления устройства, вход 29 установки устройства, первый и второй выходы 30,31 управления устройства, информационные выходы 32 устройства. Указанная цель достигается за счет введения второго блока 2 памяти, второго блока 4 сравнения, второго коммутатора 6, второго и третьего счетчиков 9, 10, четвертого, пятого, шестого и седьмого элементов И, 17,18,19,20 второго и третьего одновибраторов 24, 25, элемента 26 задержки. 1 табл., 2 ил.

Фи,г.2

| Устройство для ввода информации | 1983 |

|

SU1144101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1983 |

|

SU1151978A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-15—Публикация

1987-06-29—Подача