Изобретение относится к вычислительной технике и может быть использовано для сопряжения двух раз- носкоростных устройств в многоканальных системах сбора, регистрации и обработки информации.

Цель изобретения - повьшшние достоверности работы устройства за счет исключения потерь информации.

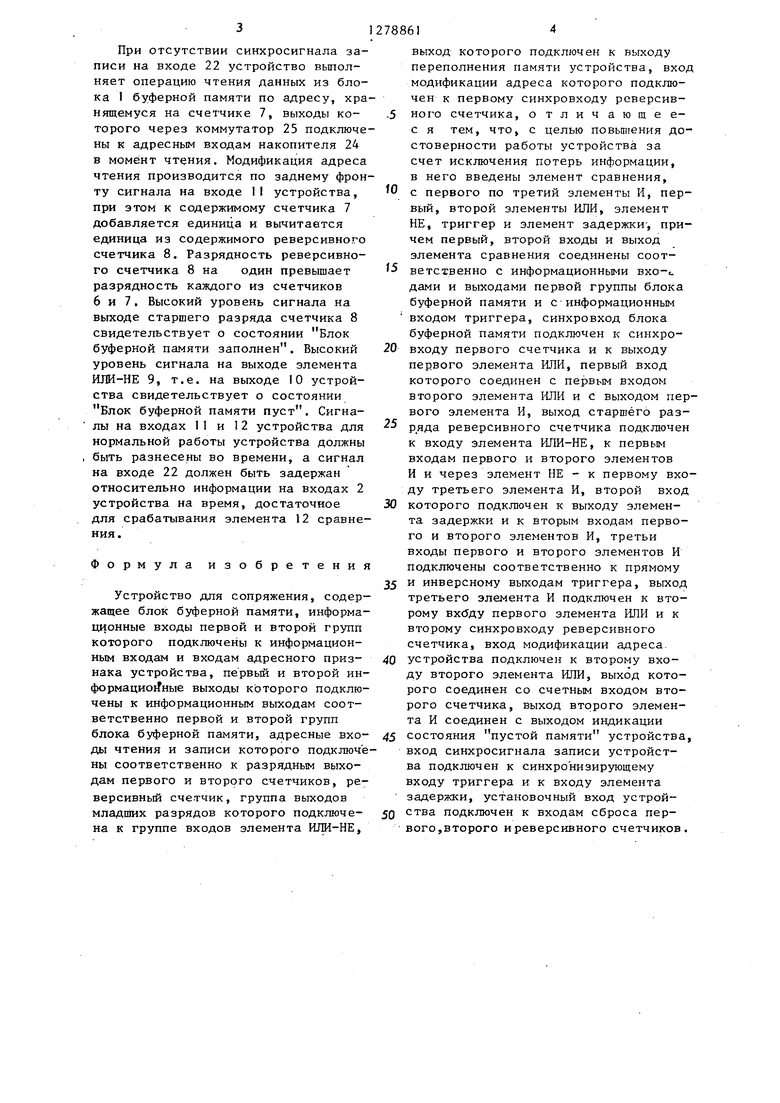

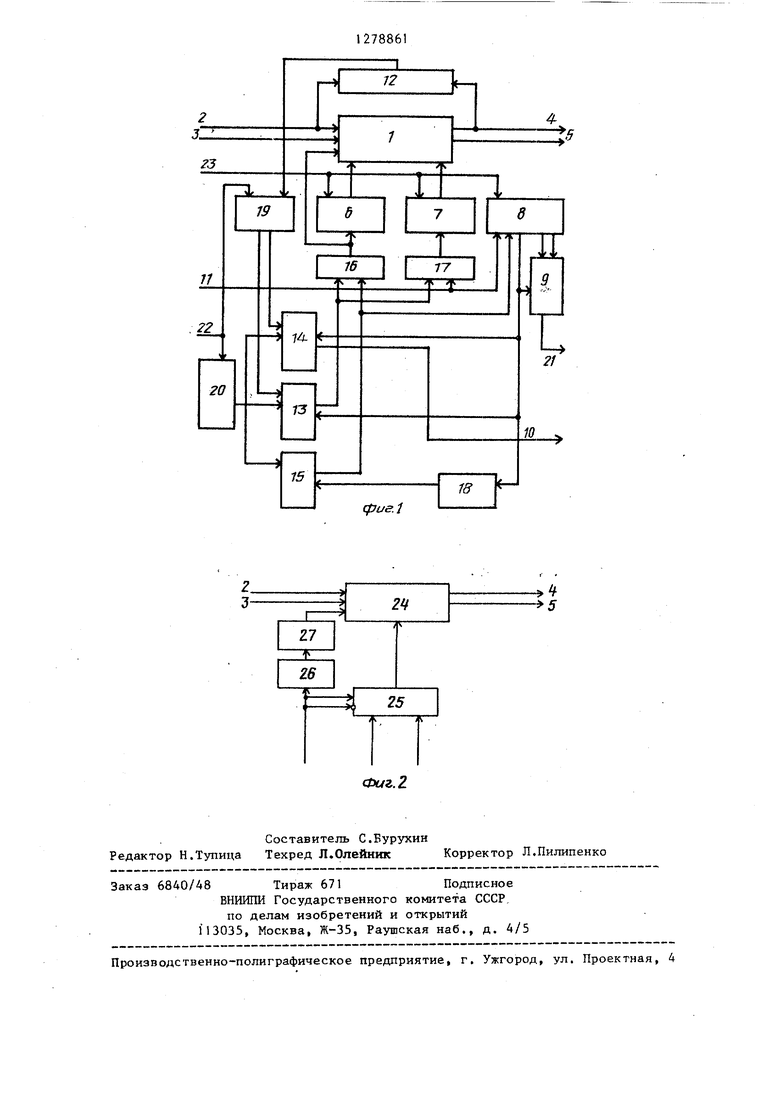

На фиг. 1 приведена структурная схема устройства для сопряжения;на фиг. 2 - структурная схема блока буферной памяти.

Устройство содержит блок 1 буфер- ной памяти с информационньши входами первой 2 и второй 3 групп и информационными выходами первой 4 и второй 5 групп, первый счетчик 6, второй счетчик 7, реверсивный счетчик 8, элемент ИЛИ-НЕ 9, выход 10

индикации состояния пустой памяти устройства, вход 11 модификации адреса устройства, элемент 12 сравнения, первый 13, второй 14 и третий- 15 элементы И, первый 16 и второй 17 элементы ИЛИ, элемент НЕ 18, триггер 19, элемент 20 задержки, выход 21 переполнения памяти устройства, вход 22 синхросигнала записи устройства, установочный вход 23 устройст- на.

Блок 1 буферной памяти (фиг. 2) содержит накопитель 24, коммутатор 25, элемент 26 задержки и формирователь 27.

Устройство работает следующим образом.

Перед началом работы сигналом по входу 23 устройства счетчики 6-8 ус- танавливак1тся в нулевое состояние.

В режиме записи на входы 3 устройства поступают данные измерительного канала в совопровождении его адресного признака на входах 2 устройства и синхросигнала записи на вход 22. Задержанный на элементе 20 задержки синхросигнал записи поступае на входы элементов И 13-15. Величин задержки сигнала на элементе 20 задержки должна быть больше времени здержки на триггере 19.

При незаполненном блоке 1 буферно памяти на выходе старшего разряда реверсивного счетчика 8 присутствуе низкий уровень сигнала, который че- рез элемент НЕ 1 В разрешает прохождние синхросигнала записи через элемент И 15, элемент ИЛИ 16 на синхро

5

0

0

5

0

5

0

вход счетчика 6 и на управляющий вход блока 1 буферной памяти. Этот сигнал, воздействуя на прямой и инверсный входы управления коммутатора 25, подключает к адресным входам накопителя 24 разрядные выходы счетчика 6, проходит элемент 26 задержки на вход формирователя 27, который формирует сигнал записи данных в накопитель 24 по адресу, хранящемуся на счетчике 6. По заднему фронту синхросигнала счетчик 6 и реверсивный счетчик 8 модифицируются, т.е. к их содержимому добавляется единица.

При заполненном блоке 1 буферной памяти по переднему фронту синхросигнала записи производится запись в триггер 19 выходного сигнала элемента 12 сравнения. На выходе элемента 12 сравнения присутствует высокий уровень сигнала, если код адресного признака информации, присутствующий на входах 2 устройства, больше кода адресного признака информации на выходах 4 устройства. Б противном случае на выходе элемента 12 сравнения присутствует низкий уровень сигнала. При условии записи в триггер 19 высокого уровня сигнала на его прямом выходе также будет высокий уровень сигнала, который вместе с высоким уровнем сигнала на выходе старшего разряда реверсивного счетчика 8 разрешает прохождение синхросигнала записи через элемент И 13 на входы элемента ИЛИ 16 и элемента ИЛИ 17, с выходов которых Сигналы поступают на синхровходы счетчиков 6 и 7 соответственно, а также

на вход управления блока 1 буферной памяти. Сигнал на входе блока 1 буферной памяти обеспечивает запись данных в накопитель 24 по адресу, хранящемуся на выходах счетчика 6. По окончании записи задним фронтом синхросигнала производится модификация счетчиков 6 и 7, т.е. к их содержимому добавляется единица. В случае присутствия высокого уровня сигнала на инверсном выходе триггера 19 При наличии высокого уровня сигнала на выходе старшего разряда реверсивного счетчика 8 синхросигнал залиси через элемент И 14 поступает на выход 21 переполнения памяти устройства, свидетельствуя о невозможности записи данных в блок 1 буферной памяти.

При отсутствии синхросигнала записи на входе 22 устройство вьтол- няет операцию чтения данных из блока 1 буферной памяти по адресу, хранящемуся на счетчике 7, выходы которого через коммутатор 25 подключены к адресным входам накопителя 24 в момент чтения. Модификация адреса чтения производится по заднему фронту сигнала на входе II устройства, при этом к содержимому счетчика 7 добавляется единица и вычитается единица из содержимого реверсивного счетчика 8. Разрядность реверсивного счетчика 8 на один превышает разрядность каждого из счетчиков 6 и 7. Высокий уровень сигнала на выходе старшего разряда счетчика 8 свидетельствует о состоянии Блок буферной памяти заполнен. Высокий уровень сигнала на выходе элемента ИЛИ-НЕ 9, т.е. на выходе 10 устройства свидетельствует о состоянии БЛОК буферной памяти пуст. Сигналы на входах I1 и 12 устройства для нормальной работы устройства должны быть разнесены во времени, а сигнал на входе 22 должен быть задержан относительно информации на входах 2 устройства на время, достаточное для срабатывания элемента 12 сравнения.

Формула изобретения

Устройство для сопряжения, содержащее блок буферной памяти, информационные входы первой и второй групп которого подключены к информационным входам и входам адресного признака устройства, пе рвьй и второй ин- формацио Гные выходы которого подключены к информационным выходам соответственно первой и второй групп блока буферной памяти, адресные входы чтения и записи которого подключены соответственно к разрядным выходам первого и второго счетчиков, реверсивный счетчик, группа выходов младщих разрядов которого подключена к группе входов элемента ИПИ-НЕ,

788614

вьгход которого подключен к выходу переполнения памяти устройства, вход модификации адреса которого подключен к первому синхровходу реверсив.5 ного счетчика, отличающее- с я тем, что, с целью повьапения достоверности работы устройства за счет исключения потерь информации, в него введены элемент сравнения,

0 с первого по третий элементы И, первый, второй элементы ИЛИ, элемент НЕ, триггер и элемент задержки-, причем первый, второй входы и выход элемента сравнения соединены соот 5 ветственно с информационными вхо-.. дами и выходами первой группы блока буферной памяти и с информационным входом триггера, синхровход блока буферной памяти подключен к синхро20 входу первого счетчика и к выходу первого элемента ИЛИ, первый вход которого соединен с первым входом второго элемента ИЛИ и с выходом первого элемента И, выход старшего раз25 ряда реверсивного счетчика подключен к входу элемента ИЛИ-НЕ, к первым входам первого и второго элементов И и через элемент НЕ - к первому входу третьего элемента И, второй вход

30 которого подключен к выходу элемента задержки и к вторым входам первого и второго элементов И, третьи входы первого и второго элементов И подключены соответственно к прямому

35 и инверсному выходам триггера, вькод третьего элемента И подключен к второму вхбду первого элемента ИЛИ и к второму синхровходу реверсивного счетчика, вход модификации адреса.

40 устройства подключен к второму входу второго элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, выход второго элемента И соединен с выходом индикации

45 состояния пустой памяти устройства, вход синхросигнала записи устройства подключен к синхронизирующему входу триггера и к входу элемента задержки, установочный вход устрой50 ства подключен к входам сброса первого,второго и реверсивного счетчиков.

Составитель С.Бурухин Редактор Н.Тупица Техред Л.Олейник Корректор Л.Пилипенко

Заказ 6840/48 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР.

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1381530A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1236550A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Буферное запоминающее устройство для блоков отображения информации | 1986 |

|

SU1411830A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1495851A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1278979A2 |

| Устройство для сопряжения источника и приемника информации | 1986 |

|

SU1416988A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве устройства для сопряжения в многоканальных системах сбора, регистрации и обработки информации. Целью изобретения является повьпиение надежности в работе устройства. Устройство содержит блок буферной памяти, первый, второй счетчики, реверсивный счетчик, элемент ИЛИ-НЕ, элемент сравнения, с первого по третий элементы И, первый, второй элементы ИДИ, элемент НЕ, триггер элемент задержки. Устройство при заполнении буферной памяти и при поступлении запроса на запись производит сравнение ценности поступившей и первой подлежащей чтению информации и в зависимости от результата сравнения производит (или не производит) запись поступивших данных в блок памяти устройства для сопряжения. Таким образом в моменты переполнения устройства теряется мен/ пенная информация. -2 ил. § (Л ND 00 00 О)

| Устройство для обмена информацией | 1973 |

|

SU496551A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1979 |

|

SU881722A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-26—Подача