Изобретение относится к вычислительной технике и может быть использоЕ ано при построении буферных запоминающих устройств (БЗУ) в системах сбора и обработки измерительной информации.

Цель изобретения - повышение информационной емкости устройства.

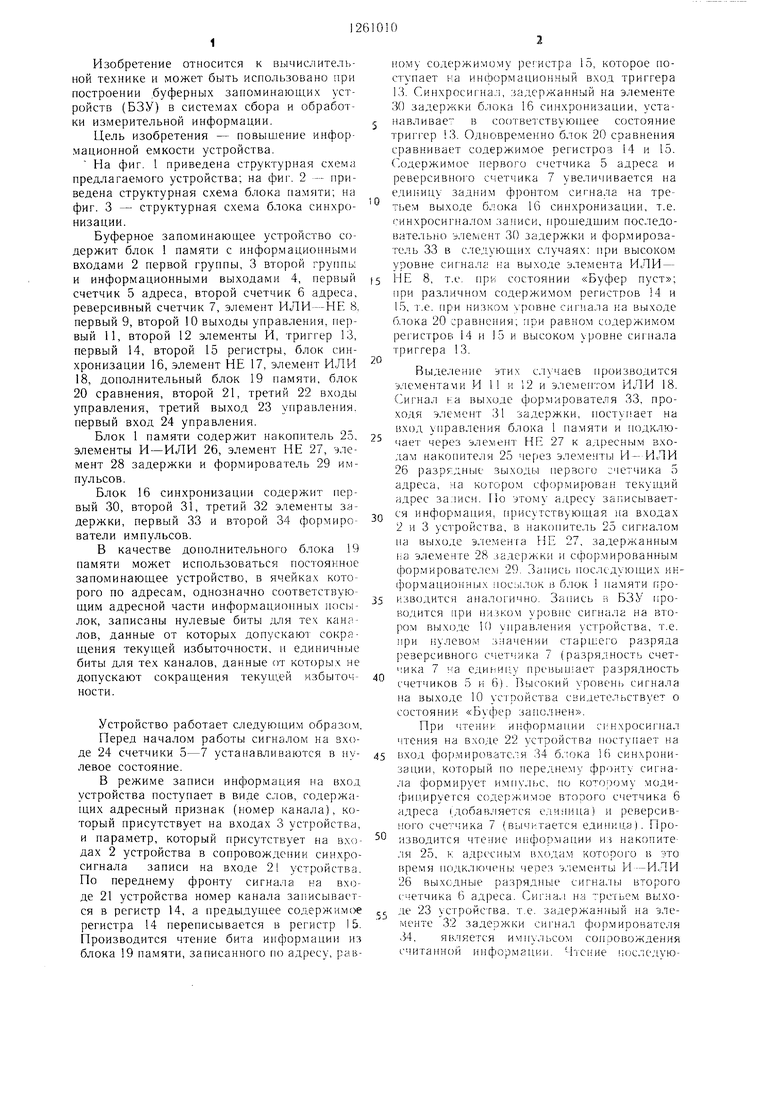

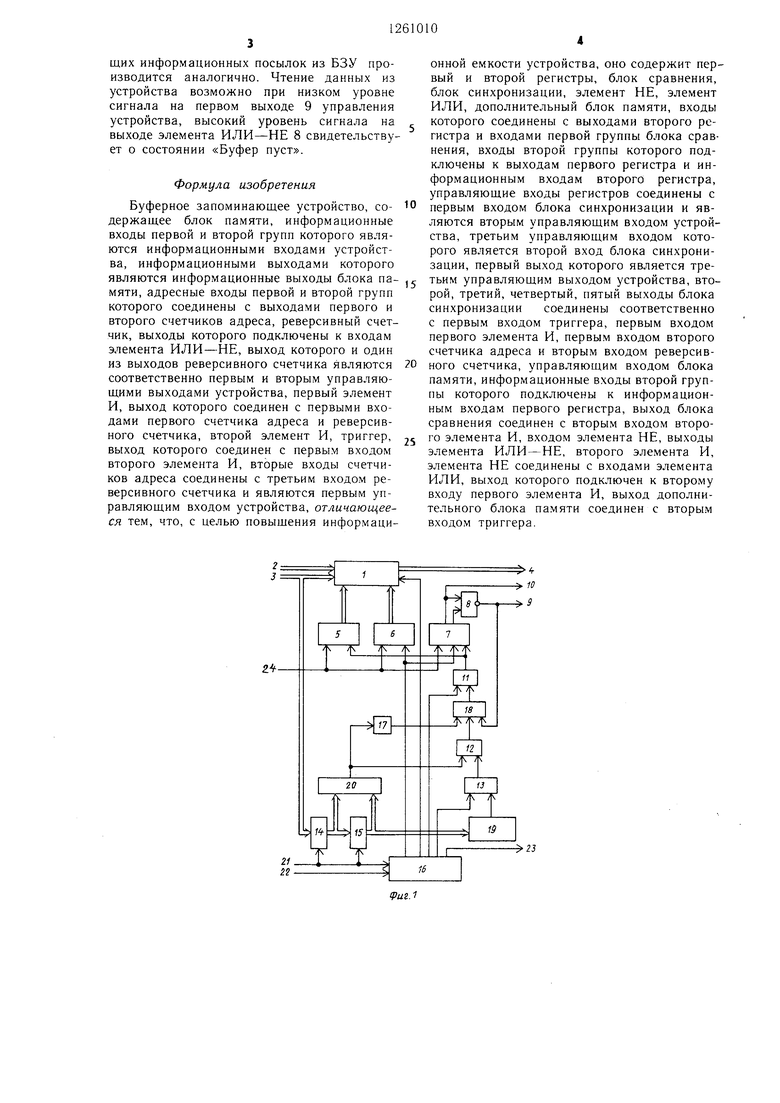

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - приведена структурная схема блока памяти; на фиг. 3 - структурная схема блока синхронизации.

Буферное запоминающее устройство содержит блок памяти с информационными входами 2 первой группы, 3 второй группы и информационными выходами 4, первый счетчик 5 адреса, второй счетчик 6 адреса, реверсивный счетчик 7, элемент ИЛИ --НЕ: 8, первый 9, второй 0 выходы управления, первый 11, второй 12 элементы И, триггер 13, первый 14, второй 15 регистры, блок синхронизации 16, элемент НЕ 17, элемент ИЛИ 18, дополнительный блок 19 памяти, блок 20 сравнения, второй 21, третий 22 входы управления, третий выход 23 управления. первый вход 24 управления.

Блок 1 памяти содержит накопитель 25, элементы И-ИЛИ 26, элемент НЕ 27, элемент 28 задержки и формирователь 29 импульсов.

Блок 16 синхронизации содержит первый 30, второй 31, третий 32 элементы задержки, первый 33 и второй 34 формирователи импульсов.

В качестве дополнительного блока 19 памяти может использоваться постоянное запоминающее устройство, в ячейках которого по адресам, однозначно соответствующим адресной части информационных посылок, записаны нулевые биты для тех каналов, данные от которых допускают сокращения текущей избыточности, п единичные биты для тех каналов, данные от которых не допускают сокращения текущей избыточности.

Устройство работает следуюп.1им образом.

Перед началом работы сигналом на входе 24 счетчики 5-7 устанавливаются в нулевое состояние.

В режиме записи информация на вход устройства поступает в виде слов, содержащих адресный признак (номер канала), который присутствует на входах 3 устройства, и параметр, который присутствует на входах 2 устройства в сопровождении синхросигнала записи на входе 21 устройства. По переднему фронту сигнала на входе 21 устройства номер канала записывается в регистр 14, а федыдущее содержимое регистра 14 переписывается в регистр 15. Производится чтение бита информации из блока 19 памяти,записанного но адресу, рав

5

0

5

5

0

содержимому регистра 15, которое поступает на информационный вход триггера 13. Синхросигнал, задержанный на элементе 30 задержки блока 16 синхронизации, уста- навливае™ в соответствующее состояние трипчф S3. Одновременно блок 20 сравнения сравнивает содержимое регистров 14 и 15. (.одержимое первого счетчика 5 адреса и реверсивного счетчика 7 увеличивается на единицу задним фронтом сигнала на третьем выходе 6jiOKa 16 син.хронизации, т.е. синхросигнало.м записи, нрошедщим последовательно эле.мснт 30 задержки и формирователь 33 в следующих случаях: при высоком уровне сигнала на выходе элемента ИЛИ - НЕ 8, т.е. при состоянии «Буфер фи различном содержимом регистров 14 и 15, т.е. при низком ч ровне сигнала на выходе Г)лока 20 сравнения; при равном содержимом регистров 14 и 15 и высоком уровне сигнала триггера 13.

Выделение УТИХ с, 1 чаев производится элементами И 11 и 2 и э;1емептом ИЛИ 18. (Сигнал на выходе формирователя 33, проходя элемент 31 задержки, поступает на вход у|фавления блока 1 памяти и подключает через элемент FiH 27 к адресным входам накопителя 25 через элеме.чты И- ИЛИ 26 разрядные зыходы первого счетчика 5 адреса, ма когором с4)ормирован текущий адрес за лиси. Ио этому адресу записывается информация, присутствующая на входах 2 и 3 устройства, в накопитель 25 сигналом па выходе элемента НЕ 27, задержанным iia элементе 28 задержки и сформированным формирователем 29. последх ющих ий- (|юрмациоиных iiociJ. ioK л блок 1 памяти про- извс дится аналогично. Запись н БЗУ lipo- водится 1ри низком уровне сигнала на втором выходе И) управ;1ения устройства, т.е. 1ФИ 1 улсвол .значении старшего разряда реверсивного счетчика 7 (разрядность счетчика 7 на единицу прсвып ает разрядность счетчиков 5 и ()). Высокий vpoBCHfj сигнала па выходе 10 устройства свидетельствует о состоянии «Еэуфер заполнен.

При 1 тени{- информап.ии С :нхроси1иал чтения на входе 22 устройства поступает на вход фо 1мироватс;;я 34 блока К) синхронизации, К(ггорый по иередне.му фро;1ту сигнала формирует импульс, по ко орому модифицируется содержимое второго счетчика 6 адреса (добавляется е.чипица) и реверсивного счетчика 7 (вычитается едипица). Производится чтение информации из накопите- .ля 25, к адресным входам которого в это время 11одк;|1очеиь через э, ;смснты И-ИЛИ 26 выходные разрядные сигна;1ы второго счетчика 6 адреса. Си1 иал на трсльем выходе 23 устройства, л .е. задержанный на элементе 32 задержки сигнал формирователя 34. является импульсом сопровождения считанной ипс|:1Ормации. последую

щих информационных посылок из БЗУ производится аналогично. Чтение данных из устройства возможно при низком уровне сигнала на первом выходе 9 управления устройства, высокий уровень сигнала на выходе элемента ИЛИ-НЕ 8 свидетельствует о состоянии «Буфер пуст.

Формула изобретения

Буферное запоминающее устройство, содержащее блок памяти, информационные входы первой и второй групп которого являются информационными входами устройства, информационными выходами которого являются информационные выходы блока па- мяти, адресные входы первой и второй групп которого соединены с выходами первого и второго счетчиков адреса, реверсивный счетчик, выходы которого подключены к входам элемента ИЛИ-НЕ, выход которого и один из выходов реверсивного счетчика являются соответственно первым и вторым управляющими выходами устройства, первый элемент И, выход которого соединен с первыми входами первого счетчика адреса и реверсивного счетчика, второй элемент И, триггер, выход которого соединен с первым входом второго элемента И, вторые входы счетчиков адреса соединены с третьим входом реверсивного счетчика и являются первым управляющим входом устройства, отличающееся тем, что, с целью повыщения информаци

0

5

онной емкости устройства, оно содержит первый и второй регистры, блок сравнения, блок синхронизации, элемент НЕ, элемент ИЛИ, дополнительный блок памяти, входы которого соединены с выходами второго регистра и входами первой группы блока сравнения, входы второй группы которого подключены к выходам первого регистра и информационным входам второго регистра, управляющие входы регистров соединены с первым входом блока синхронизации и являются вторым управляющим входом устройства, третьим управляющим входом которого является второй вход блока синхронизации, первый выход которого является третьим управляющим выходом устройства, второй, третий, четвертый, пятый выходы блока синхронизации соединены соответственно с первым входом триггера, первым входом первого элемента И, первым входом второго счетчика адреса и вторым входом реверсивного счетчика, управляющим входом блока памяти, информационные входы второй группы которого подключены к информационным входам первого регистра, выход блока сравнения соединен с вторым входом второго элемента И, входом элемента НЕ, выходы элемента ИЛИ-НЕ, второго элемента И, элемента НЕ соединены с входами элемента ИЛИ, выход которого подключен к второму в.ходу первого элемента И, выход дополнительного блока памяти соединен с вторым входом триггера.

VU2.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1295451A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1672527A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1249583A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163357A1 |

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1257704A1 |

| Устройство для сортировки информации | 1987 |

|

SU1478210A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1455363A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

Изобретение может быть использовано для согласования по скорости передачи при вводе данных от источников многоканальной измерительной информации в систему сбора и обработки информации. Сущность изобретения состоит в повышении информационной емкости устройства за счет обеспечения возможности уменьшать текущую избыточность данных некоторых измерительных каналов. Адресная часть (номер канала) каждой информационной посылки сравнивается с аналогичной частью предыдущей посылки и, в случае их равенства, производится обращение к дополнительному блоку памяти по адресу, равному адресной части информационной посылки. При чтении из дополнительного блока памяти нулевого бита данных производится запись параметра в основной блок памяти без модификации адреса обращения. 3 ил. ГС 05

| Буферное запоминающее устройство | 1979 |

|

SU822293A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163359A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-09-30—Публикация

1985-03-15—Подача