Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов и работающих в реальном масштабе времени.

Цель изобретения - уменьшение аппаратурных затрат.

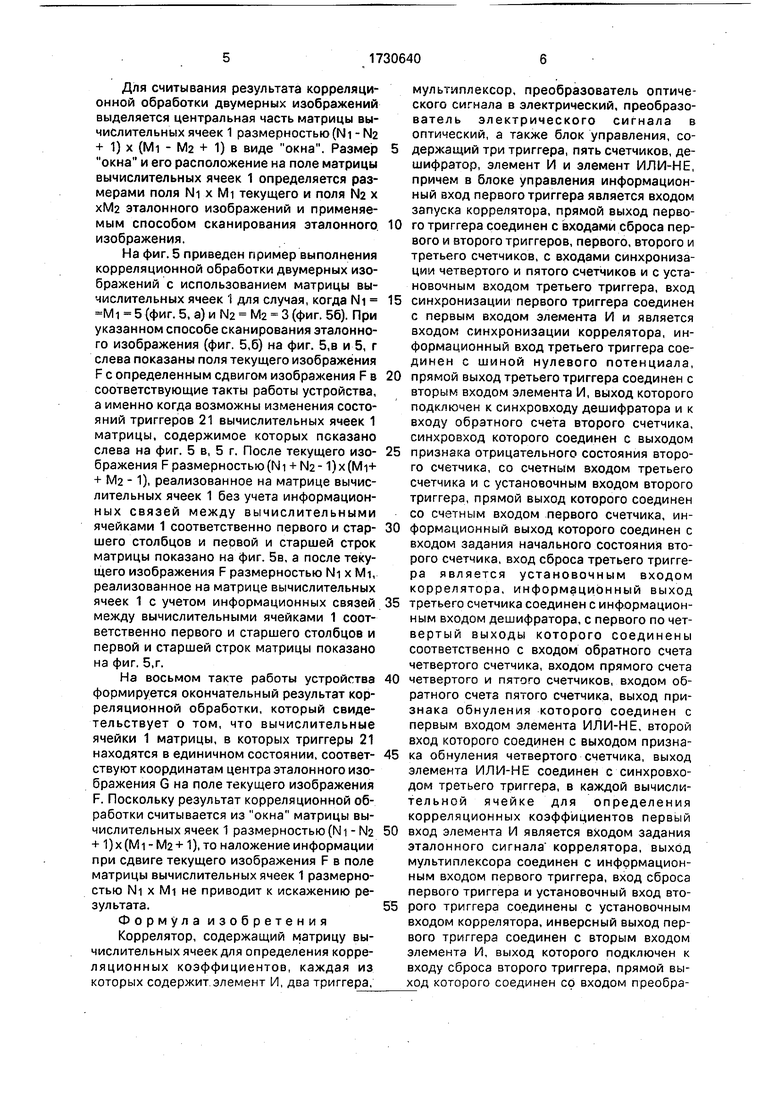

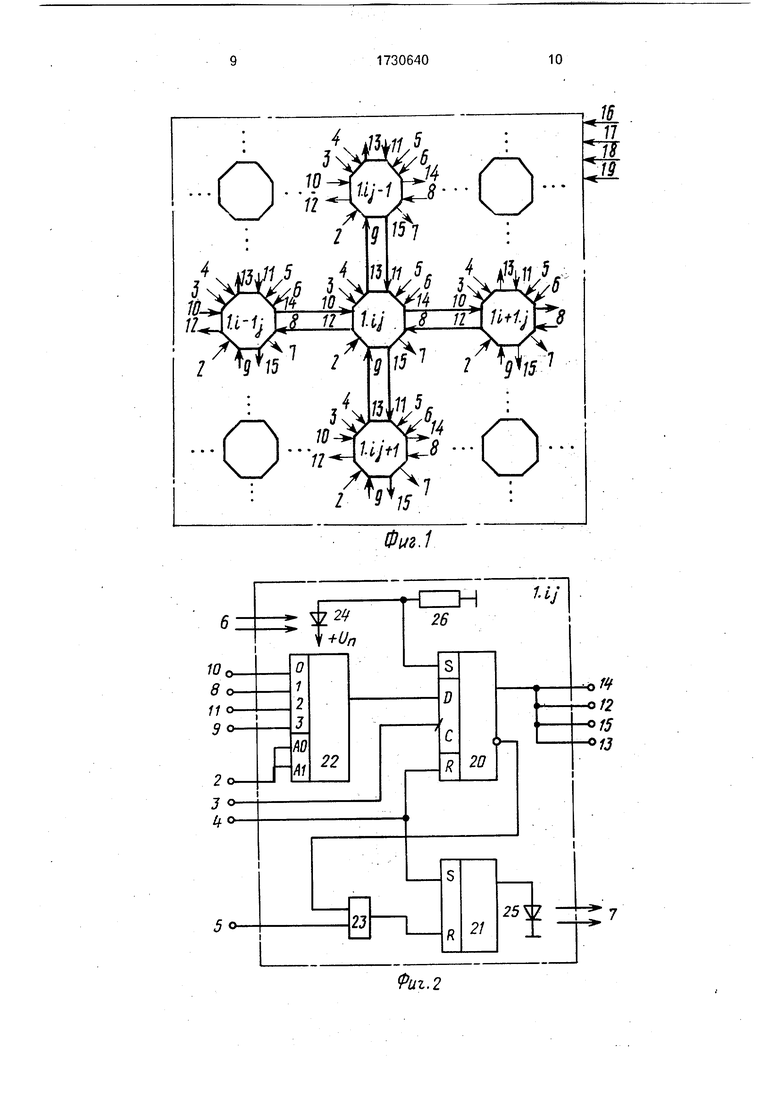

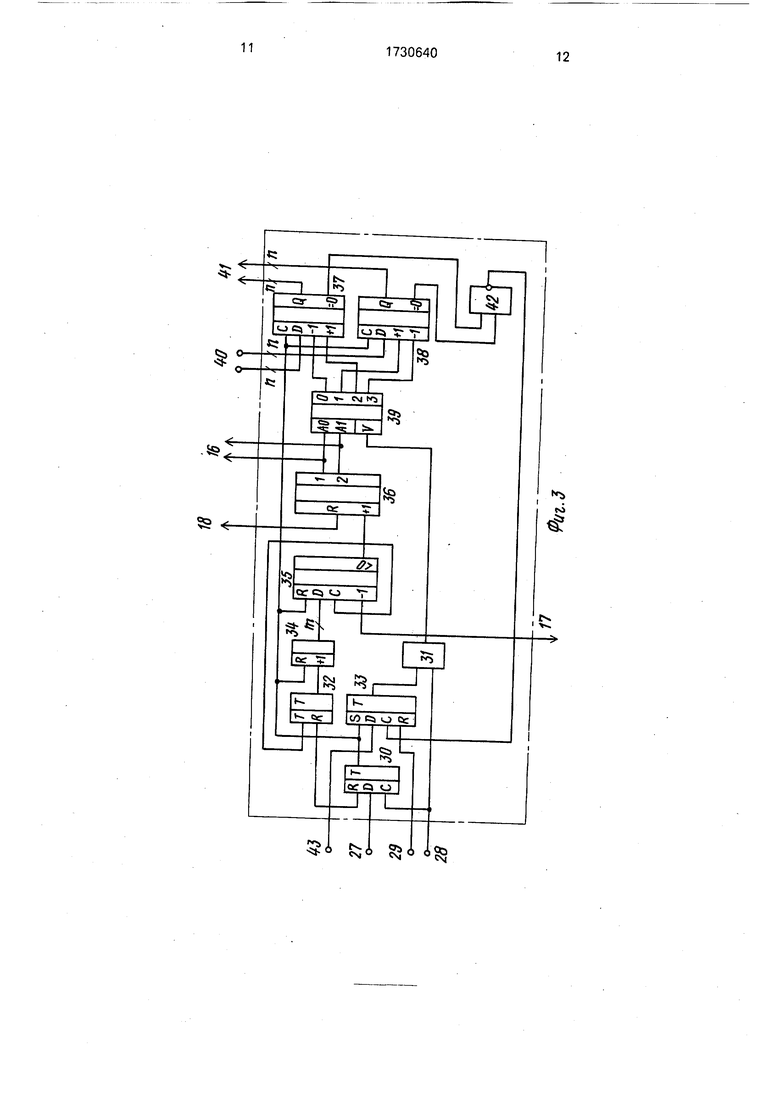

На фиг. 1 представлена структурная схема коррелятора; на фиг, 2 - схема вычисли- тельной ячейки для определения корреляционных коэффициентов; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - графическое представление матрицы вычислительных ячеек для определения корреляционных коэффициентов; на фиг. 5 - примеры корреляционной обработки изображений.

Коррелятор (фиг. 1) содержит матрицу из вычислительных ячеек 1J.J для определения корреляционных коэффициентов (1 1,

2,..., Ni; Wi- номер столбца; j 1,2Mi),

Mi - номер стрски , каждая из которых имеет адресные входь: 2, синхровход 3, входы 4 начальной установки, вход 5 эталонного сигнала, оптический вход 6, оптический выход 7, информационные входы 8-11, информационные выходы 12-15, управляющие шины 16-18, вход 19 эталонного сигнала.

Каждая вычислительная ячейка 1 (фиг. 2) содержит триггеры 20, 21, мультиплексор 22, элемент И 23, преобразователь оптического сигнала в электрический, выполненный в виде фотодиода 24, преобразователь электрического сигнала в оптический, выполненный в виде светодиода 25 резистор 26.

Блок управления (фиг. 3) содержит вход 27 запуска, вход 28 синхронизации, вход 29 начальной установки, первый триггер 30, элемент И 31, второй 32 и третий 33 триггеры, с первого по пятый счетчики 34-38, деVI

GJ О О

4

О

шифратор 39, вход 40 задания начальных координат эталонного изображения,адресный выход 41 выбора координат эталонного изображения, элемент ИЛИ-НЕ 42, вход 43 шины нулевого потенциала.

Работа коррелятора заключается в следующем.

Коррелятор определяет местонахождение двумерного эталонного изображения G {gki} на поле двумерного текущего изо-

бражения F {fij}, где i 1, 2N1; j 1, 2,

..., Mi; k 1, 2 N2; 1 1,2M2. При

поступлении управляющего сигнала осуществляется установка в нулевое состояние триггера 20 и установка в единичное состо- яниетриггера21 всех вычислительных ячеек 1 матрицы (фиг. 2). С приходом очередного синхроимпульса в триггер 20 записывается значение соответствующего элемента fij текущего изображения F, поступающего на оптический вход 6 соответствующей вычислительной ячейки l.i.j матрицы. При поступлении на вход 5 вычислительной ячейки значения элемента gi эталонного изображения G в соответствующей вычислитель- ной ячейке 1 .i.J матрицы на выходе элемента И 23 формируется сигнал д ц , который в случае, если 6 ц 1, сбрасывает в нулевое состояние триггер 21. Если такая ситуация не возникает, то триггер 21 оста- ется в единичном состоянии и излучающий светодиод 25 указывает вычислительную ячейку l.l.j с координатами центра эталонного изображения. В зависимости от кода адреса, поступающего на вход 2 вычисли- гельной ячейки, возможен сдвиг влево (по входу 8), вверх (по входу 9), вправо (по входу 10), вниз (по входу 11) содержимого матрицы вычислительных ячеек 1. После выполнения сдвига информация в матрице вычислительных ячеек 1 и поступления отсчета эталонного изображения, выборка которого, например, на низ запоминающего устройства выполняется в зависимости от кода адреса, формируемого на адресном выходе 41 блока управления, вновь осуществляется формирование сигнала д j j . Этот процесс будет продолжаться до тех пор, пока не будет выполнено считывание из запоминающего устройства всего эталонного изображения G.

Блок управления {фиг. 3) функционирует следующим образом.

При включении питания на входе 29 элока управления вырабатывается сигнал чальной установки, который устанавлива- зт триггер 33 в нулевое состояние, при этом )лемент И 31 блокирует поступление сигна- ia синхронизации со входа 28 блока управления на вход обратного счета счетчика 35. При поступлении сигнала запуска на вход 27 блока управления с приходом очередного синхроимпульса на выходе триггера 30 вырабатывается короткий импульс, который устанавливает в нулевое состояние триггер 32 и счетчики 34, 35, 36, разрешает запись начальных координат эталонного изображения в счетчики 37 и 38, устанавливает в единичное состояние триггер 33 (при этом открывается элемент И 31), формирует единичный сигнал на управляющем входе 18 матрицы вычислительных ячеек, а также обнуляет триггер 30. Следующий синхроимпульс через открытый элемент И 31 поступает на вход 17 синхронизации матрицы вычислительных ячеек, а также на вход обратного счета счетчика 35, при этом короткий импульс на выходе отрицательного признака счетчика 35 приводит к установке в единичное состояние триггера 32, перезаписи содержимого счетчика 34 в счетчик 35 и увеличению на единицу содержимого счетчика 36, что вызывает формирование нового адреса на управляющих входах 16 матрицы вычислительных ячеек, а это, в свою очередь, приводит к изменению содержимого счетчика 37,38, которые формируют на выходе41 блока управления адрес следующего элемента эталонного изображения. Когда счетчики 37, 38 обнуляются, на выходе элемента ИЛИ-НЕ 42 вырабатывается импульс, который устанавливает в нулевое состояние триггер 33 и блокирует подачу синхроимпульсов на счетчик 35, На этом рабочий цикл блока управления заканчивается. Для повторного запуска блока управления необходимо подать сигнал запуска на вход 27 блока управления.

На фиг. 4 показано графическое представление матрицы вычислительных ячеек 1 для определения корреляционных коэффициентов, которая с учетом поля двумерного текущего изображения F размерностью NI х Mi и поля двумерного эталонного изображения G размерностью N2 x M2 для выполнения корреляционной обработки, в процессе которой возможен сдвиг в поле текущего изображения вправо и влево как

максимум на величину а вверх и

вниз-на величину содержит соответственно ( NI + 2 ) столбцов и ( Mi + 2 н ) строк, величины

N2 и М2 могут быть четными.

Для считывания результата корреляционной обработки двумерных изображений выделяется центральная часть матрицы вычислительных ячеек 1 размерностью (Ni - N2 + 1) х (Mi - М2 + 1) в виде окна. Размер окна и его расположение на поле матрицы вычислительных ячеек 1 определяется размерами поля Ni x MI текущего и поля № х хМа эталонного изображений и применяемым способом сканирования эталонного изображения.

На фиг. 5 приведен пример выполнения корреляционной обработки двумерных изображений с использованием матрицы вычислительных ячеек 1 для случая, когда NI Mi 5 (фиг. 5, а) и N2 М2 3 (фиг. 56). При указанном способе сканирования эталонного изображения (фиг. 5,6) на фиг. 5,в и 5, г слева показаны поля текущего изображения F с определенным сдвигом изображения F в соответствующие такты работы устройства, а именно когда возможны изменения состояний триггеров 21 вычислительных ячеек 1 матрицы, содержимое которых показано слева на фиг. 5 в, 5 г. После текущего изображения F размерностью (Ni + N2- 1)x(Mt+ + М2 - 1), реализованное на матрице вычислительных ячеек 1 без учета информационных связей между вычислительными ячейками 1 соответственно первого и старшего столбцов и пеовой и старшей строк матрицы показано на фиг. 5в, а после текущего изображения F размерностью Ni x Mi, реализованное на матрице вычислительных ячеек 1 с учетом информационных связей между вычислительными ячейками 1 соответственно первого и старшего столбцов и первой и старшей строк матрицы показано на фиг. 5,г.

На восьмом такте работы устройства формируется окончательный результат корреляционной обработки, который свидетельствует о том, что вычислительные ячейки 1 матрицы, в которых триггеры 21 находятся в единичном состоянии, соответствуют координатам центра эталонного изображения G на поле текущего изображения F. Поскольку результат корреляционной обработки считывается из окна матрицы вычислительных ячеек 1 размерностью (Ni -N2 + 1)x(Mi-M2+ 1), то наложение информации при сдвиге текущего изображения F в поле матрицы вычислительных ячеек 1 размерностью Ni x Mi не приводит к искажению результата.

Формула изобретения

Коррелятор, содержащий матрицу вычислительных ячеек для определения корреляционных коэффициентов, каждая из которых содержит элемент И, два триггера,

мультиплексор, преобразователь оптического сигнала в электрический, преобразователь электрического сигнала в оптический, а также блок управления, содержащий три триггера, пять счетчиков, дешифратор, элемент И и элемент ИЛИ-НЕ, причем в блоке управления информационный вход первого триггера является входом запуска коррелятора, прямой выход перво0 го триггера соединен с входами сброса первого и второго триггеров, первого, второго и третьего счетчиков, с входами синхронизации четвертого и пятого счетчиков и с установочным входом третьего триггера, вход

5 синхронизации первого триггера соединен с первым входом элемента И и является входом синхронизации коррелятора, информационный вход третьего триггера соединен с шиной нулевого потенциала,

0 прямой выход третьего триггера соединен с вторым входом элемента И, выход которого подключен к синхровходу дешифратора и к входу обратного счета второго счетчика, синхровход которого соединен с выходом

5 признака отрицательного состояния второго счетчика, со счетным входом третьего счетчика и с установочным входом второго триггера, прямой выход которого соединен со счетным входом первого счетчика, ин0 формзционный выход которого соединен с входом задания начального состояния второго счетчика, вход сброса третьего триггера является установочным входом коррелятора, информационный выход

5 третьего счетчика соединен с информационным входом дешифратора, с первого по чет- вертый выходы которого соединены соответственно с входом обратного счета четвертого счетчика, входом прямого счета

0 четвертого и пятого счетчиков, входом обратного счета пятого счетчика, выход признака обнуления которого соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом призна5 ка обнуления четвертого счетчика, выход элемента ИЛИ-НЕ соединен с синхровхо- дом третьего триггера, в каждой вычислительной ячейке для определения корреляционных коэффициентов первый

0 вход элемента И является входом задания эталонного сигнала коррелятора, выход мультиплексора соединен с информационным входом первого триггера, вход сброса первого триггера и установочный вход вто5 рого триггера соединены с установочным входом коррелятора, инверсный выход первого триггера соединен с вторым входом элемента И, выход которого подключен к входу сброса второго триггера, прямой выход которого соединен со входом преобразователя электрического сигнала в оптический, установочный вход коррелятора подключен к установочному входу первого триггера и к установочному входу преобразователя оптического сигнала в электрический, в каждой строке матрицы первые информационные входы мультиплексоров вычислительных ячеек для определения корреляционных коэффициентов каждого последующего столбца соединены с прямыми выходами первых триггеров соответствующих вычислительных ячеек для определения корреляционных коэффициентов предыдущего столбца той же строки, а прямые выходы первых триггеров вычислительных ячеек для определения корреляци- онных коэффициентов последующего столбца соединены со вторыми информационными входами мультиплексоров соответствующих вычислительных ячеек для определения корреляционных коэффициентов предыдущего столбца той же строки, в каждом столбце матрицы третьи информационные входы мультиплексоров вычислительных ячеек для определения корреляционных коэффициентов каждой последующей строки соединены с прямыми выходами первых триггеров соответствующих вычислительных ячеек для определения корреляционных коэффициентов предыдущей строки того же столбца, а прямые выходы первых триггеров вычислитель- ных ячеек для определения корреляционных коэффициентов каждой последующей строки соединены с четвертыми информационными входами мультиплексоров соответствующих вычислительных ячеек для определения корреляционных коэффициентов предыдущей строки того же столбца, прямой выход первого триггера блока управления соединен с входами установки в нуль первых триггеров и входами установки в единицу вторых триггеров всех вычислительных ячеек для определения корреляционных коэффициентов, синхров- ходы первых триггеров вычислительных ячеек для определения корреляционных коэффициентов соединены с выходами элемента И блока управления, информационный выход третьего счетчика блока управления соединен с адресными входами мультиплексоров вычислительных

ячеек для определения корреляционных коэффициентов, входы задания начального состояния четвертого и пятого счетчиков блока управления являются входами задания начальных координат эталонного изображения коррелятора, информационные выходы четвертого и пятого счетчиков подключены к адресному выходу координат эта- лонного изображения коррелятора,

оптические входы преобразователей оптического сигнала в электрический и оптические выходы преобразователей электрического сигнала в оптический всех вычислительных ячеек для определения

корреляционных коэффициентов образуют соответственно оптический вход текущего изображения и оптический выход эталонного изображения коррелятора, отличающийся тем, что, с целью уменьшения

аппаратурных затрат, в каждой строке матрицы первые информационные входы мультиплексороввычислительныхкорреляционных коэффициентов первого столбца соединены с прямыми выходами

первых триггеров соответствующих вычислительных ячеек для определения корреляционных коэффициентов старшего столбца той же строки, а прямые выходы первых триггеров вычислительных ячеек для определения корреляционных коэффициентов первого столбца соединены со вторыми информационными входами мультиплексоров соответствующих вычислительных ячеек для определения корреляционных коэффициентов последнего столбца той же строки, в каждом столбце матрицы третьи информационные входы мультиплексоров вычислительных ячеек для определения корреляционных коэффициентов первой

строки соединены с прямыми выходами первых триггеров соответствующих вычислительных ячеек для определения корреляционных коэффициентов последней строки того же столбца, а прямые выходы первых триггеров вычислительных ячеек для определения корреляционных коэффициентов первой строки соединены с четвертыми информационными входами мультиплексоров соответствующих вычислительных ячеек для определения

корреляционных коэффициентов последней строки того же столбца.

1 Мф

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1989 |

|

SU1674154A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Устройство для преобразования Хо изображения | 1990 |

|

SU1785004A1 |

| Устройство распознавания изображений | 1989 |

|

SU1674153A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Устройство для определения изменения свойств случайных процессов | 1983 |

|

SU1205154A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов и работающих в реальном масштабе времени. Целью изобретения является уменьшение аппаратурных затрат в устройстве. Коррелятор содержит матрицу вычислительных ячеек l.i.j для определения корреляционных коэффициентов (где i 1, 2, ..., N1; j 1, 2 Mi), каждая из которых имеет адресные входы 2, синхровходы 3, входы 4 начальной установки, вход 5 эталонного сигнала, оптический вход 6, оптический выход 7, информационные входы 8-11, информационные выходы 12-15. Использование матрицы вычислительных ячеек 1 для определения корреляционных коэффциен- тов позволяет определить координаты центра эталонного изображения на поле текущего изображения. 5 ил.

О

Л,/ Lj

s№g у $и

U 8 8

oi f/A Аи

Ј

61

жэ

мТ

91

01

ДО

OMOEil

о

CD О

со г/I

т

О

| Коррелятор | 1985 |

|

SU1381539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коррелятор | 1989 |

|

SU1674154A1 |

| Прибор для нагревания перетягиваемых бандажей подвижного состава | 1917 |

|

SU15A1 |

Авторы

Даты

1992-04-30—Публикация

1990-05-28—Подача