сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Коррелятор | 1990 |

|

SU1730640A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

| ЯЧЕЙКА ОДНОРОДНОЙ СТРУКТУРЫ | 1993 |

|

RU2036511C1 |

| Ячейка однородной структуры | 1990 |

|

SU1778757A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ИЗОБРАЖЕНИЯ ОБЪЕКТА | 1992 |

|

RU2054196C1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство диагностирования электронной аппаратуры | 1990 |

|

SU1837244A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1991 |

|

RU2051413C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов и работающих в реальном масштабе времени. Целью изобретения является расширение функциональных возможностей за счет определения координат двумерного эталонного изображения на поле текущего изображения. Коррелятор содержит матрицу вычислительных ячеек, каждая из которых имеет адресный вход, синхровход, вход начальной установки, вход эталонного сигнала, оптический вход, оптический выход, информационные входы, информационные выходы. 3 ил.

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных устройствах, применяемых для цифровой обработки сигналов, работающих в реальном масштабе времени

Целью изобретения является расширение функциональных возможностей за счет определения координат двумерного эталонного изображения на поле текущего изображения.

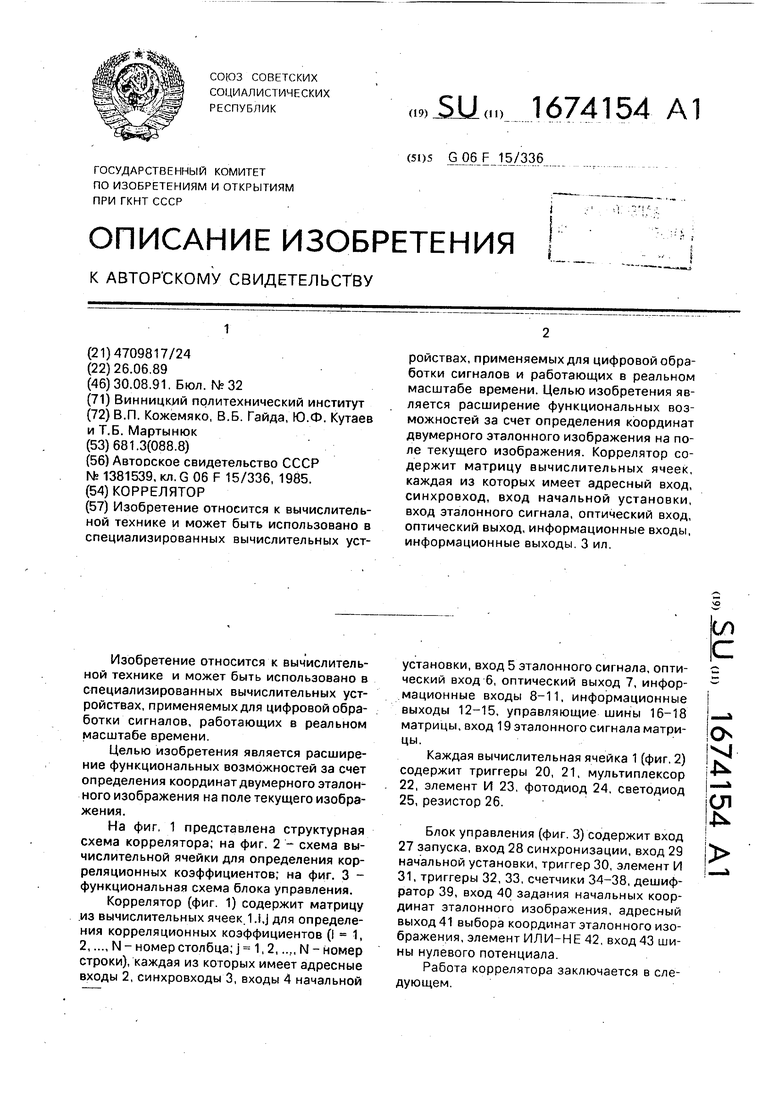

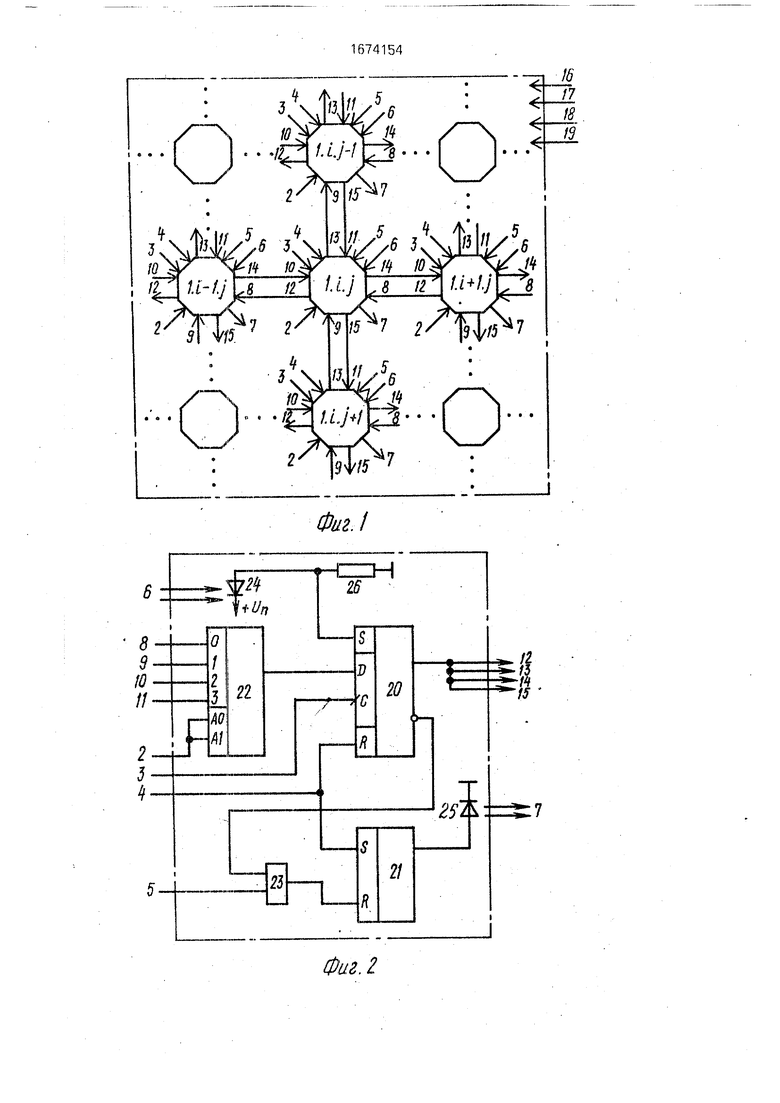

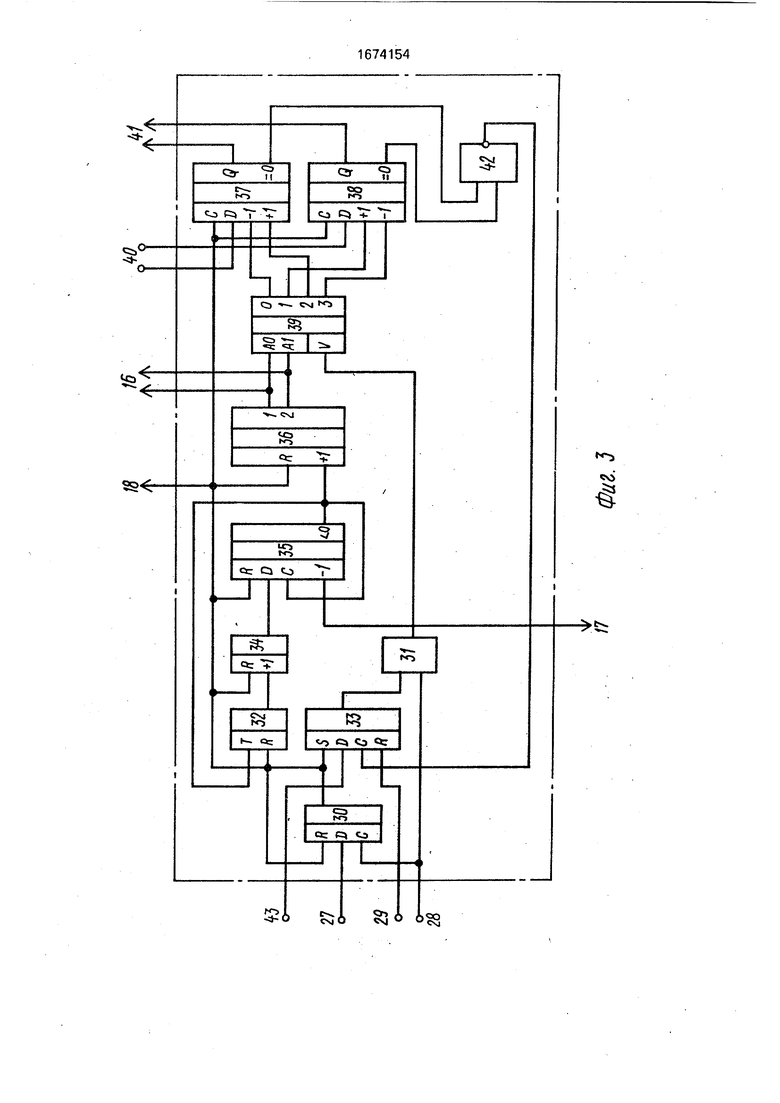

На фиг. 1 представлена структурная схема коррелятора; на фиг. 2 - схема вычислительной ячейки для определения корреляционных коэффициентов; на фиг. 3 - функциональная схема блока управления.

Коррелятор (фиг 1) содержит матрицу из вычислительных ячеек 1.IJ для определения корреляционных коэффициентов (1 1,

2, ., N - номер столбца; j 1, 2N - номер

строки), каждая из которых имеет адресные входы 2, синхровходы 3, входы 4 начальной

установки, вход 5 эталонного сигнала, оптический вход 6, оптический выход 7, информационные входы 8-11, информационные выходы 12-15, управляющие шины 16-18 матрицы, вход 19 эталонною сигнала матрицы

Каждая вычислительная ячейка 1 (фиг. 2) содержит триггеры 20, 21, мультиплексор 22, элемент И 23, фотодиод 24. светодиод 25, резистор 26.

Блок управления (фиг 3) содержит вход 27 запуска, вход 28 синхронизации, вход 29 начальной установки,триггер 30, элемент И 31, триггеры 32, 33, счетчики 34-38, дешифратор 39, вход 40 задания начальных координат эталонного изображения, адресный выход 41 выбора координат эталонного изображения, элемент ИЛИ-НБ 42 вход 43 шины нулевого потенциала

Работа коррелятора заключается в следующем

о

XJ

Ј

,

Коррелятор выполняет определение местонахождения двумерного эталонного изображения G {gki} на поле двумерного текущего изображения F {f|j} , где I, j 1,

2 N; I 1, 2 М. При поступлении

управляющего сигнала осуществляется установка в нулевое состояние триггера 20 и установка в единичное состояние триггера 21 всех вычислительных ячеек 1 матрицы (фиг. 2). Затем с приходом очередного синхроимпульса выполняется запись в триггер 20 значения соответствующего элемента fij текущего изображения F, поступающего на оптический вход 6 соответствующей вычислительной ячейки 1 .i,j матрицы. При поступлении на вход 5 вычислительной ячейки значения элемента эталонного изображения G в соответствующей вычислительной ячейке 1 ,l,j матрицы на выходе элемента И 23 формируется сигнал д - gicrfij, который при 5ij 1. сбрасывает в нулевое состояние триггер 21. Если такая ситуация не возникает, то триггер 21 остается в единичном состоянии и излучающий светодиод 25 указывает вычислительную ячейку 1.I.J с координатами центра эталонного изображения. В зависимости от кода адреса, поступающего на вход 2 вычислительной ячейки, возможен сдвиг влево (по входу 8), вверх (по входу 9), вправо (по входу 10), вниз (по входу 11) содержимого матрицы вычислительных ячеек 1. После выполнения сдвига информации в матрице вычислительных ячеек 1 и поступления отсчета gici эталонного изображения, выборка которого, например, из запоминающего устройства, выполняется в зависимости от кода адреса, формируемого на адресном выходе 41 блока управления, вновь осуществляется формирование сигнала бу. Этот процесс продолжается до тех пор, пока не будет выполнено считывание из запоминающего устройства всего эталонного изображения G. Блок управления (фиг. 3) функционирует следующим образом.

При включении питания на входе 29 блока управления вырабатывается сигнал начальной установки, который устанавливает триггер 33 в нулевое состояние, при этом элемент И 31 блокирует поступление сигнала синхронизации с входа 28 блока управления на вход обратного счета счетчика 35. При поступлении сигнала запуска на вход 27 блока управления с приходом очередного синхроимпульса на выходе триггера 30 вырабатывается короткий импульс, который устанавливает в нулевое состояние триггер 32 и счетчики 34-36, разрешает запись начальных координат эталонного изображения в счетчики 37 и 38, устанавливает в единичное состояние триггер 33 (при этом открывается элемент И 31), формирует единичный сигнал на управляющем входе

18 матрицы вычислительных ячеек, а также обнуляет триггер 30. Следующий синхроимпульс через открытый элемент И 31 поступает на вход 17 синхронизации матрицы вычислительных ячеек а также на вход об0 ратного счета счетчика 35, при этом короткий импульс на выходе отрицательного признака счетчика 35 приводит к установке в единичное состояние триггера 32. перезаписи содержимого счетчика 34 в счет5 чик 35 и увеличению на единицу содержимого счетчика 36, что вызывает формирование нового адреса на управляющих входах 16 матрицы вычислительных ячеек, а это, в свою очередь, приводит к изменению

0 содержимого счетчиков 37, 38, которые формируют на выходе 41 блока управления адрес следующего элемента эталонного изображения. Когда счетчики 37, 38 обнуляются, на выходе элемента ИЛИ-НЕ 42

5 вырабатывается импульс, который устанавливает в нулевое состояние триггер 33 и блокирует подачу синхроимпульсов на счетчик 35. На этом рабочий цикл блока управления заканчивается. Для повторного

0 запуска блока управления необходимо подать сигнал запуска на вход 27 блока управления.

Формула изобретения Коррелятор, содержащий матрицу вы5 числительных ячеек для определения корреляционных коэффициентов, каждая из которых содержит элемент И, первый вход которого подключен к входу эталонного сигнала коррелятора, отличающийся

0 тем, что, с целью расширения функциональных возможностей за счет определения координат двумерного эталонного изображения на поле текущего изображения, в коррелятор введен блок управления,

5 содержащий три триггера, пять счетчиков, дешифратор, элемент И, элемент ИЛИ-НЕ, а в каждую вычислительную ячейку введены два триггера, мультиплексор, фотодиод, светодиод, токозадающий резистор, причем

0 в блоке управления информационный вход первого триггера является входом запуска коррелятора, вход установки в О первого триггера соединен с входами установки в О второго триггера, первого, второго,

5 третьего счетчиков, входами синхронизации четвертого и пятого счетчиков, с входом установки в 1 третьего триггера и с прямым выходом первого триггера, вход синхронизации первого триггера соединен с первым входом элемента И и является входом синхронизации соррглчюря информационный вход третьего трмг гера соединен с шиной нулевого потенциала прямой выход третьего триггера соединен с вторым входом элемента И, выход которого соединен с синхровходом дешифратора и входом обратного счета второго счегчика, синхровход которого соединен с выходом признака отрицательного состояния второго счетчика, со счетным входом третьего счетчика и входом установки в 1 второго триггера, прямой выход которого соединен со счетным входом первого счетчика, информационный выход которого соединен с входом задания начального состояния второго счетчика, вход установки в О третьего триггера является входом установки в исходное состояние коррелятора, информационный выход третьего счетчика соединен с информационным входом дешифратора, с первого по четвертый выходы которого соединены соответственно с входом обратного счета четвертого счетчика, входом прямого счета пятого и четвертого счетчиков, входом обратного счета пятого счетчика, выход признака обнуления которого соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом признака обнуления четвертого счетчика, выход элемента ИЛИ-НЕ соединен с синхровходом третьего триггера, в каждой вычислительной ячейке для определения корреляционных коэффициентов выход мультиплексора соединен с информационным входом первого триггера, вход установки в О первого триггера и вход установки в 1 второго триггера подключены к входу установки начального состояния коррелятора, инверсный выход первого триггера соединен с вторым входом элемента И, выход которого соединен с входом установки в О второго триггера, прямой выход которого соединен с электрическим входом светоди- ода, электрический выход которого подключен к шине нулевого потенциала, к которой подключен первый вывод токозадающего резистора, второй вывод которого подключен к входу установки в 1 первого триггера и электрическому входу фотодиода, электрический выход которого соединен с шиной положительного потенциала, в каждой строке матрицы первые информационные входы мультиплексоров вычислительных ячеек для определения корреляционных коэффициентов каждого последующего с голбца со- единены с прямыми выходами первых

тршгеров соответствующих вычислиггль ных ячеек для определения коррелчципн ных коэффициентов предыдущего глолГща той же строки, а прямые выходы перпьк 5 триггеров вычислительных ячеек для опрг деления корреляционных коэффициентов последующего столбца соединены с вторы ми информационными входами мультиплексоров соответствующих вычислительных 0 ячеек для определения корреляционных коэффициентов предыдущего столбца той же строки, в каждом столбце матрицы третьи информационные входы мультиплексоров вычислительных ячеек для определения 5 корреляционных коэффициентов каждой последующей строки соединены с прямыми выходами первых триггеров соответствующих вычислительных ячеек для определения корреляционых коэффициентов предыдущей

0 строки того же столбца, а прямые выходы первых триггеров вычислительных ячеек для определения корреляционных коэффициентов каждой последующей строки соединены с четвертыми информационными

5 входами мультиплексоров соответствующих вычислительных ячеек для определения корреляционных коэффициентов предыдущей строки того же столбца, прямой выход первого триггера блока управления соеди0 нен с входами установки в О первых триггеров и входами установки в 1 вторых триггеров всех вычислительных ячеек для определения корреляционных коэффициентов, синхровходы первых триггеров вычис5 лительных ячеек для определения корреляционных коэффициентов соединены с выходом элемента И блока управления, информационный выход третьего счетчика блока управления соединен с адресными

0 входами мультиплексоров вычислительных ячеек для определения корреляционных коэффициентов, входы задания начального со- стояния четвертого и пятого счетчиков блока управления являются входами зада5 ния начальных координат эталонного изображения коррелятора, информационные выходы четвертого и пятого счетчиков подключены к адресному выходу координат эталонного изображения коррелятора,

0 оптические входы фотодиодов и оптические выходы светодиодов всех вычислительных ячеек для определения корреляционных коэффициентов образуют соответственно оптический вход текущею изображения и

5 оптический выход эталонного изображения коррелятора

IV

OJ

N

IN

I CT1 -J

tr,-vj

01

о

A A /tv

J3

o5 -vjicr,

t

Sic

о -J л

ел

I Л

/7

Фиг.З

| Коррелятор | 1985 |

|

SU1381539A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-30—Публикация

1989-06-26—Подача