ю сь

4

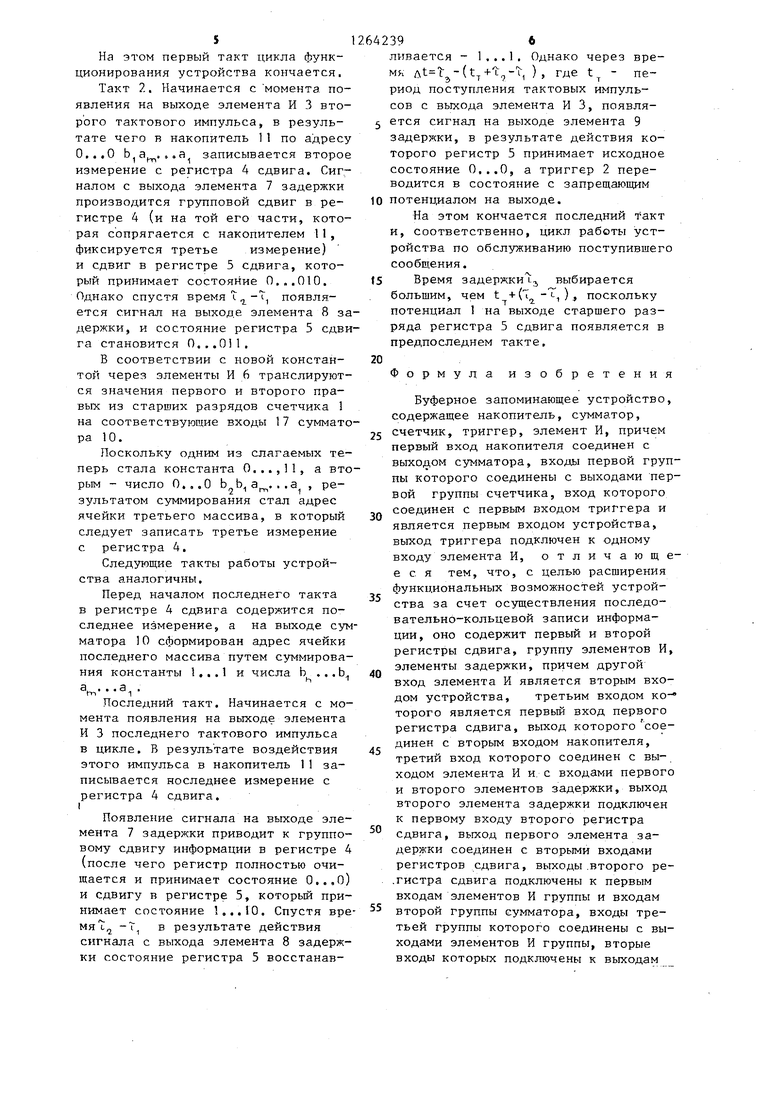

ю со .Изобретение относится к вычислительной технике и может быть исполь зовано в буферных запоминающих устройствах систем ввода и систем обработки информации многоканальных измерительных комплексов. Цель изобретения - расширение функциональных возможностей устройства за счет осуществления последовательно-кольцевой записи информации. На чертеже приведена структур на схема устройства (механизм считывания информации из массивов устройства не показан). Устройство содержит счетчик 1, триггер 2, элемент ИЗ, первый регистр 4 сдвига, второй регистр 5 сдвига, группу элементов И 6, первый элемент 7 задержки, второй элемент 8 задержки, третий элемент 9 задержки, сумматор 10, накопитель 11, первый вход 12 устройства, второй вход 13 устройства, третий вход 14 устройства, шины 15-17. Счетчик 1 предназначен для фиксации .синхросигналов, поступающих на первый вход 12 устройства одновременно с информационными сообщениями. Выходы старших разрядов счет чика образуют группу выходов 15, а выходы младших разрядов - группу вы ходов 16, причем выходы младших разрядов подаются на сумматор 10 не посредственно, а выходы старших раз рядов - через элементы И 6. Число младших разрядов счетчика определяется емкостью меньшего массива буфе ра, а число старших разрядов равно числу массивов. Триггер 2 предназначен для фикса ции начала и конца цикла работы уст ройства. Цикл начинается в момент п ступления на первый вход 12 устройства синхроимпульса и отмечается по явлением разрешающего потенциала на выходе триггера в результате воздействия синхроимпульса на его первый вход. Цикл оканчивается в момен появления на выходе триггера запрещающего потенциала в результате воз действия на второй вход триггера сигнала с выхода элемента 9 задержк I Элемент И 3 предназначен для коммутации через его второй вход та товых импульсов генератора (не покаэан) с второго входа 13 устройств Каждый тактовый импульс с выхода эл мента И 3 является уцравляющкм сигналом Д.ЛЯ накопителя 1 1 и регистров 4 и 5 сдвига. Первый регистр 4 сдвига предназначен для фиксации и последующего сдвига сообщения, поступающего -на его вход с третьего входа 14 устройства. Сообщение представляет собой совокупность измерений, из которых подлежит записи в соответствующий массив накопителя 11, Б каждом такте цикла работы устройства в регистре производится групповой сдвиг хранимой информации таким образом, чтобы к записи в накопитель бьото подготовлено очередное измерение сообщения. Второй регистр 5 сдвига предназначен для образования последовательности констант 0...01,0...011,0... 011 I ,01 .... 1,1 ... 1 в цикле работы устройства. Число вырабатываемых констант равно числу старших разрядов счетчика 1. В начале каждого цикла регистр находится в состояНИИ 0.,.0. Установка его в это состояние из состояния 1 ... 1 производится сигналом с выхода элемента 9 задержки в последнем цикла. Образование констант производится при помощи сигналов сдвига и установки младщегс разряда в 1, поступающих соответственно с выходов элементов 7 и 8 задержки. 1 Элементы И 6 предназначены дпя коммутации старших разрядов I5 счетчика 1 на соответствующие входы 17 сумматора 10. Коммутация тех или иных элементов И 6 определяется константой, поступающей на их первые входы с регистра 5 сдвига Элементы 7 и 8 задержки предназ начены для задержки тактового им- -, пульса с выхода элемента И 3 на время, большее времени записи измерения с регистра 4 сдвига в накопитель 11. Выход элемента 7 задержки соединен со сдвигающими входами регистров 4 и 5 сдвига. Задержанным этим элементом на время t тактовый импульс производит групповой сдвиг в регистре 4 сдвига и поразрядный сдвиг -в регистре 5 сдвига, И мпульс с выхода элемента 8 задержки, задерживающего тактовый импульс , осуществляет запись 1 в правый (младший) разряд регистра 5 сдвига. Наличие элементов 7 и 8 задержки позволяет образовывать константы в регистре 5 сдвига для соответ ствующих тактов цикла работы устройства. Элемент 9 задержки предназначен для задержки на время i потенциал с выхода старшего (левого) разряда регистра 5 сдвига с целью своевременной фиксации конца цикла работы устройства состоянием триггера 2 и приведения в исходное (нулевое) состояние регистра 5 сдвига. Сумматор 10 предназначен для об разования адреса обращения к накоп телю 11 в результате суммирования двух слагаемых. Первое слагаемое представляет собой композицию млад ших разрядов счетчика 1, поступающих по шинам 16, и старших разрядо счетчика, коммутируемых через злементы И 6 сигналом с регистра 5 сдви га. Вторым слагаемым является константа с регистра 5 сдвига. Веса разрядов константы равны весам соо ветствующих старших разрядов сч чика 1. Если второе слагаемое равно 0...0, то старшие разряды счетч ка 1 в образовании первого слагаемого не участвуют и результатом суммирования является код младших разрядов счетчика 1. Накопитель 11 предназначен для фиксации по сигналу с выхода элем та И 3 измерения с регистра 4 сдви га по адресу с сумматора 10. Устройство работает следующим о разом. Перед началом очередного цикла работы устройства регистр 5 сдвига находится в состоянии 0...0, а на выходе триггера 2 имеется запрещающий потенциал, препятствующий про хождению через элемент И 3 тактовых импульсов с второго входа 13 устройства. Очередной цикл работы устройства начинается с поступления очередного синхроимпульса по первому входу 12 устройства и соответствующего ему очередного сообщения по третьему входу 14 устройства. Синхроимпульс учитывается счетчиком I и взводит триггер 2, в результате чего на вых де последнего образуется разрещающий потенциал, поступающий на пер вый вход элемента И 3. В дальнейшем работа устройства происходит в несколько тактов. Такт 1. Начинается с момента появления на выходе элемента И 3 первого тактового импульса в цикле. Тактовый импульс воздействует на управляющий вход накопителя 11, в результате чего в последнем запускается циклограмма режима Запись. Поскольку при этом регистр 5 сдвига находится в состоянии 0...0 и на выходах всех элементов И 6 имеют место О, то результатом суммирования, а следовательно, и адресом памяти является состояние младших разрядов счетчика 1, поступающих на сумматор IО по шинам 16. По этому адресу в память записывается измерение, содер кащееся в той части регистра 4 сдвига, которая соединена с информационным входом накопителя 1 1 . Спустя время L, (большее, чем время записи измерения в память) тактовый импульс появляется на выходе элемента 7 задержки, в результате чего, во-первых, производится групповой сдвиг в регистре 4 сдвига и в той его части, которая соединена с накопителем 11, фиксируется второе измерение сообщения, во-вторых, осуществляется сдвиг на один разряд влево содержимого регистра 5 сдвига. Однако, поскольку этот регистр находился в состоянии 0...0, то после воздействия ртмпульса сдвига состояние его не меняется. Спустя время - с начала такта 1 тактовый импульс появляется на выходе элемента 8 задержки, в результате чего в младший разряд регистра 5 сдвига заносится 1 и регистр принимает состояние O...OI. В соответствии с его состоянием через соответствующий элемент И 6 транслируется состояние правого (младшего) из старших разрядов счетчика 1 на соответствующий вход 17 группы входов сумматора 10. Поскольку первым слагаемым стало число 0.. .0 . а .. .а , Гг, 1 Ц - зназначения младших разрядов, разрядов чение правого из старших счетчика 1, а вторым слагаемым - константа O...D1, на выходе сумматора 10 образуется число, соответствуюее следующему адресу из второго ассива памяти, по которому следует аписать второе измерение с региста 4 Сдвига, S На этом первый такт цикла функционирования устройства кончается. Такт .. Начинается с момента появления на выходе элемента И 3 второго тактового импульса, в результате чего в накопитель 11 по адресу О..,0 . ..а записывается второе измерение с регистра 4 сдвига. Сигналом с выхода элемента 7 задержки производится групповой сдвиг в регистре 4 (и на той его части, которая сопрягается с накопителем 11, фиксируется третье измерение) и сдвиг в регистре 5 сдвига, который принимает состояние П...010. Однако спустя время появляется сигнал на выходе элемента 8 за держки, и состояние регистра 5 сдви га становится П..,011. В соответствии с новой константой через элементы И 6 транслируются значения первого и второго правых из старших разрядов счетчика 1 на соответствующие входы 17 суммато ра 10. Поскольку одним из слагаемых теперь стала константа 0...,П, а вто рым - число О..,0 b . ..а , результатом суммирования стал адрес ячейки третьего массива, в который следует записать третье измерение с регистра 4. Следующие такты работы устройства аналогичны. Перед началом последнего такта в регистре 4 сдвига содержится последнее измерение, а на выходе сум матора 10 сформирован адрес ячейки последнего массива путем суммирова ния константы t...l и числа b ...b а,- Последний такт. Начинается с мо мента появления на выходе элемента И 3 последнего тактового импульса в цикле. В результате воздействия этого импульса в накопитель 11 записывается последнее измерение с регистра 4 сдвига. I Появление сигнала на выходе элемента 7 задержки приводит к групповому сдвигу информации в регистре 4 (после чего регистр полностью очищается и принимает состояние О..,0 и сдвигу в регистре 5, который принимает состояние 1,..10. Спустя вре мя 7 -Т в результате действия сигнала с выхода элемента 8 задержки состояние регистра 5 восстанав396ливается - 1 ... 1 . Однако через врея (, ), где t - период поступления тактовых импульсов с выхода элемента И 3, появляется сигнал на выходе элемента 9 задержки, в результате действия которого регистр 5 принимает исходное состояние 0...0, а триггер 2 переводится в состояние с запрещающим потенциалом на выходе. На этом кончается последний такт и, соответственно, цикл работы устройства по обслуживанию поступившего сообщения. Время задержкиЕ.,, выбирается большим, чем t +(, ), поскольку потенциал на выходе старшего разряда регистра 5 сдвига появляется в предпоследнем такте, Формула изобретения Буферное запоминающее устройство, содержащее накопитель, сумматор, счетчик, триггер, элемент И, причем первый вход накопителя соединен с выходом сумматора, входы первой группы которого соединены с выходами первой группы счетчика, вход которого соединен с первым входом триггера и является первым входом устройства, выход триггера подключен к одному входу элемента И, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет осуществления последовательно-кольцевой записи информации, оно содержит первый и второй регистры сдвига, группу элементов И, элементы задержки, причем другой вход элемента И является вторым входом устройства, третьим входом ко- торого является первый вход первого регистра сдвига, выход которого соединен с вторым входом накопителя, третий вход которого соединен с вы-. ходом элемента И и. с входами первого и второго элементов задержки, выход второго элемента задержки подключен к первому входу второго регистра Сдвига, выход первого элемента задержки соединен с вторыми входами регистров сдвига, выходы .второго ре.гистра сдвига подключены к первым входам элементов И группы и входам второй группы сумматора, входы третьей группы которого соединены с выходами элементов И группы, вторые входы которых подключены к выходам

712642398

второй группы счетчика, выход старше- задержки, выход которого подключен к го разряда второго регистра сдвига третьему входу второго регистра сдвисоединен с входом третьего элемента га и второму входу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1986 |

|

SU1381565A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1304079A1 |

| Многоканальный коммутатор | 1985 |

|

SU1260993A1 |

| Многоканальный коммутатор | 1985 |

|

SU1305749A2 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для умножения | 1985 |

|

SU1254473A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2450343C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ И ДИФФЕРЕНЦИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2470359C1 |

Изобретение относится к вычислительной технике и может быть использовано в буферных запоминающих устройствах систем ввода и систем обработки информации многоканальных измерительных комплексов. Цель изобретения - расширение функциональных возможностей устройства за счет осуществления последовательно-кольцевой записи информации. Для этого в буферное запоминающее устройство, содержащее накопитель I1, сумматор 10, счетчик 1, триггер 2, элемент ИЗ, введены регистры 4, 5 сдвига, группа 6 элементов И, элементы 7,8, 9 задержки с соответствующими функциональными связями. 1 ил. (Л с

| Буферное запоминающее устройство | 1981 |

|

SU991512A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1034069A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-15—Публикация

1985-02-04—Подача