Изобретение относится к вычислительной технике и может быть использовано в буферных запоминающих устройствах систем ввода и обработки информации многоканальных измерительных комплексов.

Цель изобретения расширение области применения устройства за счет последовательно-кольцевой записи информации из массивов произвольного объема.

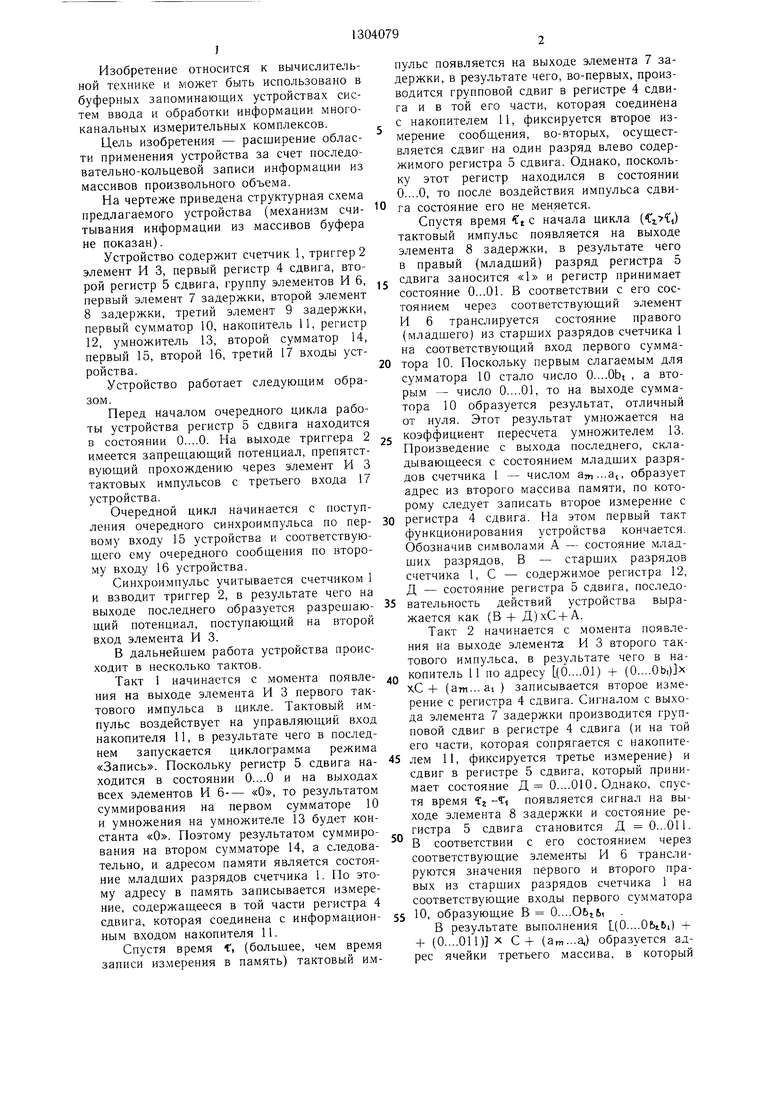

На чертеже приведена структурная схема

пульс появляется на выходе элемента 7 задержки, в результате чего, во-первых, производится групповой сдвиг в регистре 4 сдвига и в той его части, которая соединена с накопителем 11, фиксируется второе измерение сообщения, во-вторых, осуществляется сдвиг на один разряд влево содержимого регистра 5 сдвига. Однако, поскольку этот регистр находился в состоянии 0....0, то после воздействия импульса сдвипредлагаемого устройства (механизм счи- 0 га состояние его не меняется.

тывания информации из массивов буфераСпустя время ft с начала цикла ( tj,t,)

тактовый импульс появляется на выходе элемента 8 задержки, в результате чего

в правый (младший) разряд регистра 5

не показан).

Устройство содержит счетчик 1, триггер 2 элемент И 3, первый регистр 4 сдвига, второй регистр 5 сдвига, группу элементов И 6, ,5 сдвига заносится «1 и регистр принимает первый элемент 7 задержки, второй элемент состояние 0...01. В соответствии с его состоянием через соответствующий элемент И 6 транслируется состояние правого (младшего) из старших разрядов счетчика 1 на соответствующий вход первого сумма- 20 тора 10. Поскольку первым слагаемым для сумматора 10 стало число O....0bt , а вто8 задержки, третий элемент 9 задержки, первый сумматор 10, накопитель 11, регистр 12, умножитель 13, второй сумматор 14, первый 15, второй 16, третий 17 входы устройства.

Устройство работает следующим образом.

Перед началом очередного цикла работы устройства регистр 5 сдвига находится

рым - число 0....01, то на выходе сумматора 10 образуется результат, отличный от нуля. Этот резу.тьтат умножается на

в состоянии 0....0. На выходе триггера 2 25 коэффициент пересчета умножителем 13.

Произведение с выхода последнего, складывающееся с состоянием младших разрядов счетчика 1 - числом am---ai, образует адрес из второго массива памяти, по которому следует записать второе измерение с

имеется запрещающий потенциал, препятствующий прохождению через э лемент И 3 тактовых импульсов с третьего входа 17 устройства.

Очередной цикл начинается с поступления очередного синхроимпульса по пер- 30 регистра 4 сдвига. На этом первый такт во.му входу 15 устройства и соответствую- функционирования устройства кончается, щего ему очередного сообщения по второ- Обозначив символами А - состояние млад- му входу 16 устройства.ших разрядов, В - старших разрядов

Синхроимпульс учитывается счетчиком 1 счетчика 1, С - содержимое регистра 12, и взводит триггер 2, в результате чего на Д - состояние регистра 5 сдвига, последо- выходе последнего образуется разрешаю- 35 вательность действий устройства выра- щий потенциал, поступающий на второй жается как (В + Д)хС + А.

Такт 2 начинается с момента появления на выходе элемента И 3 второго тактового импульса, в результате чего в наТакт 1 начинается с момента появле- до копитель 11 по адресу Цб....01) + (О....ОЬ,)х ния на выходе элемента И 3 первого так- хС + (атп...а1 ) записывается второе измерение с регистра 4 сдвига. Сигналом с выхода элемента 7 задержки производится групповой сдвиг в регистре 4 сдвига (и на той его части, которая сопрягается с накопитехЗапись. Поскольку регистр 5 сдвига на- 45 лем 11, фиксируется третье измер ение) и ходится в состоянии 0....0 и на выходах сдвиг в регистре 5 сдвига, который принимает состояние Д 0....010. Однако, спустя время Tj -ЧГ, появляется сигнал на выходе элемента 8 задержки и состояние рестанта «О. Поэтому результатом суммиро- „ гистра 5 сдвига становится Д 0...011. вания на втором сумматоре 14, а следова- В соответствии с его состоянием через

соответствующие элементы И 6 транслируются значения первого и второго правых из старших разрядов счетчика 1 на соответствующие входы первого сумматора

сдвига, которая соединена с информацион- 55 О, образующие В О....ОЬгЬ, ным входом накопителя 11.В результате выполнения L(0....0bibi) +

Спустя время f, (большее, чем время + (О....011)х С+ (am...а,) образуется ад- записи измерения в память) тактовый им- рее ячейки третьего массива, в который

вход элемента И 3.

В дальнейшем работа устройства происходит в несколько тактов.

тового импульса в цикле. Тактовый импульс воздействует на управляющий вход накопителя 11, в результате чего в последнем запускается циклограмма режима

всех элементов И 6- «О, то результатом суммирования на первом сумматоре 10 и умножения на умножителе 13 будет контельно, и адресом памяти является состояние младших разрядов счетчика 1. По этому адресу в память записывается измерение, содержащееся в той части регистра 4

пульс появляется на выходе элемента 7 задержки, в результате чего, во-первых, производится групповой сдвиг в регистре 4 сдвига и в той его части, которая соединена с накопителем 11, фиксируется второе измерение сообщения, во-вторых, осуществляется сдвиг на один разряд влево содержимого регистра 5 сдвига. Однако, поскольку этот регистр находился в состоянии 0....0, то после воздействия импульса сдви га состояние его не меняется.

в правый (младший) разряд регистра 5

сдвига заносится «1 и регистр принимает состояние 0...01. В соответствии с его состоянием через соответствующий элемент И 6 транслируется состояние правого (младшего) из старших разрядов счетчика 1 на соответствующий вход первого сумма- тора 10. Поскольку первым слагаемым для сумматора 10 стало число O....0bt , а вторым - число 0....01, то на выходе сумматора 10 образуется результат, отличный от нуля. Этот резу.тьтат умножается на

коэффициент пересчета умножителем 13.

Произведение с выхода последнего, складывающееся с состоянием младших разрядов счетчика 1 - числом am---ai, образует адрес из второго массива памяти, по которому следует записать второе измерение с

регистра 4 сдвига. На этом первый такт функционирования устройства кончается, Обозначив символами А - состояние млад- ших разрядов, В - старших разрядов

следует записать третье измерение с регистра 4 сдвига.

На этом второй такт функционирования устройства кончается. Последующие такты работы устройства аналогичны.

Перед началом последнего такта в регистре 4 сдвига содержится последнее измерение, а на выходе второго сумматора 14 сформирован адрес ячейки последнего массива

L(6n...bO+ (1... l)Jx C-H(dm... tti).

Последний такт начинается с момента появления на выходе элемента И 3 последнего тактового импульса в цикле. В результате воздействия этого импульса в накопитель 11 записывается последнее измерение с регистра 4 сдвига.

Появление сигнала на выходе элемента 7 задержки приводит к групповому сдвигу информации в регистре 4 (после чего регистр полностью очищается и принимает состояние 0....0) и сдвигу в регистре 5, который принимает состояние 1...10. Спустя время г -TI в результате действия сигнала с выхода элемента 8 задержки состояние регистра восстанавливается - 1...1. Однако, через время -(ty + + Тг -Т, ), где t,.- период поступления тактовых импульсов с выхода элемента И 3, появляется сигнал на выходе элемента 9 задержки, в результате действия которого регистр 5 сдвига принимает исходное состояние 0...0, а триггер 2 переводится в состояние с запрещающим потенциалом на выходе.

На этом кончается последний такт и соответственно цикл работы устройства по обслуживанию поступивщего сообщения.

Время задержки fj выбирается больщим, чем tr-f (Сг. - Т| ) поскольку потенциал «1 на выходе левого (старшего) разряда регистра 5 сдвига появляется в предпоследнем такте.

Предлагаемое устройство позволяет осуществить последовательно-кольцевую запись информации в массивы памяти, млад- щий из которых может иметь произвольный объем. Реализация устройства проста и может быть выполнена незначительным колиРедактор И. Касарда Заказ 1316/52

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

П3035, Москва, Ж-35, Рауи1ская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, -1

чеством интегральных микросхем средней степени интеграции.

Формула изобретения

Буферное запоминающее устройство, содержащее счетчик, накопитель, триггер, элемент И, группу элементов И, первый сумматор, первый и второй регистры сдвига, первый, второй и третий элементы задержки, причем первый вход триггера соединен с входом счетчика и является первым входом устройства, первый, вход первого регистра сдвига является вторым входом устройства, а первый вход элемента И является третьим входом устройства, второй вход элемента И соединен с выходом триггера, а выход - с входами первого и второго элементов задержки и с управляющим входом накопителя, информационный вход которого соединен с выходом первого регистра сдвига, второй вход которого соединен с выходом первого элемента задержки, и с первым входом второго регистра сдвига, второй вход которого соединен с выходом второго элемента задержки, а третий вход соединен с вторым входом триггера и с выходом третьего элемента задержки, вход которого соединен с выходом старщего разряда второго регистра сдвига, одни выходы которого соединены с соответствующими входами первого сумматора

и с первыми входами соответствующих элементов И группы, вторые входы которых соединены с соответствующими выходами счетчика, а выходы соединены с соответствующими входами первого сумматора, отличающееся тем, что, с целью расщирения

области применения устройства за счет последовательно-кольцевой записи информации из массивов произвольного объема, в состав устройства введены второй сумматор, умножитель и регистр, выход которого соединен с первым входом умножителя, второй вход которого соединен с выходом первого сумматора, а выход соединен с первым входо.м второго сумматора, второй вход которого соединен с выходом счетчика, а выход соединен с адресным входом накопителя.

Составитель В. Гордонова

Техред И. ВересКорректор М. Пожо

Тираж 590Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1985 |

|

SU1264239A1 |

| Многоканальный коммутатор | 1985 |

|

SU1305749A2 |

| Многоканальный коммутатор | 1986 |

|

SU1381565A1 |

| Многоканальный коммутатор | 1985 |

|

SU1260993A1 |

| Вычислительное устройство | 1986 |

|

SU1432510A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1282156A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1985 |

|

SU1312611A1 |

| Цифровой рекурсивный фильтр | 1988 |

|

SU1578720A1 |

| Устройство для спектрального анализа с постоянным относительным разрешением | 1982 |

|

SU1109760A1 |

Изобретение относится к средствам накопления и хранения информации и может использоваться в системах управления и обработки данных. Цель изобретения состоит в расширении области применения устройства за счет последовательно-кольцевой записи информации из массивов произвольного объема. Адрес ячейки любого массива образуется путем сложения на втором сумматоре содержимого младших разрядов счетчика и результата произведения двух чисел: коэффициента пересчета и частичной суммы с первого сумматора. 2 ил. S (Л со о N О ;о

| Буферное запоминающее устройство | 1982 |

|

SU1034069A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1264239A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-04-15—Публикация

1985-09-20—Подача