Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания быстродействующих, специализированных и высокопроизводительных цифровых процессоров, выполняющих логические операции: конъюнкцию, дизъюнкцию, инверсию, исключающее ИЛИ.

Известно "Устройство управления" (з-ка UA, Авторское свидетельство СССР № 1285963 от 1995.10.20 г.), позволяющее выполнять логические операции.

Известно "Устройство для вычислений" (з-ка RU №2042186 от 1995.08.20 г.), позволяющее в специализированных процессорах для обработки нечеткой информации выполнять арифметические и логические операции.

Известен "Сумматор" (з-ка RU №2049346 от 1995.11.27 г.), предназначенный для арифметической и логической обработки цифровой информации.

В качестве прототипа выбран "Сумматор" (з-ка RU №94007826 от 1996.02.27 г.), который выполняет функции конъюнкции, дизъюнкции, равнозначности, констант "0" и единицы.

Задача заключалась в следующем:

1) расширить функциональные возможности устройства,

2) повысить скорость выполнения логических операций,

3) повысить надежность работы устройства выполнения логических операций.

В представленном устройстве выполнения логических операций выполняются основные логические операции: конъюнкции, дизъюнкции, инверсии, исключающее ИЛИ.

Предлагаемое устройство позволит расширить функциональные возможности, повысить скорость выполнения логических операций, упростит алгоритм работы устройства.

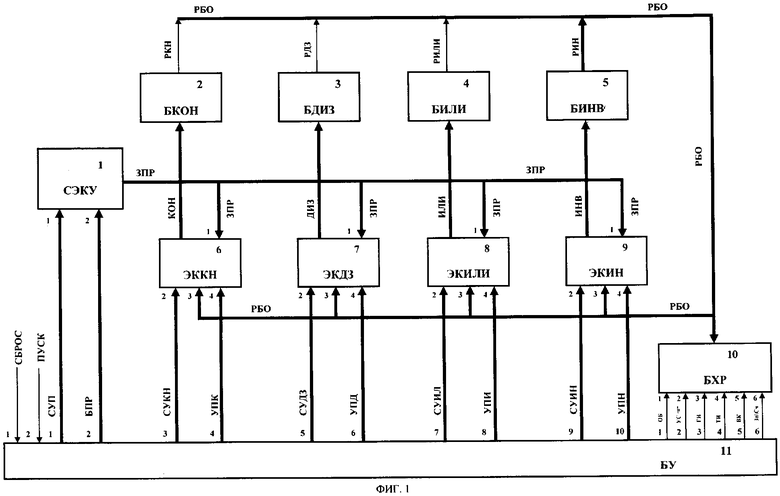

Решение задачи осуществляется тем, что устройство выполнения логических операций, содержащее элементы исключающее ИЛИ, отличающее тем, что дополнительно введены: система электронных ключей, блок конъюнкторов, блок дизъюнкторов, блок инверторов, электронные ключи конъюнкторов, электронные ключи дизъюнкторов, электронные ключи операции исключающее ИЛИ, электронные ключи инверторов, блок хранения результатов, блок управления, причем первый и второй информационные выходы блока управления соединены соответственно с первым и вторым информационными входами системы электронных ключей, информационный выход которой соединен с первым информационным входом электронных ключей конъюнкторов, с первым информационным входом электронных ключей дизъюнкторов, с первым информационным входом электронных ключей операции исключающее ИЛИ, с первым информационным входом электронных ключей инверторов, третий и четвертый информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей конъюнкторов, пятый и шестой информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей дизъюнкторов, седьмой и восьмой информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей операции исключающее ИЛИ, девятый и десятый информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей инверторов, с первого по шестой управляющие выходы блока управления соединены соответственно с первым по шестой управляющими входами блока хранения результата, информационный выход электронных ключей конъюнкторов соединен с информационным входом блока конъюнкторов, информационный выход электронных ключей дизъюнкторов соединен с информационным входом блока дизъюнкторов, информационный выход электронных ключей операции исключающее ИЛИ соединен с информационным входом блока операции исключающее ИЛИ, информационный выход электронных ключей инверторов соединен с информационным входом блока инверторов, управляющий выход блока конъюнкторов, управляющий выход блока дизъюнкторов, управляющий выход блока операции исключающее ИЛИ, информационный выход блока инверторов соединены с информационным входом блока хранения результата, с третьим информационным входом электронных ключей инверторов, с третьим информационным входом электронных ключей операции исключающее ИЛИ, с третьим информационным входом электронных ключей дизъюнкторов, с третьим информационным входом электронных ключей конъюнкторов, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства выполнения логических операций.

СЭКУ - система электронных ключей устройства служит для разрешения подачи переменных и управляющих сигналов из блока управления на входы блоков, выполняющих логические операции.

БКОН - блок конъюнкторов служит для выполнения логической операции конъюнкции над входными переменными.

БДИ3 - блок дизъюнкторов служит для выполнения логической операции дизъюнкции над входными переменными.

БИЛИ - блок операции исключающее ИЛИ служит для выполнения логической операции исключающее ИЛИ над входными переменными.

БИНВ - блок инверторов служит для выполнения логической операции инверсии над входными переменными.

ЭККН - электронные ключи конъюнкторов служат для разрешения передачи переменных в блок конъюнкторов для выполнения логической операции конъюнкции.

ЭКДЗ - электронные ключи дизъюнкторов служат для разрешения передачи переменных в блок дизъюнкторов для выполнения логической операции дизъюнкции.

ЭКИЛИ - электронные ключи операции исключающее ИЛИ служат для разрешения передачи переменных в блок операции исключающее ИЛИ для выполнения логической операции исключающее ИЛИ.

ЭКИН - электронные ключи инверторов служат для разрешения передачи переменных в блок инверторов для выполнения логической операции инверсии.

БХР - блок хранения результатов служит для записи и хранения в нем результатов выполнения логических операций.

БУ - блок управления служит для генерации управляющих сигналов устройства.

Любая булева функция может быть представлена аналитически одной из нормальных форм: дизъюнктивной (СДНФ) и конъюнктивной (СКНФ). Для СДНФ и СКНФ такими функциями являются: конъюнкция, дизъюнкция, отрицание (инверсия). Существуют системы булевых функций, с помощью которых можно аналитически представить любую сколь угодно сложную булеву функцию. Функционально полной системой булевых функций называется совокупность таких булевых функций f1, f2, ..., fn, что произвольная булева функция может быть записана в виде формы через функции этой совокупности. К функционально полной системе булевых функций следует отнести системы: логическая И, логическая ИЛИ, отрицание НЕ, исключающее ИЛИ, т.е. конъюнкция (&), дизъюнкция (V), инверсия (НЕ), исключающее ИЛИ (⊕) [1]. Для примера следует задать булеву функцию аналитическим способом.

F=((X1&X2& )VX4)⊕

)VX4)⊕

Для ее реализации необходимо выполнить ряд последовательных операций в определенном порядке:

1) определить инверсное значение переменной Х3,

2) выполнить логическую операцию конъюнкцию над переменными X1, Х2 и инверсным значением переменной Х3.

3) выполнить логическую операцию дизъюнкцию над результатом операции конъюнкции переменных X1, Х2 инверсным значением Х3 и переменной Х4,

4) определить инверсное значение переменной Х5,

5) выполнить логическую операцию исключающее ИЛИ над результатом операции дизъюнкции Х4 и конъюнкции переменных X1, Х2, инверсным значением Х3 и инверсным значением переменной Х5,

6) результаты выполнения логических операций записать в оперативное запоминающее устройство.

В устройстве выполнения логических операций последовательность выполнения булевых функций определяется установкой управляющих сигналов на входах электронных ключей в единичное состояние. Тем самым отпираются соответствующие ключи и через их, значения переменных, и ранее полученные результаты других блоков, поступают на входы очередного блока устройства.

На фиг.1 изображена структурная схема устройства, выполняющего логические операции.

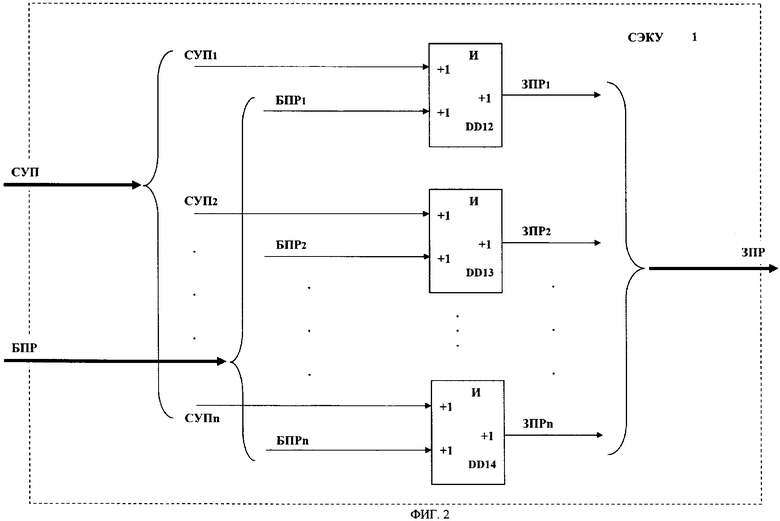

На фиг.2 представлен вариант технической реализации системы электронных ключей устройства.

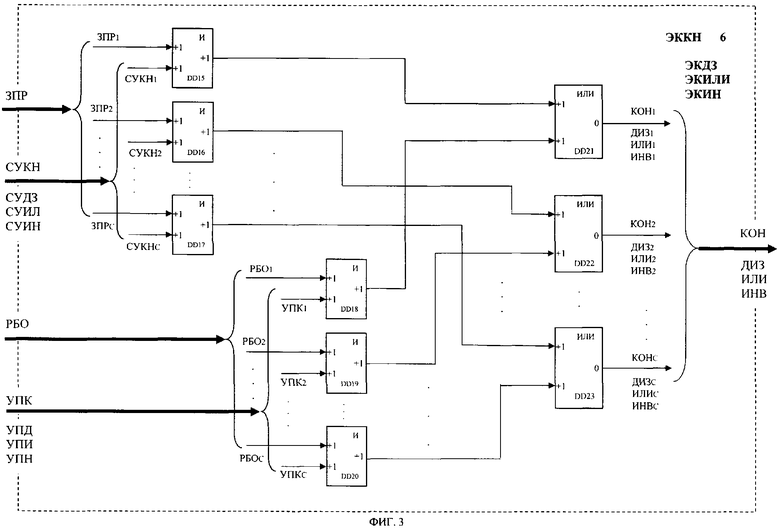

На фиг.3 изображена функциональная схема блоков электронных ключей: конъюнкторов, дизъюнкторов, операции исключающее ИЛИ, инверторов, которые имеют одинаковую структуру, выполняют аналогичные функции и состоят из одинаковых электронных элементов.

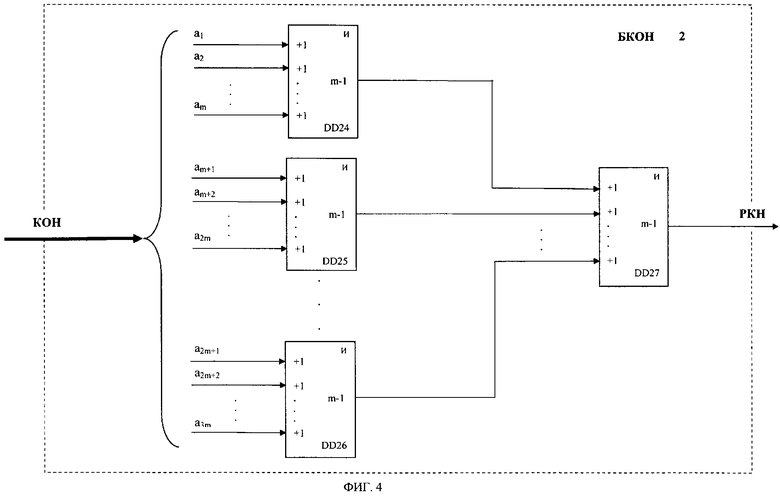

На фиг.4 представлен вариант технической реализации блока конъюнкторов устройства.

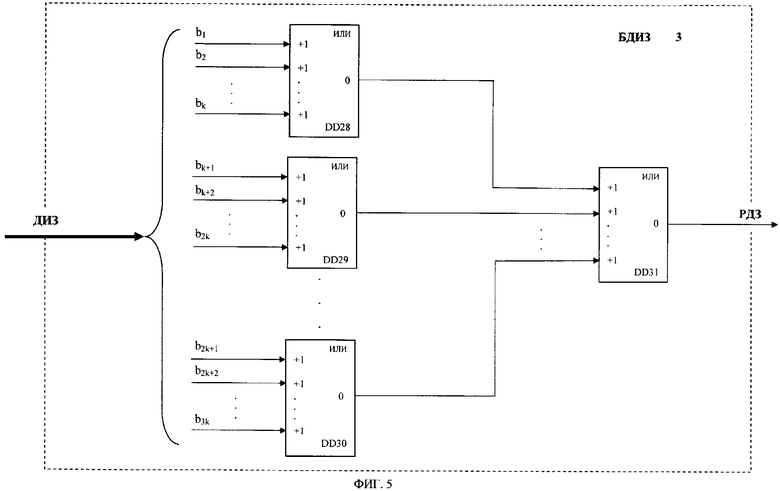

На фиг.5 представлен вариант технической реализации блока дизъюнкторов устройства.

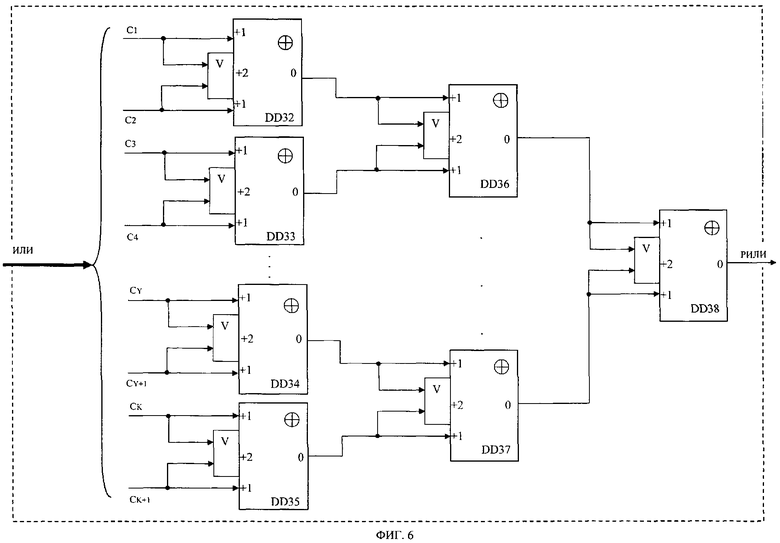

На фиг.6 представлен вариант технической реализации блока операции исключающее ИЛИ устройства.

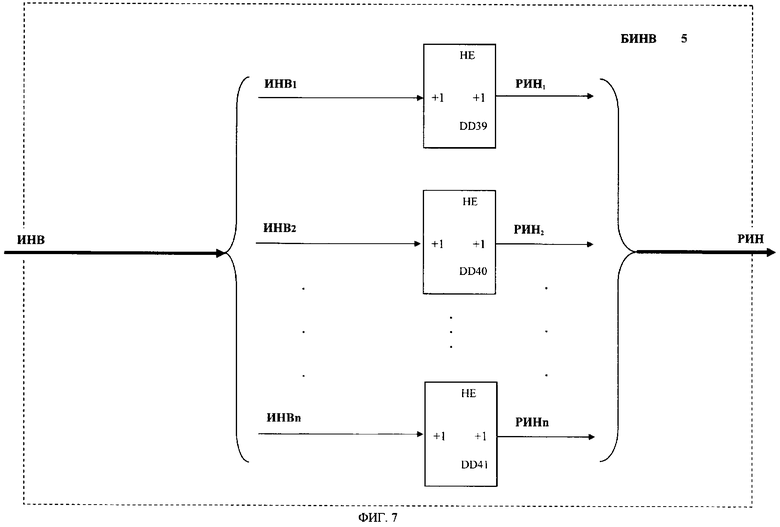

На фиг.7 представлен вариант технической реализации блока инверторов устройства.

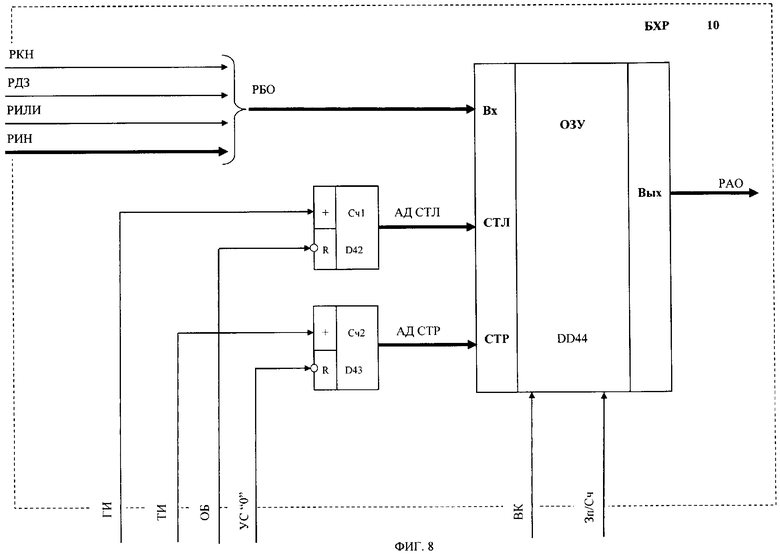

На фиг.8 представлен вариант технической реализации блока хранения результата и структуры информационного, входного сигнала в ОЗУ-РБО.

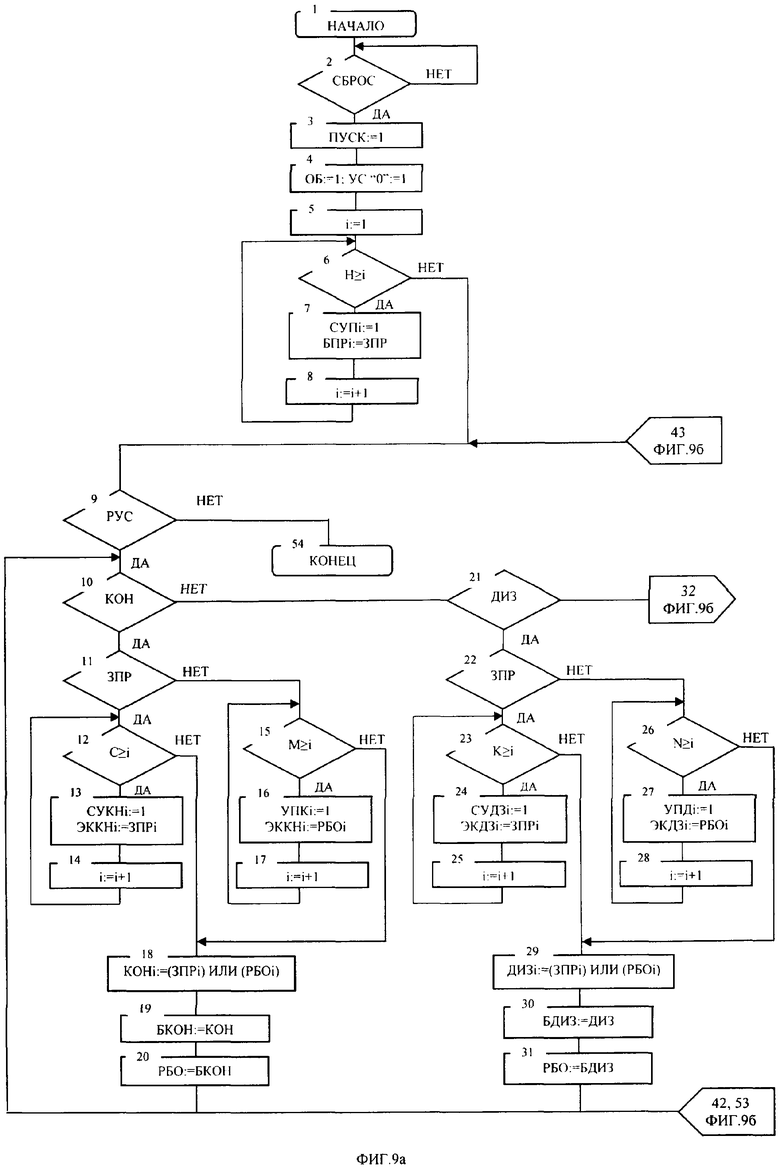

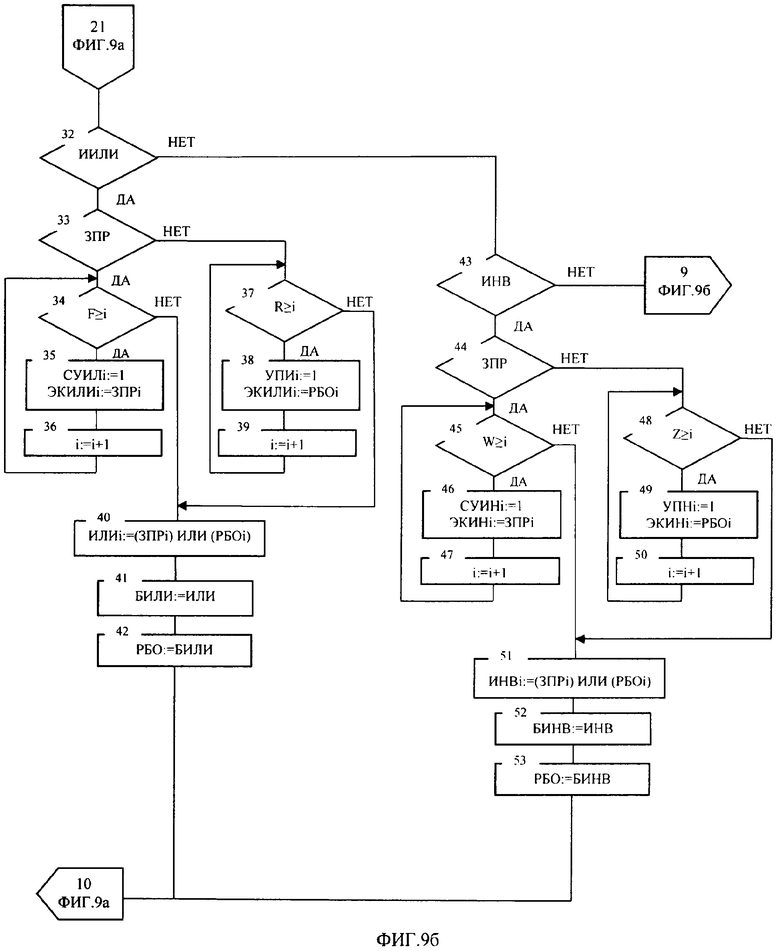

На фиг.9а, 9б - содержательная ГСА работы устройства.

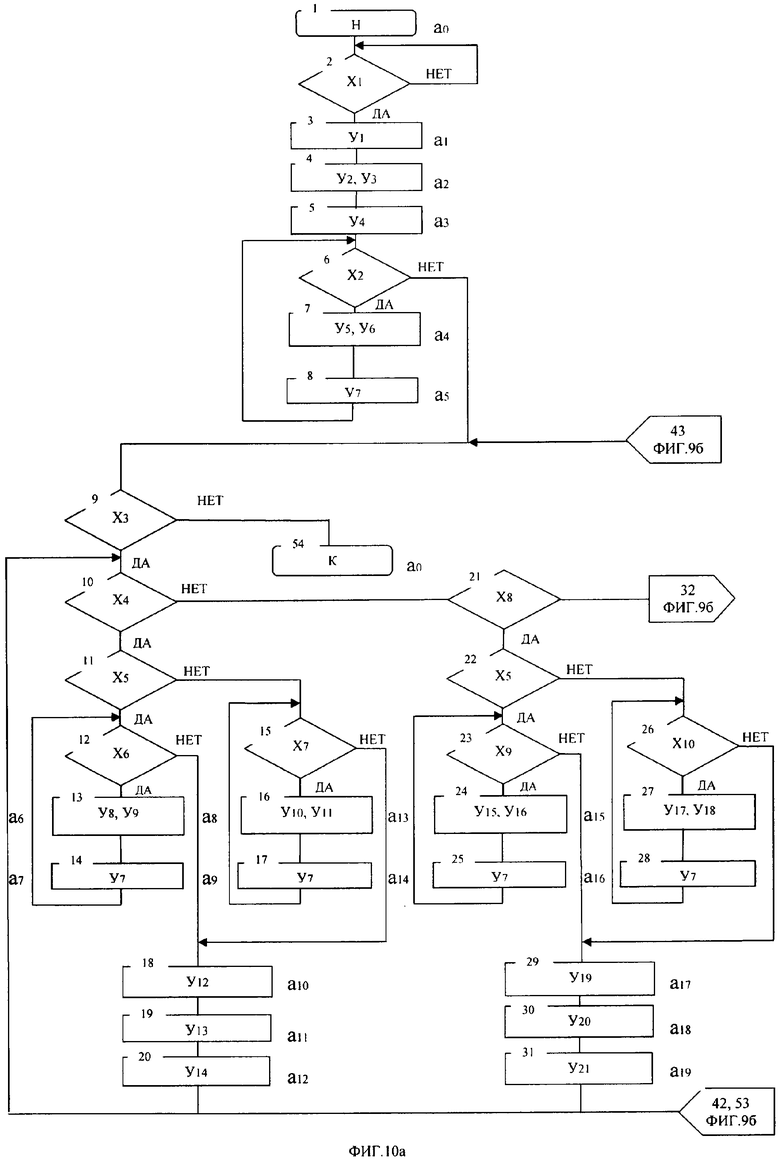

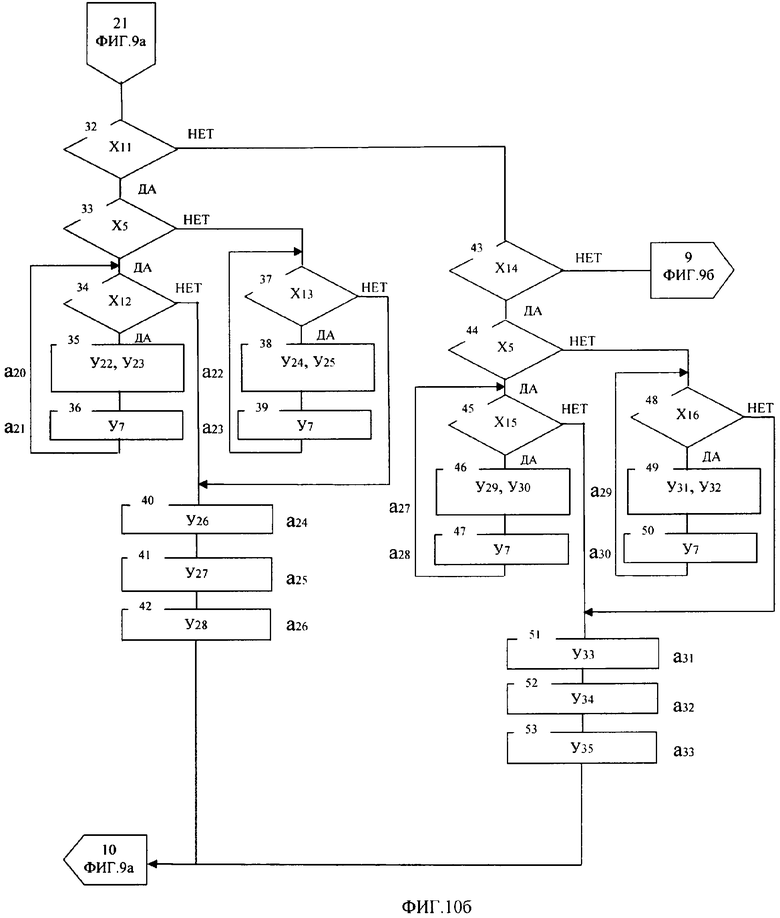

На фиг.10а, 10б - размеченная ГСА работы устройства.

Устройство выполнения логических операций (фиг.1) содержит: систему электронных ключей, блок конъюнкторов, блок дизъюнкторов, блок операции исключающее ИЛИ, блок инверторов, электронные ключи конъюнкторов, электронные ключи дизъюнкторов, электронные ключи операции исключающее ИЛИ, электронные ключи инверторов, блок хранения результатов, блок управления, пороговые элементы, нейроны.

Для описания алгоритма работы блока 11 управления используются следующие идентификаторы.

1. СЭКУ - система электронных ключей устройства.

2. БКОН - блок конъюнкторов.

3. БДИЗ - блок дизъюнкторов.

4. БИЛИ - блок операции исключающее ИЛИ.

5. БИНВ - блок инверторов.

6. ЭККН - электронные ключи конъюнкторов.

7. ЭКДЗ - электронные ключи дизъюнкторов.

8. ЭКИЛИ - электронные ключи операции исключающее ИЛИ.

9. ЭКИН - электронные ключи инверторов.

10. БХР - блок хранения результатов.

11. БУ - блок управления.

12. СУП - сигналы управления, поступающие из блока управления.

13. СУПi - активный сигнал управления.

14. БПР - булевы переменные, поступающие из блока управления.

15. БПРi - определенная булева переменная, имеющая нуль, единичное значение.

16. ЗПР - информационный сигнал, в структуру которого входят определенные значения булевых переменных.

17. КОН - булевы переменные, над которыми нужно выполнить устройством операцию конъюнкции.

18. ДИЗ - булевы переменные, над которыми нужно выполнить операцию дизъюнкции.

19. ИЛИ - булевы переменные, над которыми нужно выполнить операцию исключающее ИЛИ.

20. ИНВ - булевы переменные, над которыми нужно выполнить операцию инверсии.

21. СУКН - сигналы управления, поступающие на управляющие входы электронных ключей конъюнкторов.

22. СУКНi - активный сигнал управления, поступающий на управляющий вход электронных ключей конъюнкторов.

23. СУДЗ - сигналы управления, поступающие на управляющие входы электронных ключей дизъюнкторов.

24. СУЗДЗi - активный сигнал управления, поступающий на управляющий вход электронных ключей дизъюнкторов.

25. СУИЛ - сигналы управления, поступающие на управляющие входы электронных ключей операции исключающее ИЛИ.

26. СУИЛi - активный сигнал управления, поступающий на управляющий вход электронных ключей операции исключающее ИЛИ.

27. СУИН - сигналы управления, поступающие на управляющие входы электронных ключей инверторов.

28. СУИНi - активный сигнал управления, поступающий на управляющий вход электронных ключей инверторов.

29. УПК - управляющие сигналы, поступающие на управляющие входы электронных ключей конъюнкторов.

30. УПКi - активный управляющий сигнал, поступающий на управляющий вход электронных ключей конъюнкторов.

31. УПД - управляющие сигналы, поступающие на управляющие входы электронных ключей дизъюнкторов.

32. УПДi - активный управляющий сигнал, поступающий на управляющий вход электронных ключей дизъюнкторов.

33. УПИ - управляющие сигналы, поступающие на управляющие входы электронных ключей операции исключающее ИЛИ.

34. УПИi - активный управляющий сигнал, поступающий на управляющий вход электронных ключей операции исключающее ИЛИ.

35. УПН - управляющие сигналы, поступающие на управляющие входы электронных ключей инверторов.

36. УПНi - активный управляющий сигнал, поступающий на управляющий вход электронных ключей инверторов.

37. РКН - результат выполнения операции конъюнкции блоком конъюнкторов.

38. РДЗ - результат выполнения операции дизъюнкции блоком дизъюнкторов.

39. РИЛИ - результат выполнения операции суммы по модулю два блоком исключающее ИЛИ.

40. РИН - результат получения инверсных значений булевых переменных блоком инверторов.

41. ОБ - команда обнуления двоичного счетчика Сч 1 DD 42 блока хранения результата.

42. УС "0" - команда обнуления двоичного счетчика Сч 2 DD 43 блока хранения результата.

35. ГИ - генератор импульсов, поступающий из блока управления на суммирующий вход (+) двоичного счетчика Сч 1 DD 42 блока хранения результата.

36. ТИ - тактовые импульсы, поступающие из блока управления на суммирующий вход (+) двоичного счетчика Сч 2 DD 43 блока хранения результата.

43. ВК - команда выбора кристалла оперативного запоминающего устройства ОЗУ блока хранения результата.

44. Сч/Зп - команда считывания/записи оперативного запоминающего устройства ОЗУ блока хранения результата.

45. РБО - информационный вход блока хранения результата. В структуру этого информационного сигнала входят: РКН - результат выполнения операции конъюнкции блоком конъюнкторов, РДЗ - результат выполнения операции дизъюнкции блоком дизъюнкторов, РИЛИ - результат выполнения операции суммы по модулю два блоком исключающее ИЛИ, РИН - результат получения инверсных значений булевых переменных блоком инверторов.

46. СБРОС - сигнал сброса (обнуление) элементов памяти устройства выполнения логических операций.

47. ПУСК - сигнал начало работы устройства.

Работа блока управления устройства выполнения логических операций.

Содержательная ГСА управления приведена на фиг.9а и фиг.9б и отражает работу блока управления (фиг.1).

В блоке 2 алгоритма осуществляется подача сигнала установки в нулевое состояние - СБРОС на входы всех элементов устройства.

В блоке 3 алгоритма происходит установка сигнала - пуск в единичное значение ПУСК:=1.

В блоке 4 алгоритма по командам: ОБ:=1, УС "0":=1 происходит установка в нулевое значение двоичных счетчиков Сч 1 и Сч 2 блока 10 хранения результатов, формирующих адреса строк и столбцов оперативного запоминающего устройства (фиг.8).

В блоке 5 алгоритма по команде i:=1 текучее значение счетчика, определяющее количество логических переменных, устанавливается в единичное значение.

Блоки 6, 7 и 8 образуют цикл, в котором определяется количество переменных, а также присваиваются значения переменным, равным нулю или единице (фиг.2).

В блоке 6 алгоритма анализируется переменная Н, определяющая количество булевых переменных. Если текущее значение счетчика переменных i меньше значения Н, Н≥i, то происходит переход из блока 6 по выходу ДА на блок 7 алгоритма. По выходу НЕТ осуществляется переход на блок 9 алгоритма.

В блоке 7 алгоритма по команде СУПi:=1 происходит подача единичных значений на управляющие входы схем И для отпирания соответствующих электронных ключей (фиг.2). Количество управляющих сигналов СУПi зависит от числа введенных переменных в блоке управления. По команде БПРi=ЗПР каждой булевой переменной присваивается значение, равное нулевому или единичному уровню (фиг.2).

В блоке 8 алгоритма по команде i:=i+1 к текущему значению счетчика i переменных прибавляется единичное значение.

В результате выполнения этого цикла будут определены булевы переменные, присвоены им значения и записана булева функция в аналитическом виде, которую необходимо реализовать устройством.

В блоке 9 алгоритма анализируется признак работы устройства - РУС. Если устройство работает - выход ДА блока, то при этом осуществляется переход на блок 10 алгоритма. Если работа устройства завершена - выход НЕТ блока, осуществляется переход на конечный блок 54 алгоритма.

В блоке 10 алгоритма проверяется признак выполнения устройством логической операции конъюнкции (И) - КОН. Если устройство выполняет не эту функцию - выход НЕТ блока, то осуществляется переход на блок 21 алгоритма. Если выполняется логическая операция конъюнкция (И) - выход ДА, то осуществляется переход на блок 11 алгоритма.

В блоке 11 алгоритма происходит анализ признака - значение переменных ЗПР. Этот признак означает то, что блок конъюнкторов работает с первоначально заданными значениями переменных или уже с результатом работы других блоков устройства. Если блок конъюнкторов работает с результатом работы других блоков - выход НЕТ, то осуществляется переход на блок 15 алгоритма. Если блок выполняет операцию конъюнкции с первоначально заданными переменными, то осуществляется переход на блок 12 алгоритма (фиг.1, 3).

Блоки 12, 13 и 14 формируют цикл, в котором выполняется операция конъюнкции над булевыми переменными, поступившими на вход блока конъюнкторов (фиг.4).

В блоке 12 алгоритма анализируется признак - количество булевых переменных С и текущее значение счетчика i, C≥i. Если операция конъюнкции выполнена блоком конъюнкторов над всеми переменными, то осуществляется переход на блок 18 алгоритма. Если происходит выполнение операции конъюнкции блоком конъюнкторов над булевыми переменными, то осуществляется переход на блок 13 алгоритма.

В блоке 13 алгоритма по команде СУКНi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 6 электронные ключи конъюнкторов для отпирания схем. По команде ЭККНi:=ЗПРi происходит подача на информационные входы схем И значений переменных - ЗПР для выполнения логической операции И (фиг.3).

В блоке 14 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 12 алгоритма для выполнения циклических операций блоков 12, 13 и 14 алгоритма.

Блоки 15, 16 и 17 формируют цикл, в котором выполняется операция конъюнкции над результатами, поступившими с выходов других блоков устройства (фиг.1).

В блоке 15 алгоритма анализируется признак - количество булевых переменных М и текущее значение счетчика i, M≥i. Если операция конъюнкции выполнена блоком конъюнкторов над всеми результатами других блоков устройства, поступившими на вход блока 2, то осуществляется переход на блок 18 алгоритма. Если происходит выполнение операции конъюнкции блоком 2 конъюнкторов над результатами, то осуществляется переход на блок 16 алгоритма.

В блоке 16 алгоритма по команде УПКi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 6 электронные ключи конъюнкторов для отпирания логических схем. По команде ЗККНi:=РБОi происходит подача на информационные входы схем И результатов выполнения других блоков устройства - РБО для выполнения логической операции И (фиг.3).

В блоке 17 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 15 алгоритма для выполнения операций блоков 15, 16 и 17 алгоритма.

В блоке 18 алгоритма по команде KOHi:=(ЗПРi) ИЛИ (РБОi) происходит подача результата логической операции ИЛИ значений переменных - ЗПР или результата выполнения другими блоками устройства - РБО (фиг.3).

В блоке 19 по команде БКОН:=КОН осуществляется подача информационного сигнала КОН с выходов блока 6 электронные ключи конъюнкторов на вход блока 2 конъюнкторов (фиг.4).

В блоке 20 алгоритма по команде РБО:=БКОН выходная шина устройства РБО принимает значение операции конъюнкции с выхода блока 2 конъюнкторов (фиг.1). По выходу этого блока осуществляется переход на блок 10 алгоритма.

В блоке 21 алгоритма проверяется признак выполнения устройством логической операции дизъюнкции (ИЛИ) - ДИЗ. Если устройство выполняет другую функцию - выход НЕТ блока, то осуществляется переход на блок 32 алгоритма. Если устройством выполняется логическая операция дизъюнкция (ИЛИ) - выход ДА, то осуществляется переход на блок 22 алгоритма.

В блоке 22 алгоритма происходит анализ признака - значение переменных ЗПР. Этот признак означает то, что блок дизъюнкции работает с первоначально заданными значениями переменных или уже с результатом работы других блоков устройства. Если блок дизъюнкторов работает с результатом работы других блоков - выход НЕТ, то осуществляется переход на блок 26 алгоритма. Если блок выполняет операцию дизъюнкции с первоначально заданными переменными, то осуществляется переход на блок 23 алгоритма (фиг.1, 3, 5).

Блоки 23, 24 и 25 формируют цикл, в котором выполняется операция дизъюнкции над булевыми переменными, поступившими на вход блока дизъюнкторов (фиг.5).

В блоке 23 алгоритма анализируется признак - количество булевых переменных К и текущее значение счетчика i, K≥i. Если операция дизъюнкции выполнена блоком дизъюнкторов над всеми переменными, то осуществляется переход на блок 29 алгоритма. Если происходит выполнение операции дизъюнкции блоком дизъюнкторов над булевыми переменными, то осуществляется переход на блок 24 алгоритма.

В блоке 24 алгоритма по команде СУДЗi=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 7 электронные ключи дизъюнкторов для отпирания электронных схем. По команде ЭКДЗi:=ЗПРi происходит подача на информационные входы схем И значений переменных - ЗПР для выполнения логической операции ИЛИ (фиг.3, 5).

В блоке 25 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 23 алгоритма для выполнения циклических операций блоков 23, 24 и 25 алгоритма.

Блоки 26, 27, 28 формируют цикл, в котором выполняется операция дизъюнкции над результатами, поступившими с выходов других блоков устройства (фиг.1, 5).

В блоке 26 алгоритма анализируется признак - количество булевых переменных N и текущее значение счетчика i, N≥i. Если операция дизъюнкции выполнена блоком дизъюнкторов над всеми результатами других блоков устройства, поступившими на вход блока 3, то осуществляется переход на блок 29 алгоритма. Если происходит выполнение операции дизъюнкции блоком 3 дизъюнкторов над результатами, то осуществляется переход на блок 27 алгоритма.

В блоке 27 алгоритма по команде УПДi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 7 электронные ключи дизъюнкторов для отпирания логических схем. По команде ЭКДЗi:=РБОi происходит подача на информационные входы схем И результатов выполнения других блоков устройства - РБО для выполнения логической операции ИЛИ (фиг.3, 5).

В блоке 28 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 26 алгоритма для выполнения операций блоков 26, 27 и 28 алгоритма.

В блоке 29 алгоритма по команде ДИЗi:=(ЗПРi) ИЛИ (РБОi) происходит подача результата логической операции дизъюнкции значений переменных - ЗПР или результата выполнения другими блоками устройства - РБО (фиг.3).

В блоке 30 по команде БДИЗ:=ДИЗ осуществляется подача информационного сигнала ДИЗ с выходов блока 7 электронные ключи дизъюнкторов на вход блока 3 дизъюнкторов (фиг.1, 5).

В блоке 31 алгоритма по команде РБО:=БДИЗ выходной информационный сигнал устройства - РБО принимает значение операции дизъюнкции с выхода блока 3 дизъюнкторов (фиг.1). По выходу из блока 31 осуществляется переход на вход блока 10 алгоритма.

В блоке 32 алгоритма проверяется признак выполнения устройством логической операции исключающее ИЛИ - ИИЛИ. Если устройству задано выполнять другую функцию - выход НЕТ блока, то осуществляется переход на блок 43 алгоритма. Если устройством выполняется логическая операция исключающее ИЛИ - выход ДА, то осуществляется переход на блок 33 алгоритма.

В блоке 33 алгоритма анализируется признак ЗПР - значение переменных. Этот признак означает то, что блок операции исключающее ИЛИ работает с первоначально заданными значениями переменных или уже с результатом работы других блоков устройства. Если блок операции исключающее ИЛИ работает с результатом работы других блоков - выход НЕТ, то осуществляется переход на блок 37 алгоритма. Если блок выполняет операцию исключающее ИЛИ с первоначально заданными переменными, то осуществляется переход на блок 34 алгоритма (фиг.1, 3, 6).

Блоки 34, 35 и 36 формируют цикл, в котором выполняется операция исключающее ИЛИ над булевыми переменными, поступившими на вход блока операции исключающее ИЛИ (фиг.6).

В блоке 34 алгоритма анализируется признак F - количество булевых переменных и текущее значение счетчика i, F≥i. Если операция исключающее ИЛИ выполнена блоком операции исключающее ИЛИ над всеми переменными, то осуществляется переход на блок 40 алгоритма. Если происходит выполнение операции исключающее ИЛИ блоком операции исключающее ИЛИ над булевыми переменными, то осуществляется переход на блок 35 алгоритма.

В блоке 35 алгоритма по команде СУИЛi=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 8 электронные ключи операции исключающее ИЛИ для отпирания электронных схем. По команде ЭКИЛИi:=ЗПРi происходит подача на информационные входы схем И значений переменных - ЗПР для выполнения логической операции исключающее ИЛИ (фиг.3, 6).

В блоке 36 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единичное значение. По выходу из этого блока осуществляется переход на блок 34 алгоритма для выполнения циклических операций блоков 34, 35 и 36 алгоритма.

Блоки 37, 38 и 39 формируют цикл, в котором выполняется операция исключающее ИЛИ над результатами, поступившими с выходов других блоков устройства (фиг.1, 6).

В блоке 37 алгоритма анализируется признак - количество булевых переменных R и текущее значение счетчика i, R≥i. Если операция исключающее ИЛИ выполнена блоком операции исключающее ИЛИ над всеми результатами других блоков устройства, поступившими на вход блока 4, то осуществляется переход на блок 40 алгоритма. Если происходит выполнение операции исключающее ИЛИ блоком 4 операции исключающее ИЛИ над результатами, выполненными другими блоками, то осуществляется переход на блок 38 алгоритма.

В блоке 38 алгоритма по команде УПИi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 8 электронные ключи операции исключающее ИЛИ для отпирания логических схем. По команде ЭКИЛИi:=РБОi происходит подача на информационные входы открытых схем И результатов, выполненных другими блоками устройства - РБО для выполнения логической операции исключающее ИЛИ (фиг.3, 6).

В блоке 39 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 37 алгоритма для выполнения операций блоков 37, 38 и 39 алгоритма.

В блоке 40 алгоритма по команде ИЛИi:=(ЗПРi) ИЛИ (РБОi) происходит подача результата логической операции исключающее ИЛИ значений переменных - ЗПР или результата выполнения другими блоками устройства - РБО (фиг.3).

В блоке 41 по команде БИЛИ:=ИЛИ осуществляется подача информационного сигнала ИЛИ с выходов блока 8 электронные ключи операции исключающее ИЛИ на вход блока 4 операции исключающее ИЛИ (фиг.1, 6).

В блоке 42 алгоритма по команде РБО:=БИЛИ выходной информационный сигнал устройства - РБО принимает значение операции исключающее ИЛИ с выхода блока 4 операции исключающее ИЛИ (фиг.1). По выходу из блока 42 осуществляется переход на вход блока 10 алгоритма.

В блоке 43 алгоритма проверяется признак выполнения устройством логической операции инверсии (НЕ) - ИНВ. Если устройство выполняет не эту функцию - выход НЕТ блока, то осуществляется переход на блок 9 алгоритма. Если выполняется логическая операция инверсия (НЕ) - выход ДА, то осуществляется переход на блок 44 алгоритма.

В блоке 44 алгоритма происходит анализ признака - значение переменных ЗПР. Этот признак означает то, что блок инверторов работает с первоначально заданными значениями переменных или уже с результатом работы других блоков устройства. Если блок инверторов работает с результатом работы других блоков - выход НЕТ, то осуществляется переход на блок 48 алгоритма. Если блок выполняет логическую операцию инверсию с первоначально заданными переменными, то осуществляется переход на блок 45 алгоритма (фиг.1, 3).

Блоки 45, 46 и 47 формируют цикл, в котором выполняется операция инверсия над булевыми переменными, поступившими на вход блока 5 инверторов (фиг.1, 7).

В блоке 45 алгоритма анализируется признак - количество булевых переменных W и текущее значение счетчика i, W≥i. Если операция инверсия выполнена блоком инверторов над всеми переменными, то осуществляется переход на блок 51 алгоритма. Если происходит выполнение операции инверсии блоком инверторов над булевыми переменными, то осуществляется переход на блок 46 алгоритма.

В блоке 46 алгоритма по команде СУИНi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 9 электронные ключи инверторов для отпирания схем. По команде ЭКИНi:=ЗПРi происходит подача на информационные входы схем И значений переменных - ЗПР для выполнения логической операции отрицания (НЕ) (фиг.3).

В блоке 47 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 45 алгоритма для выполнения циклических операций блоков 45, 46 и 47 алгоритма.

Блоки 48, 49 и 50 формируют цикл, в котором выполняется операция инверсия над результатами, поступившими с выходов других блоков устройства (фиг.1, 7).

В блоке 48 алгоритма анализируется признак - количество булевых переменных Z и текущее значение счетчика i, Z≥i. Если операция инверсия выполнена блоком инверторов над всеми результатами других блоков устройства, поступившими на вход блока 5, то осуществляется переход на блок 51 алгоритма. Если происходит выполнение операции инверсии блоком 5 инверторов над результатами, то осуществляется переход на блок 49 алгоритма.

В блоке 49 алгоритма по команде УПНi:=1 происходит подача единичных значений на управляющие входы соответствующих логических схем И блока 9 электронные ключи конъюнкторов для отпирания логических схем. По команде ЭКИНi:=РБОi происходит подача на информационные входы схем И результатов выполнения других блоков устройства - РБО для выполнения логической операции инверсии (НЕ) (фиг.3).

В блоке 50 алгоритма по команде i:=i+1 осуществляется увеличение текущего значения счетчика i на единицу. По выходу из этого блока осуществляется переход на блок 48 алгоритма для выполнения операций блоков 48, 49 и 50 алгоритма.

В блоке 51 алгоритма по команде ИНВi:=(ЗПРi) ИЛИ (РБОi) происходит подача результата логической операции ИЛИ значений переменных - ЗПР или результата выполнения другими блоками устройства - РБО (фиг.3).

В блоке 52 по команде БИНВ:=ИНВ осуществляется подача информационного сигнала ИНВ с выходов блока 9 электронные ключи инверторов на вход блока 5 инверторов (фиг.7).

В блоке 53 алгоритма по команде РБО:=БИНВ выходная шина устройства РБО принимает значение операции инверсии с выхода блока 5 инверторов (фиг.1). По выходу этого блока осуществляется переход на блок 10 алгоритма.

Блок 54 алгоритма является конечным.

Работа устройства выполнения логических операций заключается в следующем.

Внешние управляющие сигналы "СБРОС" и "ПУСК" поступают в блок 11 управления.

Устройство выполнения логических операций над булевыми переменными выполняет логические операции: конъюнкцию (И), дизъюнкцию (ИЛИ), исключающее ИЛИ (⊕), инверсию (НЕ). Эти функции являются функционально полными базисами. Это означает, что булеву функцию любой сложности можно записать и выполнить с помощью перечисленных функций.

Блок 1 система электронных ключей устройства - СЭКУ содержит систему логических элементов И с тремя высоко идемпотентными состояниями, выполненных на пороговых элементах: DD 12, DD 13, DD 14 (фиг.2). Этот блок служит для разрешения передачи логических переменных из блока управления на входы блоков устройства для выполнения над ними логических операций. На вход системы электронных ключей поступают информационные сигналы: СУП - сигналы управления и БПР - булевы переменные. На входы пороговых элементов блока поступают информационные сигналы - БПРi, равные нулю или единице, и управляющие сигналы - СУПi, значение которых равны нулю или единице. Количество и значение булевых переменных БПРn задаются в блоке 11 управления. Булева переменная БПРi, где 1≤i≤n, поступает на один из входов порогового элемента. На второй вход этого порогового элемента поступает сигнал управления СУП1, где 1≤i≤n, из блока 11 управления. При единичном значении сигнала управления СУПi на выходе соответствующего i-ого порогового элемента будет значение булевой переменной БПРi, в этом случае будет равенство ЗПРi:=БПРi. Если сигнал управления СУП будет равен нулевому значению, то соответствующая логическая схема И блока будет заперта, на выходе которой будет большое сопротивление для отключения этих элементов от других блоков устройства (фиг.2).

Блок 2 конъюнкторов - БКОН содержит m пороговых элементов. На фигуре показаны пороговые элементы: DD 24, DD 25, DD 26, DD 27, выполняющие логическую функцию конъюнкцию над логическими переменными (фиг.4). Входным сигналом блока является информационный сигнал КОН, который поступает с выхода блока 6 ЭККН электронные ключи конъюнкторов (фиг.1, 4). Блок 2 конъюнкторов имеет пирамидальную структуру. Входы a1...а3m поступают на входы пороговых элементов: DD 24, DD 25, DD 26. Выходы этих элементов поступают на вход порогового элемента DD 27 (фиг.4). Выходным сигналом блока 2 конъюнкторов является сигнал РКН - результат конъюнкции, формирующийся с выхода порогового элемента DD 27 (фиг.4).

Блок 3 дизъюнкторов - БДИЗ содержит k пороговых элементов. На фигуре показаны пороговые элементы: DD 28, DD 29, DD 30, DD 31, выполняющие логическую функцию дизъюнкцию над входными логическими переменными (фиг.5). Входным сигналом блока является информационный сигнал ДИЗ, который поступает с выхода блока 7 ЭКДЗ - электронные ключи дизъюнкторов (фиг.1, 5). Блок 3 дизъюнкторов имеет пирамидальную структуру. Входы b1...b3k поступают на входы пороговых элементов: DD 28, DD 29, DD 30. Выходы этих элементов поступают на вход порогового элемента DD 31 (фиг.5). Выходным сигналом блока 3 дизъюнкторов является сигнал РДЗ - результат дизъюнкции, формирующийся с выхода порогового элемента DD 31 (фиг.5).

Блок 4 исключающее ИЛИ - БИЛИ содержит f нейронов. На фигуре показаны нейроны: DD 32, DD 33, DD 34, DD 35, DD 36, DD 37, DD 38, выполняющие логическую функцию исключающее ИЛИ над входными логическими переменными (фиг.6). Входным сигналом блока является информационный сигнал ИЛИ, который поступает с выхода блока 8 ЭКИЛИ - электронные ключи операции исключающее ИЛИ (фиг.1, 6). Блок 4 исключающее ИЛИ имеет пирамидальную структуру. Входы c1...cw+1 поступают на входы нейронов: DD 32, DD 33, DD 34, DD 35. Выходы этих элементов поступают на входы нейронов DD 36 и DD 37 соответственно (фиг.6). Выходы этих нейронов поступают на входы нейрона DD 38. Выходным сигналом блока 4 БИЛИ является результат выполнения операции исключающее ИЛИ - РИЛИ, полученный на выходе нейрона DD 38 (фиг.6).

Блок 5 инверторов - БИНВ содержит систему логических элементов НЕ - инверторов, выполненных на пороговых элементах: DD 39, DD 40, DD 41 (фиг.7). Этот блок служит для получения инверсных состояний переменных. Входным сигналом блока 5 является информационный сигнал ИНВ, поступающий с выхода блока 9 ЭКИН - электронные ключи инверторов. Каждая переменная ИНВi поступает на вход соответствующего инвертора - схемы НЕ (фиг.7). На выходе каждого инвертора блока формируется инверсный сигнал - РИНi, ИНВi:= . Выходным сигналом блока 5 инверторов является информационный сигнал РИН (фиг.1, 7).

. Выходным сигналом блока 5 инверторов является информационный сигнал РИН (фиг.1, 7).

Блок 6 электронные ключи конъюнкторов содержит систему электронных ключей, построенную на электронных ключах: DD 15, DD 16, DD 17. На информационные входы этой системы поступают сигналы ЗПР - значения переменных, и на управляющие входы поступают сигналы СУКН - сигналы управления электронными ключами конъюнкторов. В состав блока входит система электронных ключей, выполненных на элементах: DD 18, DD 19 и DD 20. На информационные входы этой системы поступают сигналы РБО - результаты выполнения логических операций другими блоками, на управляющие входы поступают сигналы УПК - управляющие сигналы электронными ключами конъюнкторов. В блок входит система логических элементов ИЛИ, построенных на микросхемах: DD 21, DD 22, DD 23 (фиг.3).

Блоки устройства: 7 ЭКДЗ - электронные ключи дизъюнкторов, 8 ЭКИЛИ - электронные ключи операции исключающее ИЛИ, 9 ЭКИН - электронные ключи инверторов имеют структуру, выполняют функции, состоят из элементов пороговой логики, аналогичные структуре, функции и составу элементов блока 6 ЭККН - электронные ключи конъюнкторов (фиг.1, 3).

Блок 10 хранения результатов БХР содержит оперативное запоминающее устройство ОЗУ DD 44, двоичный счетчик, формирующий адреса столбцов ОЗУ - Сч 1 DD 42, двоичный счетчик, формирующий адреса строк ОЗУ - Сч 2 DD 43 (фиг.8). Двоичные счетчики вначале работы устройства обнулены управляющими сигналами ОБ, УС "0" соответственно, поступающими из блока 11 управления. На входы счетчиков поступают прямоугольные импульсы ГИ, ТИ из блока 11 управления. Счетчики формируют адреса столбцов - АД СТЛ и строк АД СТР, по которым будет записаны результаты логических операций - РБО, поступающие на вход - Вх оперативного запоминающего устройства ОЗУ DD 44. Сигналы управления оперативного запоминающего устройства ОЗУ DD 44 выбора кристалла и считывания/запись соответственно при записи принимают значения ВК=0, Сч/Зп=0 (фиг.8).

Блок 11 управления синтезируется на основе ГСА алгоритма управления (фиг.9а, 96) известным способом [3]. Размеченная ГСА работы блока 11 управления приведена на фиг.10а, 10б, где обозначено:

ИСТОЧНИКИ ИНФОРМАЦИИ

1. Самофалов К.Г., Романкевич А.М., Валуйский В.Н. Прикладная теория цифровых автоматов. - Киев: Высш. шк., 1987. - 374 с.: ил.

2. Мкртчян С.О. Проектирование логических устройств ЭВМ на нейронных элементах. - М.: Энергия, 1977.

3. Баранов С.И. Синтез микропрограммных автоматов. - Энергия. Ленинградское отделение, 1974. - 184 с.

4. Дертоузос М. Пороговая логика. - М.: Мир, 1967.

5. Вавилов Е.И. и др. Синтез схем на пороговых элементах. - М.: Сов. радио, 1970.

6. Заявка RU №94007826 от 1996.02.27 г. (прототип).

7. Заявка UA Авторское свидетельство СССР N 1285963 от 1995.10.20 г. (аналог).

8. Заявка RU №2042186 от 1995.08.20 г. (аналог).

9. Заявка RU №2049346 от 1995.11.27 г. (аналог).

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительный модуль логических операций | 2019 |

|

RU2716026C1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство поразрядного вычисления логических и арифметических операций | 2020 |

|

RU2739343C1 |

| КОНЪЮНКТИВНО-ДИЗЪЮНКТИВНЫЙ РЕЛЯТОР | 1999 |

|

RU2143730C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1997 |

|

RU2134442C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО ЛОГИЧЕСКОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 1996 |

|

RU2106676C1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

| УСТРОЙСТВО СОРТИРОВКИ ИНФОРМАЦИИ МЕТОДОМ ДЕШИФРАЦИИ ДАННЫХ | 2006 |

|

RU2319197C1 |

| Устройство для вычисления булевых функций | 1980 |

|

SU955027A1 |

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

Изобретение относится к техническим средствам информатики и вычислительной техники и может быть использовано для создания специализированных процессоров по выполнению логических операции функционально полной системы булевых функций. Техническим результатом является расширение функциональных возможностей и повышение надежности работы. Устройство содержит систему электронных ключей, блок конъюнкторов, блок дизъюнкторов, блок операции исключающее ИЛИ, блок инверторов, электронные ключи конъюнкторов, электронные ключи дизъюнкторов, электронные ключи операции исключающее ИЛИ, электронные ключи инверторов, блок хранения результатов, блок управления, пороговые элементы, нейроны. 12 ил.

Устройство выполнения логических операций, содержащее элементы исключающее ИЛИ, отличающееся тем, что дополнительно введены система электронных ключей, блок конъюнкторов, блок дизъюнкторов, блок инверторов, электронные ключи конъюнкторов, электронные ключи дизъюнкторов, электронные ключи операции исключающее ИЛИ, электронные ключи инверторов, блок хранения результатов, блок управления, причем первый и второй информационные выходы блока управления соединены соответственно с первым и вторым информационными входами системы электронных ключей, информационный выход которой соединен с первым информационным входом электронных ключей конъюнкторов, с первым информационным входом электронных ключей дизъюнкторов, с первым информационным входом электронных ключей операции исключающее ИЛИ, с первым информационным входом электронных ключей инверторов, третий и четвертый информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей конъюнкторов, пятый и шестой информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей дизъюнкторов, седьмой и восьмой информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей операции исключающее ИЛИ, девятый и десятый информационные выходы блока управления соединены соответственно со вторым и четвертым информационными входами электронных ключей инверторов, с первого по шестой управляющие выходы блока управления соединены соответственно с первым по шестой управляющими входами блока хранения результата, информационный выход электронных ключей конъюнкторов соединен с информационным входом блока конъюнкторов, информационный выход электронных ключей дизъюнкторов соединен с информационным входом блока дизъюнкторов, информационный выход электронных ключей операции исключающее ИЛИ соединен с информационным входом блока операции исключающее ИЛИ, информационный выход электронных ключей инверторов соединен с информационным входом блока инверторов, управляющий выход блока конъюнкторов, управляющий выход блока дизъюнкторов, управляющий выход блока операции исключающее ИЛИ, информационный выход блока инверторов соединены с информационным входом блока хранения результата, с третьим информационным входом электронных ключей инверторов, с третьим информационным входом электронных ключей операции исключающее ИЛИ, с третьим информационным входом электронных ключей дизъюнкторов, с третьим информационным входом электронных ключей конъюнкторов, первый и второй управляющие входы "СБРОС" и "ПУСК" блока управления являются внешними входами устройства выполнения логических операций.

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2246752C1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| US 5581661 A, 03.12.1996. | |||

Авторы

Даты

2006-11-27—Публикация

2005-06-16—Подача