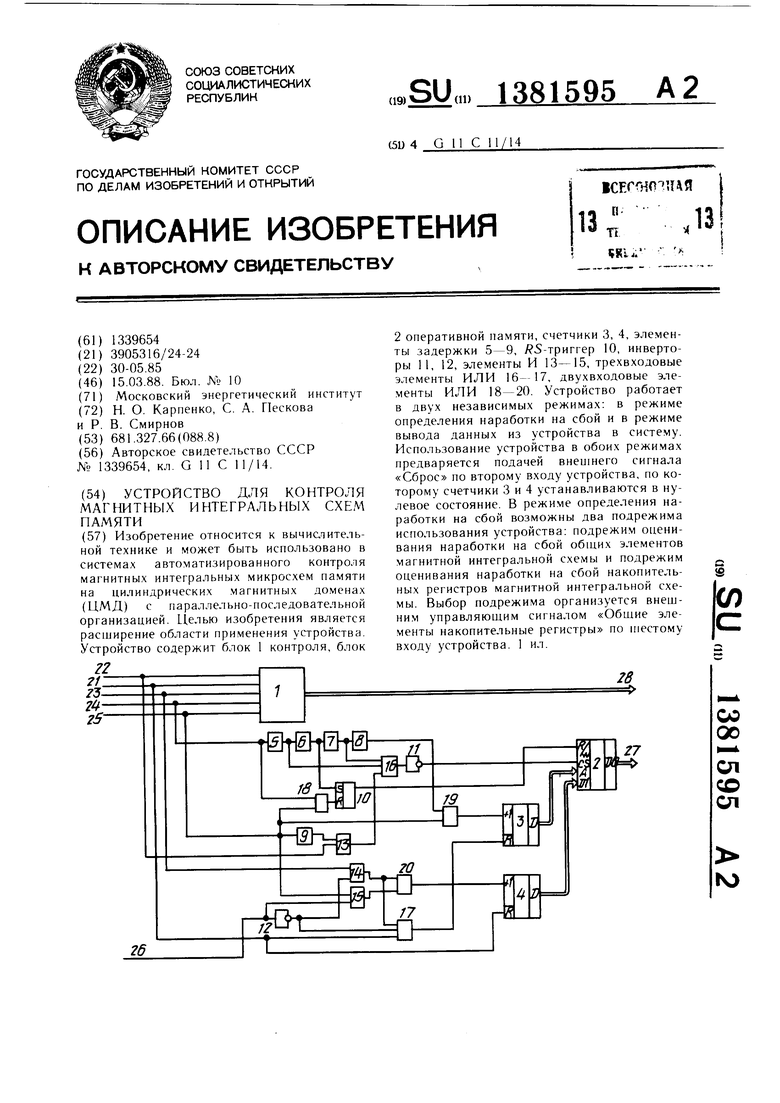

Изобретение относится к вычислительной технике, может быть использовано в системах автоматизированного контроля магнитных интегральных микросхем памяти на цилиндрических доменах () с параллельно-последовательной организацией и является дополнительным к авт. св. № 1339654. Цель изобретения р, 1сп ирение об;1асти нрнмеь сния у -гройства.

На чери /ке изоб) б;1ок-схема нред -laracMoro устройства.

Уст-(;(;йстио содержи б.чок 1 контроля, блок 2 опеоатИННОЙ памяти, счетчики 3, 4, первый пятый элемешы задержки 5 9, / 5-триггер 10, первый И и второй 12 верторы, первый третий элементы И 13 15, первый 16 и вт(.))ой 17 трехвхоловые i:ie.MciiT i М, 1 7. |К (ии,1Й - rprii ; ;

il. lH 18--2(). Вто iT.i I 13 СОСД ; .-И ; Истца, третий нхс).; ..icMcina ИЛИ ; (сл.инсны с BTO)ij;v

:Ч)|-,ЫЙ ВХОД второго

грстьим входом 23 B si i :и ,)Г)го двухвходо ii 18 1 hXb.i || ЧН()го уле.мсиг;. огдннснь с чг1 ,ергым входом

., р.юрой В(11 (ТО)О1 О ;ПЛ

i-MCH i a или I ). вход iiHi ui.; , р/кк)( Ь . ;ic iitbiri нход треп.сг.. . 1 i ,I )) ихо.ч первого . И л х- ;- 1снга S1 И 1 10 .- едипснм i . 25 v ,i роист на «горой r;(ii

КХО.Ч 2() it i O()i u

I If. ЫМ vi,,

I . TOMl. ti -1 bbii vK poi .) -..ICVU HT ,

iv ji ;i I i- 1 : -. - , isi Ku I .

t .i:

ДВуХВХ(.)ДО15ЫС .Nieil Ы liXfi.a исрво:;; (ЛсМ

С гтервым 2 нто)ого I рсх.чч |Д1))1;)1 . и ВХО.1 сб)1га (Tirii.

ВХОД, . 2 ус: :

ЭЛСМС1ГГИ и 14 гос днг: уст poMcrii

ВОГО -.(. V

и:1 Ил I

I lCit :

.

ИЛС И .

.hiijk ; ;. :ui;i p.

/TC.MiMII I -- ):.1 ih MUjro I |:, ,.. . Ill (), пЬГлОД MCTTu pI .-.ii cot с :icpiii. b -t..:/- )|.: .; : ч v-. 4.,, ,;oi о jjlCMthr;: l, M), выход К1;1О)о;м сос.тинен со счет .. : ;i...).).n ;.|стчика ii ч 1:.10рмациопне.Й И..1Х(Х. 1. ко10р .ч о сосдмнсп с а;1) входом блока 2. Hbi .o;: ;и.-|;в(И .1 №Ух1 ходов(ач ч.тс- мепт а ИЛИ coe; ..H :ii ii с . триггера 10, иы.ход i.;ij i,iC; -з.телк нт-а J -,;; держкм сосдлиен с iieii(, . Uj.M iic-tJHoro : лемента И 13, utjxoa KnTriporo соедши-и с тр(.-тьпм ь.ходом ncfUioi 11 ; р1 ХВХ()го алсменга ИЛИ 16, выхс)л вго)О1о : леме1 г И 14 соединен с первым входо. Л т рет.-i.-i ij

0

двухвходового элемента ИЛИ 20 и с первым входом второго трехвходового элемента ИЛИ 17, вы.ход которого соединен с входом сброса счетчика 3, выход третьего элемента И 15 соединен с вторым входом третьего двухвходового эле.мента ИЛИ 20, выход которого соединен со счетны.м входом счетчика 4, информационный выход которого соедииен с входом ланных блока 2, выход в ( инвертора 12 соединен с вторым входо.м второго элемента И 14 и с вторым вхолом второго трехвходового эле.мента ИЛИ 17.

Предлагаемое устройство работает в лвух независимых режимах: режиме опре- .- деления наработки на сбой, режиме вывода данных и.з устройства в систему. Исполь- «)и1ние устройства в обоих режимах пред- 1с1р)яегся подачей BHcnmeici сигнала «Сброс МО втт))) входу 22 уст)ойства, по которо.му -ч( (чик И и счетчик 4 уст-анавливаются в 0 ;iy,:cBoc состояние. В режиме определения lapatM.irKH на сбой возможны два подрежима (..Ьчонания устройсгва: юдрежим оцени- и:1иия наработки на сбой общих элементов магмигной И1ггегральп()й схемы; подрежим (Hu ii fiBann наработки на сбой нако11ите;1Ь- i:,: jxTMcrpOB магнитной интегральной схе- x;;,i. Р-ыбо|) подрежима организуется внещ- |им -п)авляютим сигн.кчом «Об1цие эле- MfMiii Иокопительные ич истры по шестому и ходу 2t) Устройства.

1 разлагаемое усгроисгво работает сле- iJidM оГ))азом.

определения наработки на сбой. ;о; :-1 уст)ойсгва н id.v; сжиме нротекает )r.i.i.L льпо процессу счит| 115анпя инфор- с магнитной И1Г1сгральной схемы. ;i. };i;-.iMH уп|)ав.:1Я1 ицпми спгиа.чами в I I .vKnMe яв.чяются впспшие сигналы i. ii.ic I .iT OBbi i(i п/Г1(;.му входу 25 VCT0

iH. t. .()п1ибка:- i t( iBii . Я|)вая

/3 yn p jiuT Ba. |-;ил1 тч . ьсгиует

. ,.; ; .М НОЙ ИНТС ; - ими ()ИТ. .j,

по первому входу 21 трапипа по третьему пгнал «Лаиные гото- чт о с проверяе1 ЮМ

:л1,ной схемы считан i гОшиГжа указывает

3

i. i -..м 1)|)иаружено 11есов11адение считан- ,. 1. -ilia г :)та. 1оном. (ли нал «Новая ст ра- . lUj,- имеет место (О1 да, когда начинается i;ci .,ii,.aHiU нового данных.

Гч-чу.Тг, га том рабогы усгройства в режиме . ||| е,|слсп; Я наработки на сбой является i:i -..n, :(-ii)ic :;iu|)0,v, О числс сбоев, вы- uuiHi.i.x каждым накопительным регистром ч |(И1 )|.и;м в 1|елом; 1-ако:1.чсние инфор.мации и моменгах последних сГюев каждого нако- ...ч(; регистра и.чи оопшх элементов л1агпп1иой пнгегральн:;ч: t хемы. Информация ; ч(11.те сбоев форг.; П1уется блоком конт

p;fJ..TH i

И o.iOK 2 заносятся данные о моментах iK.i i,iiiKi,:ih(. НИН текущих сбоев. В ячейке . ;улень1м адресом фиксируется .момент сбоя iK iiufiX лс ментов, а в .ячейках с адресами

с 1 no К-й моменты сбоев 1 - К накопительных регистров. По завершении испытаний в блоке 2 хранится информация о моментах возникновения последних сбоев, имев тих место в этих испытаниях. Данными для занесения в блок 2 служит содержимое счетчика 4, в котором формируется тот номер считанного с магнитной интегральной схемы бита, под которым этот бит проходил через исследуемый элемент прибора.

Порядок прохождения битов через общие элементы магнитной интегральной схемы полностью совпадает с порядком их стедова- ния со схемы считывания, поэтому для подрежима определения наработки на сбой об- 1ДИХ элементов в счетчике 4 фиксируется текущее число сигналов «Данные готовы. Что касается порядка прохождения битов через отдельный накопительный регистр, то номер бита, вышедшего с некоторого накопительного регистра соответствует номеру считанного блока данных, поэтому для подрежима определения наработки на сбой накопительных регистров в счетчике битов фиксируется текущее число сигналов «Новая страница. Если считанный бит не совпадает с эталоном, о чем свидетельствует наличие сигнала «Ошибка, содержимое счетчика 4 заносится в блок 2.

Первый сигнал «Данные готовы сбрасывает / 5-триггер 10, устанавливая тем самым режим записи блока 2. Последовательность операций по каждому сигналу «Данные готовы следующая: в подрежиме определения наработки на сбой накопительных ре1 истров содержимое счетчика 3 наращивается на «1, в то время как в подрежиме определения наработки на сбой обших элементов счетчик 3 постоянно находится в сброшенном состоянии, обеспечивая задание нулевого адреса блока 2; в подрежиме определения наработки на сбой общих элементов содержимое счетчика 4 наращивается на «1 в случае наличия сигнала «Ошибка активизируется сигнал выборки блока 2, по которому осуществляется занесение содержимого счетчика 4 по текущему адресу блока 2.

Очередность действий организуется с помощью пятого элемента 9 задержки.

Для подрежима определения наработки на сбой накопительных регистров наращивание содержимого счетчика 4 на «1 происходит по сигналу «Новая страница, и, кроме того, по этому сигналу происходит обнуление счетчика.3 с целью получения соответствия между адресным пространством блока 2 и накопительными регистрами магнитной интегральной схемы.

Режим вывода данных из устройства в систему. Этот режим служит для выдачи в систему данных, сформированных в режиме определения наработки на сбой. Этими данными являются данные о числе сбоев каждого накопительного регистра и прибора в целом и данные о моментах последних

10

сбоев накопительных регистров или общих элементов прибора. Управляющим сигналом для устройства в этом режиме служит внешний сигнал «Пересылка по четвертому вхо- 5 ду 24 устройства. Для передачи в систему К слов, содержащих данные о количестве сбоев, и К слов, содержащих данные о моментах последних сбоев, требуется подать К сигналов «Пересылка. Данные о кбличест- ве сбоев поступают на выход 28 устройства, а данные о моментах последних сбоев на второй выход 27 устройства с выхода данных блока 2.

Последовательность действий в этом режиме следующая: установка режима чтения 15 блока 2 (установка в «1 -состояние RS- триггера 10); активизация входа выборки блока 2, в результате чего очередное слово считывается из блока 2 и фиксируется на втором выходе 27 устройства; установка режима записи блока 2 (установка в 20 состояние / 5-триггера 10); активизация входа выборки блока 2, в результате чего нулевое содержимое счетчика 4 заносится в выбранную ячейку блока 2. Таким образом, считывание содержимого каждой ячейки 5 сопровождается ее очисткой (д.чя подготовки блока 2 к новому циклу работы). Нулевое значение момента последнего сбоя в конце испытаний свидетельствует об отсутствии сбоя; содержимое счетчика 3 нарап1,ивается на «1.

0 Очередность операций организуется первым - четвертым элементами 5- 8 задержки.

Формула изобретения

Устройство для контроля магнитных ин5 тегральных схем памяти по авт. св. № 1339654, отличающееся тем, что, с целью расщирения области применения устройства, оно содержит оперативный блок памяти, счетчик и элементы задержки / 5-триггер, инверторы, элементы И, трехвходовые эле0 менты ИЛИ и двухвходовЪ1е элементы ИЛИ, причем второй вход первого элемента И соединен с первым входом устройства, третий вход второго трехвходового элемента ИЛИ и вход сброса первого счетчика соединены

;- С вторым входом устройства, первый вход второго элемента И соединен с третьим входом устройства, первый вход первого двух- входового элемента И и вход первого элемента задержки соединены с четвертым входом устройства, второй вход второго двух0 входового элемента ИЛИ, вход пятого элемента задержки, первый вход третьего элемента И и второй вход первого двухвходо- вого элемента ИЛИ соединены с пятым входом устройства, второй вход третьего элемента И и вход второго инвертора соединены

5 с щестым входом устройства, выход первого элемента задержки соединен с входом второго элемента задержки и вторым входом первого трехвходового эле.мента ИЛИ, выход которого соединен с входом первого инвертора, выход которого соединен с входом выборки блока оперативной памяти, выход которого является вторым выходом устройства, выход второго элемента задержки соединен с входом третьего элемента задержки и с S-входом / 5-триггера, выход которого соединен с входом установки режима чтения- записи блока оперативной памяти, выход третьего элемента задержки соединен с входом четвертого элемента задержки и с первым входом первого трехвходового элемента ИЛИ, выход четвертого элемента задержки соединен с первым входом второго двухвхо- дового элемента ИЛИ, выход которого соединен со счетным входом второго счетчика, информационный выход которого соединен с адресным входом блока оперативной памяти, выход первого двухвходового элемента

ИЛИ соединен с / -входом / 5-триггера, выход пятого элемента задержки соединен с первым входом первого элемента И, выход которого соединен с третьим входом первого трехвходового элемента ИЛИ, выход второго элемента И соединен с первым входом третьего двухвходового элемента ИЛИ и с первым входом второго трехвходового элемента ИЛИ, выход которого соединен с входом сброса второго счетчика, выход третьего

элемента И соединен с вторым входом третьего двухвходового элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, информационный выход которого соединен с входом данных блока оперативной памяти, выход второго инвертора

соединен с вторым входом второго элемента И и с вторым входом второго трехвходового элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля магнитных интегральных схем памяти | 1985 |

|

SU1339654A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| АНАЛИЗАТОР ПАРАМЕТРИЧЕСКИХ ОТКАЗОВ И СБОЕВ | 2004 |

|

RU2270470C2 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2005 |

|

RU2296365C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство поиска и контроля адреса страницы для доменной памяти | 1983 |

|

SU1095242A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОБУЧЕНИЕМ И ОЦЕНИВАНИЕМ ЗНАНИЙ ОБУЧАЮЩИХСЯ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2011 |

|

RU2467388C1 |

| Устройство для ввода информации | 1986 |

|

SU1363225A2 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматизированного контроля магнитных интегральных микросхем памяти на цилиндрических магнитных доменах (ПМД) с параллельно-последовательной организацией. Целью изобретения является расширение области применения устройства. Устройство содержит блок 1 контроля, блок 22 21 2 оперативной памяти, счетчики 3, 4, элементы задержки 5-9, / 5-триггер 10, инверторы 11, 12, элементы И 13-15, трехвходовые элементы ИЛИ 16-17, двухвходовые элементы ИЛИ 18-20. Устройство работает в двух независимых режимах: в режиме определения наработки на сбой и в режиме вывода данных из устройства в систему. Использование устройства в обоих режимах предваряется подачей внешнего сигнала «Сброс по второму входу устройства, по которому счетчики 3 и 4 устанавливаются в нулевое состояние. В режиме определения наработки на сбой возможны два подрежима использования устройства: подрежим оценивания наработки на сбой общих элементов магнитной интегральной схемы и подрежим оценивания наработки на сбой накопительных регистров магнитной интегральной схемы. Выбор подрежима организуется внешним управляющим сигналом «Общие элементы накопительные регистры по шестому входу устройства. 1 ил. $б / оо оо ел ;о ел К)

| Устройство для контроля магнитных интегральных схем памяти | 1985 |

|

SU1339654A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-03-15—Публикация

1985-05-30—Подача