1

Изобретение относится к вычислительной технике и может быть исполь-, зовано при разработке запоминающих устройств на цилиндрических магнитньп доменах (1Щ) ,

Целью изобретения является упрощение устройства.

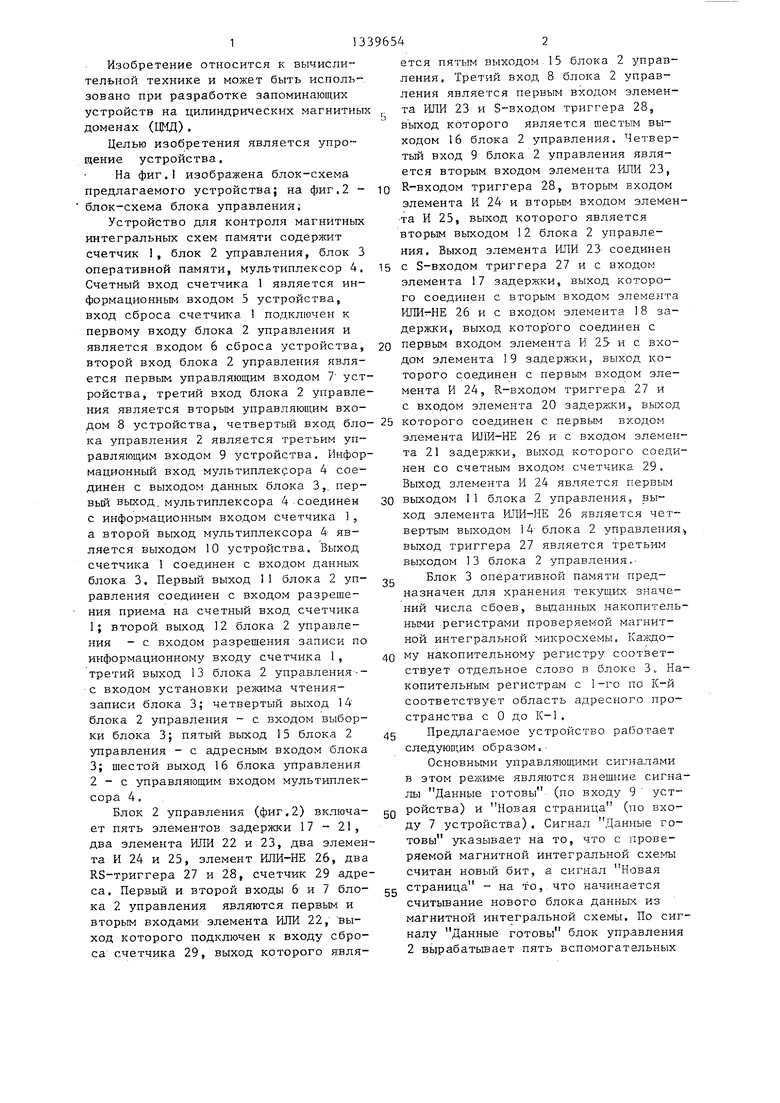

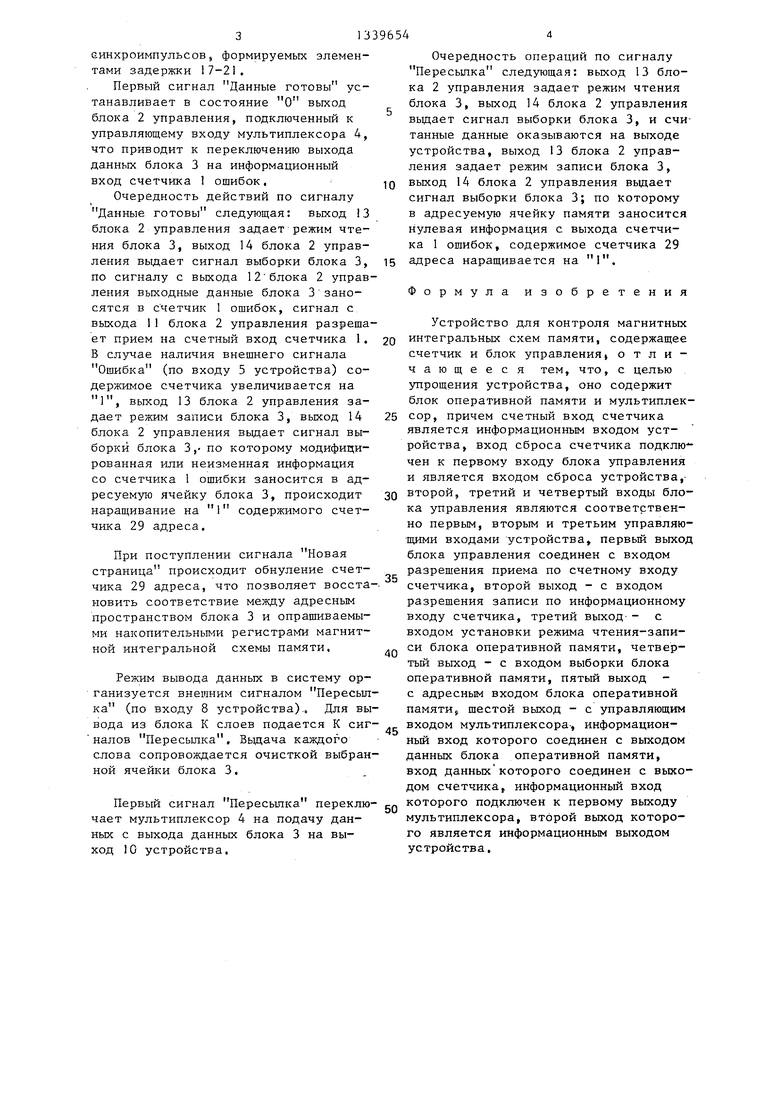

На фиг.I изображена блок-схема предлагаемого устройства; на фиг.2 - блок-схема блока управления;

Устройство для контроля магнитных интегральных схем памяти содержит счетчик 1, блок 2 управления, блок 3 оперативной памяти, мультиплексор 4, Счетный вход счетчика 1 является информационным входом 5 устройства, вход сброса счетчш :а. подключен к первому входу блока 2 управления и является входом 6 сброса устройства, второй вход блока 2 управления является первым, управляющим входом 7 устройства, третий вход блока 2 управле13

20 первым входом элемента И 25 и с входом элемента 19 задержки, выход которого соединен с первым входом элемента И 24, R-входом триггера 27 и с входом элемента 20 задержки, выход

НИН является вторым управляющим входом 8 устройства, четвертый вход бло- 25 которого соединен с первым входом ка управления 2 является третьим уп элемента ШШ-НЕ 26 и с входом элемен равляющим входом 9 устройства. Информационный вход мультиплексора 4 соединен с выходом данных блока 3,. первый выход, мультиплексора 4 соединен с информационным входом счетчика 1, а второй выход мультиплексора 4 является выходом 10 устройства. Выход счетчика 1 соединен с входом данных блока 3, Первый выход II блока 2 управления соединен с входом разрешения приема на счетный вход счетчика 1; второй выход 12 блока 2 управления - с входом разрешения записи по информационному входу счетчика 1, третий выход 13 блока 2 управления-- с входом установки режима чтения- записи блока 3; четвертый выход 14 блока 2 управления - с входом выборки блока 3; пятый выход 15 блока 2 управления - с адресным входом блока

35

40

та 21 задержки, выход которого соеди нен со счетным входом счетчика. 29. Выход элемента И 24 является первым

30 выходом 11 блока 2 управления, выход элемента ИЛИ-МЕ 26 является четвертым выходом 14 блока 2 управления выход триггера 27 является третьим выходом 13 блока 2 управления,

Блок 3 оперативной памяти предназначен для хранения текущих значений числа сбоев, выданных накопитель ными регистрами проверяемой магнитной интегральной микросхемы. Каждому накопительному регистру соответствует отдельное слово в блоке 3, На копительным регистрам с по К-й соответствует область адресного пространства с О до К-1.

Предлагаемое устройство работает следуюп им образом.

45

3; щестой выход 16 блока управления 2 с управляющим входом мультиплексора 4.

Блок 2 управления (фиг,2) включает пять элементов задержки 17 - 21, два элемента ИЛИ 22 и 23, два элемента И 24 и 25, элемент ИЛИ-НЕ 26, два RS-триггера 27 и 28, счетчик 29 адреса. Первый и второй входы 6 и 7 блока 2 управления являются первым и вторым входами элемента ИЛИ 22, выход которого подключен к входу сброса счетчика 29, выход которого явля

96542

ется пятым выходом 15 блока 2 управления. Третий вход 8 блока 2 управления является первым входом элемен- j та ИЛИ 23 и S-входом триггера 28, в ыход которого является шестым выходом 16 блока 2 управления. Четвертый вход 9 блока 2 управления является вторым входом элемента ИЛИ 23,

10 R-входом триггера 28, вторым входом элемента И 24- и вторым входом элемента И 25, выход которого является вторым выходом 12 блока 2 управления. Выход элемента ИЛИ 23 соединен

15 с S-входом триггера 27 и с входом элемента 17 задержки, выход которого соединен с вторым входом элемента ИЛИ-НЕ 26 и с входом элемента 18 задержки, выход которого соединен с

20 первым входом элемента И 25 и с входом элемента 19 задержки, выход которого соединен с первым входом элемента И 24, R-входом триггера 27 и с входом элемента 20 задержки, выход

25 которого соединен с первым входом элемента ШШ-НЕ 26 и с входом элемен

которого соединен с первым входом элемента ШШ-НЕ 26 и с входом элемен

та 21 задержки, выход которого соединен со счетным входом счетчика. 29. Выход элемента И 24 является первым

выходом 11 блока 2 управления, выход элемента ИЛИ-МЕ 26 является четвертым выходом 14 блока 2 управления выход триггера 27 является третьим выходом 13 блока 2 управления,

Блок 3 оперативной памяти предназначен для хранения текущих значений числа сбоев, выданных накопительными регистрами проверяемой магнитной интегральной микросхемы. Каждому накопительному регистру соответствует отдельное слово в блоке 3, Накопительным регистрам с по К-й соответствует область адресного пространства с О до К-1.

Предлагаемое устройство работает следуюп им образом.

Основными управляющими сигналами в этом режиме являются внешние сигналы Данные готовы (по входу 9 устройства) и Новая страница (по входу 7 устройства), Сигнал Данные готовы указывает на то, что с проверяемой магнитной интегральной считан новый бит, а сигнал Новая

страница -- на то, что начинается считывание нового блока данных из магнитной интегральной схемы. По сигналу Данные готовы блок управления 2 вырабатьшает пять вспомогательных

синхроимпульсов, формируемых элементами задержки 17-21.

Первый сигнал Данные готовы устанавливает Б состояние О выход блока 2 управления, подключенный к управляющему входу мультиплексора 4, что приводит к переключению выхода данных блока 3 на информационный вход счетчика 1 ошибок,

Очередность действий по сигналу Данные готовы следующая: выход 13 блока 2 управления задает режим чтения блока 3, выход 14 блока 2 управления выдает сигнал выборки блока 3, по сигналу с выхода 12 блока 2 управления выходные данные блока 3 заносятся в счетчик 1 ошибок, сигнал с выхода 11 блока 2 управления разрешает прием на счетный вход счетчика 1, В случае наличия внешнего сигнала Ошибка (по входу 5 устройства) содержимое счетчика увеличивается на 1, выход 13 блока 2 управления задает режим записи блока 3, выход 14 блока 2 управления вьщает сигнал выборки блока 3,- по которому модифицированная или неизменная информация со счетчика 1 ошибки заносится в адресуемую ячейку блока 3, происходит наращивание на 1 содержимого счетчика 29 адреса.

При поступлении сигнала Новая страница происходит обнуление счетчика 29 адреса, что позволяет восста повить соответствие между адресным пространством блока 3 и опрашиваемыми накопительными регистрами магнитной интегральной схемы памяти.

Режим вывода данных в систему организуется внешним сигналом Пересьт ка (по входу 8 устройства).. Для вывода из блока К слоев подается К сиг налов Пересылка, Вьщача каждого слова сопровождается очисткой выбранной ячейки блока 3.

Первый сигнал Пересыпка переключает мультиплексор 4 на подачу данных с выхода данных блока 3 на выход 1C устройства.

Очередность операций по сигналу Пересылка следующая: выход 13 блока 2 управления задает режим чтения блока 3, выход 14 блока 2 управления вьщает сигнал выборки блока 3, и считанные данные оказываются на выходе устройства, выход 13 блока 2 управления задает режим записи блока 3, выход 14 блока 2 управления выдает сигнал выборки блока 3; по которому в адресуемую ячейку памяти заносится нулевая информация с выхода счетчика 1 ошибок, содержимое счетчика 29 адреса наращивается на I.

Формула изобретения

0

5

0

В

0

5

0

Устройство для контроля магнитных интегральных схем памяти, содержащее счетчик и блок управления, отличающееся тем, что, с целью упрощения устройства, оно содержит блок оперативной памяти и мультиплексор, причем счетный вход счетчика является информационным входом устройства, вход сброса счетчика подклю- чен к первому входу блока управления и является входом сброса устройства,- второй, третий и четвертый входы блока управления являются соответственно первым, вторым и третьим управляющими входами устройства первый выход блока управления соединен с входом разрешения приема по счетному входу счетчика, второй выход - с входом разрешения записи по информационному входу счетчика, третий выход- - с входом установки режима чтения-записи блока оперативной памяти, четвертый выход - с входом выборки блока оперативной памяти, пятый выход - с адресным входом блока оперативной памяти5 шестой выход - с управляющим входом мультиплексора-, информационный вход которого соединен с выходом данных блока оперативной памяти, вход данных которого соединен с выходом счетчика, информационный вход которого подключен к первому выходу мультиплексора, второй выход которого является информационным выходом устройства.

Редактор Н.Лазаренко

Составитель Ю.Розенталь Техред М.Дидык

Заказ 4232/44Тираж 589Подписное

БНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1990 |

|

SU1789975A1 |

| Устройство для отладки программно-аппаратных блоков | 1987 |

|

SU1497617A1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 2011 |

|

RU2450432C1 |

| Устройство для сопряжения в многотерминальной вычислительной системе | 1984 |

|

SU1166124A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке запоминающих устройств на цилиндрических магнитных доменах. Целью изобретения является упрощение устройства;Устройство для контроля магнитных интегральных схем памяти содержит счетчик 1, блок управления 2, блок оперативной памяти 3, мультиплексор 4. Счетный вход счетчика 1 является ин- .формационным входом 5 устройства. Вход сброса счетчика 1 подключен к первому входу блока управления 2 и является входом сброса 6 устройства. Второй вход блока управления 2 является первым управляющим входом 7 устройства, третий вход блока управления 2 - вторым управляющим входом 8 устройства, четвертый вход блока управления 2 - третьим управляющим входом 9 устройства. Информационный вход мультиплексора 4 соединен с выходом данных блока 3. Первый выход гультиплексора 4 соединен с информационным входом счетчика 1, а второй выход мультиплексора 4 является выходом 10 устройства. Выход счетчика 1 соединен с входом данных блока 3. Первый выход 11 блока управления 2- соединен с входом разрешения приема на счетный вход счетчика 1, второй выход 12 блока управления 2-е входом разрешения записи по информационному входу счетчика 1, третий выход 13 блока управления 2-е входом установки режима чтения - записи блока 3, четвертый выход 14 блока управления 2 с входом выборки блока 3, пятый выход 5 блока управления 2 - с адресным входом блока 3, шестой выход 16 блока управления 2 с управляющим входом мультиплексора 4, 2 ил. е (Л со со со О5 СП 4

| ,IEEE Trans | |||

| Magn., V.Mag-16, № 2, 1980, p.424-430 | |||

| Digest papers of IEEE Test Corf., Philadelphia, 1980 | |||

| New York, 1980, p.50-55. |

Авторы

Даты

1987-09-23—Публикация

1985-04-30—Подача