Изобретемие относится к электротехнике, а именно к системам управления тирис- торными 11)ео6разовате.-1Ями, и може найти применение в качестве блока управления преобразователей, ведомых сетью.

Цель изобретения у;1учшение динами ческих характеристик и повын1ение надежности рабогы у тре йстиа.

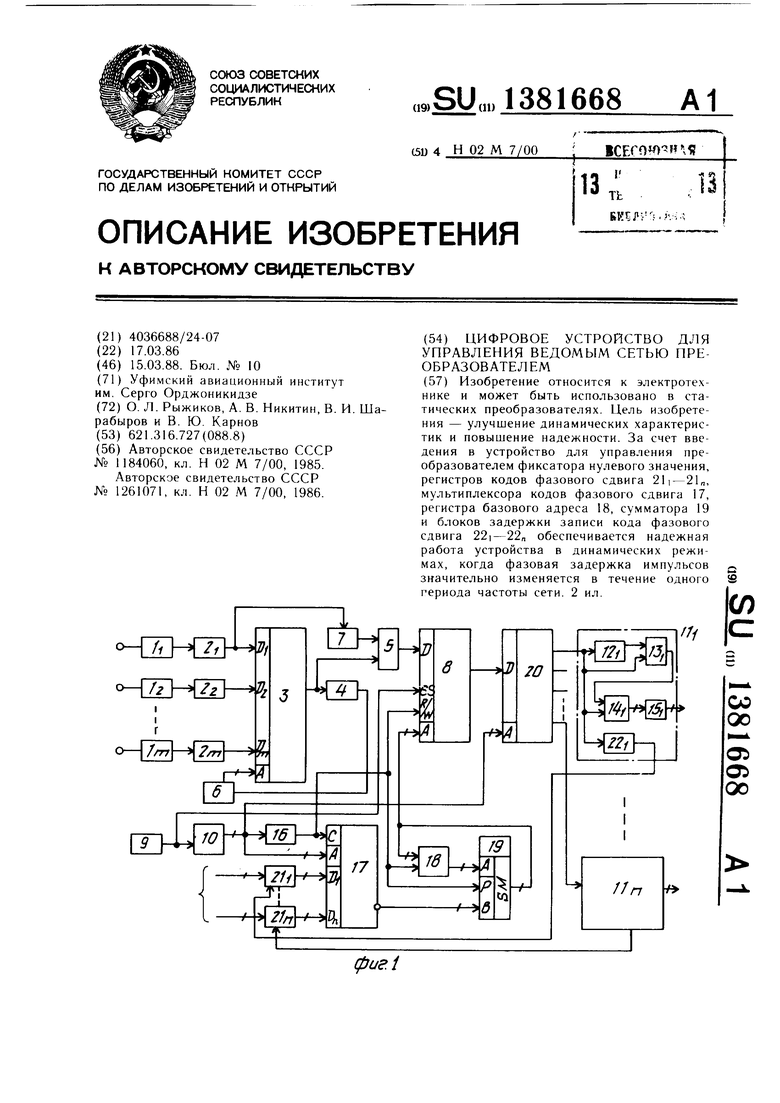

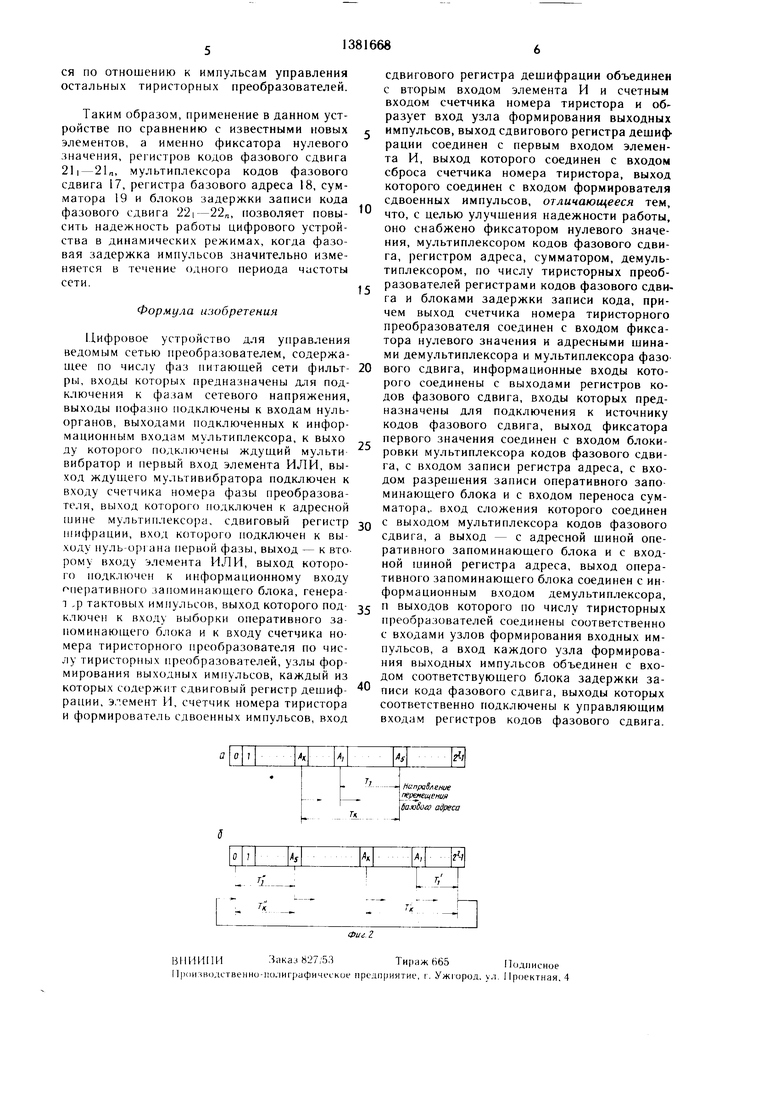

На фи1. I представлена структурная схема устройства; на i)Hi 2 -- ноле яч(Ч к онератинного запомииаюнимч) блока,

Уст)ойство содержит по чис;|у фаз питаю- П1ей сети фи ibTpiii 1,1 liri, входы которых предназначены для 1К)дключения и фазам сетевог о напряжения, а выходы иофазно подключены к входам пуль-органов 2,1...2ni, выходами подк,: юченных и информационным входам мульгиплексо|1а 3, к выходу которого подключены ждун1ий мультивибратор 4 и первый вход элемента ИЛИ 5, выход жду- inei o 1уль ииибраго)а 4 подключен к входу счетчика номера фазы преобразовагеля 6, выход KOTcjpoi o нодклю Ч И к адрееной ;ппне мультип:1ексора i, сдвиговый регист) Liin({) рации 7, вход Koropoio подключен к выхо ду нуль-органа ш-рной фазы 2, а выход к иго рому входу элемента И.Ч И 5, выхол. кого рого подключен к информационному входу опе)ативпог() запоминающего блока 8, гене paiop тактиьых пмиу Ил ов 9, выход Koiopocc; )дкл1очем к гхо , iibi6 iK;i ()iie|i;iTHRHori) «aiJOMHHaioiiit ll) блока 8 и. входу ск тчик; HoMeiia ти)1и r .jinoro 1реобрачо1 агс :и И), по ЧИСЛУ I иргн i o poi; -;лы форм jjui;; п И Я выходных и И льсов 11, содержащие r.d/K- i ; i MriiBbie регистры , 1еп1И|{)рациг 12, -лс к-|Г1Ы I . : счетчик номера |Ч1)исто- ра 14 н iji(;)i:i|i j4a rt , ii сдвоенных им- ly. ibcoB 1Г), ; Л11д сди1;гово| о рег ис гра де.-- пифрации i 2 oh 1 1-дин1. 11 с вторыми ми лемепга И 13 и счетным входом счетчика Н1:мс)а i ирис гора 14 и об|)а п ет вход узлг фо 1мн|1ог;ания и1)1ходны имнуль сов II, нь:х;;л, ciiuiioHoio |)егистра де ни4 - рапин 12 ч1кдииеп с первым входом элемента И 13. libixc.i, кот,|1ого соединен с входом сброса сче1чнка nnvupa тирИ(.то)а 14. выхо.ч которого сое 1пнеп с входом форми- рова|С.:|я i,,. i;os4iiibix импульсов 15. Устрой- С 1 во 1ОПО.iiin тельпо 1набжено фиксатором Т1ерв(.11(; .Я1ачепия 16, мультHiiJieKC(jpoM фазовси о (.ДНИ а 17. регио ром адреса 18, сум 1атор ; 19, лемул1/тип пексог о.м 20, по числу nipnc т(1) л; регистпами кодов фазовсл о сдви1 а 21 п 1) .1аде)жкн за1:нси кода 22, нричсГ iu, с 1 :м чпка номера ти ристорн(.)го П()р;1 i4ii;i 11,1я 1,1)едипен с входом фиксато| )а лс иого .зн,ачения Ui и а- респыми njnii.aViii дему. и.тиилексора 20 и мультиплексора фа.К ЧОго c;iBHia 17. информа- циочч1)1е в(.) .:)To|ui;o соединен15| с иыхо- ре1 пст;)ов кодой ij)a30Boi() сдвиг.а 2, входы кото) пре.диа 111ачепы д:1, подкл - чемс,. И(;то||ппку кодов ijia iOBoro с;1ВИ1-а, иь1

5

0

5

0

,

0

5

0

5

ход фиксатора ny. ieBoio значения соединен с входом блокировки мультиплексора кодов фазового , с входом записи регистра адреса 18, входом разрешения записи оперативного запоминающего блока 8 и входом переноса сумматора 19, вход сложения которого соединен с выходом мультиплексора кодов фазового сдвига 17, а вход - с адресной 1ииной оперативного запоминаю- nieix.i блока Вис входной шиной ре- гист|)а адреса 18, выход оперативного запо- .минаюп его блока 8 соединен с информа- ционпым входом демультиплексора 20 п выходов которого но числу тиристорных преобразователей соединены соответственио с входами уз.:1ов формирования выходных импульсов 11, а вход каждого узла форми- ровапия выходных импульсов 1 1 объединен с соответсгвующего блока задержки записи кода фазово1о сдвиг-а 22, выходы которых соответственно подключены к управляю- П1ИЛ1 входам рег истров кодов фазового

С; 1ВИ; а - 21 .

Усг)ойство раб тает следуюнгим образом.

Напряжения фа.з сети подаются на вход- ньи фильтры 1.1 l.ni, а затем на нуль-ор- 1аны 2 1 2.т, фиксирующие положительными импульсами на своих выходах момент пере.хода через ну.ль напряже)1ия в соот- ветгт(ук)щей фазе. Эти и.мпульсы поступают и )П)еде,тенной пос., |е;|.оиа1 льности на ин- ф 0(1 лаипо1 ные нчичы му. и/гнплексора 3, а на уп)мн.1ик)1ци:е его нхо чы поступает с выхода CMevHK.y номера (}i;i зы ti код, обеспечивай чции нолк.лю-к нис одного из пнформа- циончьк входл. в чере. выход му;1ьти11,:|ек сорт 3 к жд.ущему мул тивибратч)ру 4 с Hpev.eHk M зад(. ржкн Т). Импульс с выхода ,-кД ineio мулы n,iH j|ia О|)а 4 нерек.тючит через нр(мя Тд счетч:1к 6, при это.м муль- гип. 3 перек,1К)чится на ожидание им- |;у.||ка ;() следуюпцмо () порядку ну,ть-ор- laii.i, пос.те чего процесс повторяется.

Г.1КИМ образом, на одном из входов элемента ИЛИ 5 ф(фмируетс од}и)канальная послед,овательность синхронизирующих им- ny.TbC(jB. Имну.тьс с выхода первого нуль- 2 задерживается сдвиговым регист- )()М 7 на один такт и поступает па второй иход эле.мента ИЛИ 5, лри этом на ею выходе и однокана.)1ьной последовательпоети импульсов первый из г руппы является сдвоен- , что необходимее в дaJTЬнeйнleм для определения, к какой из фаз принад.тежит кажд1)1Й импулье.

Рабочий цикл устройства состоит из п+1 тактов генератора тактовых имнульсов 9, определяющих состояние выхода счетчика номера тиристорнс.м о преобразователя 10, здес Ь п -- число управляемых тиристоров пpe(Jбpaзoвaтeлeй. Ири нулевом состоянии ()икси)уемый фнкеатором пулевого значения i(j (Л1е)ативный запомипающий блок 8 вклю чается в режим записи и одновременно

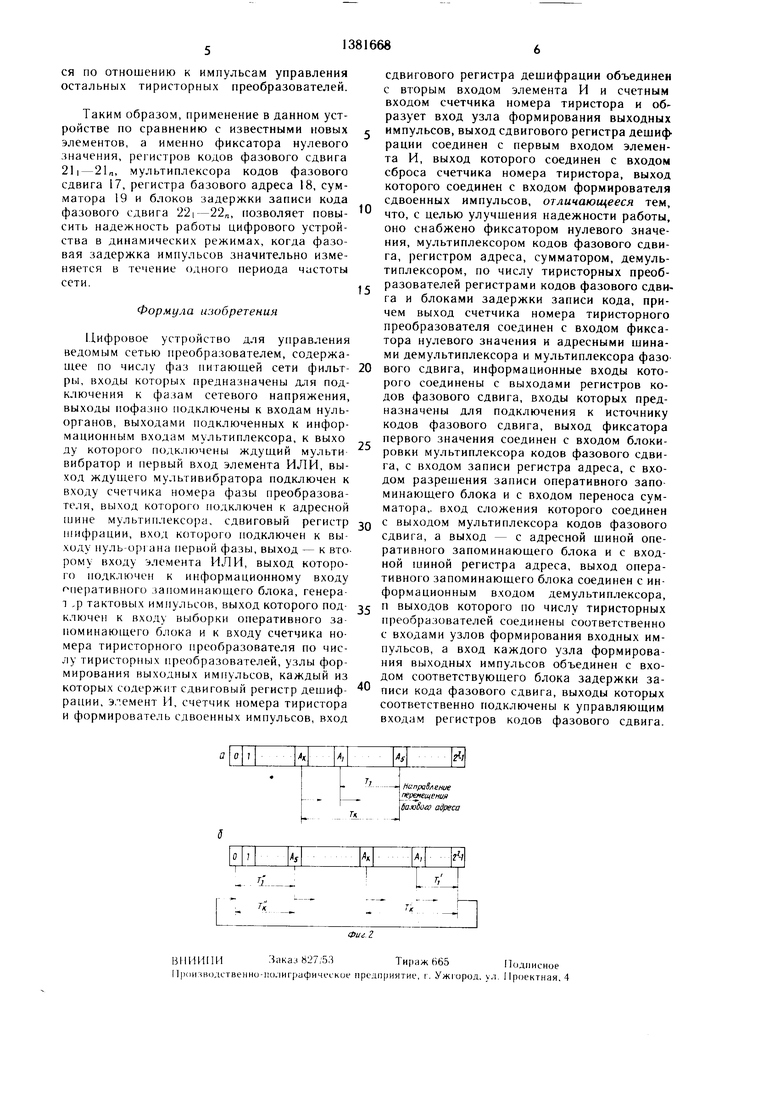

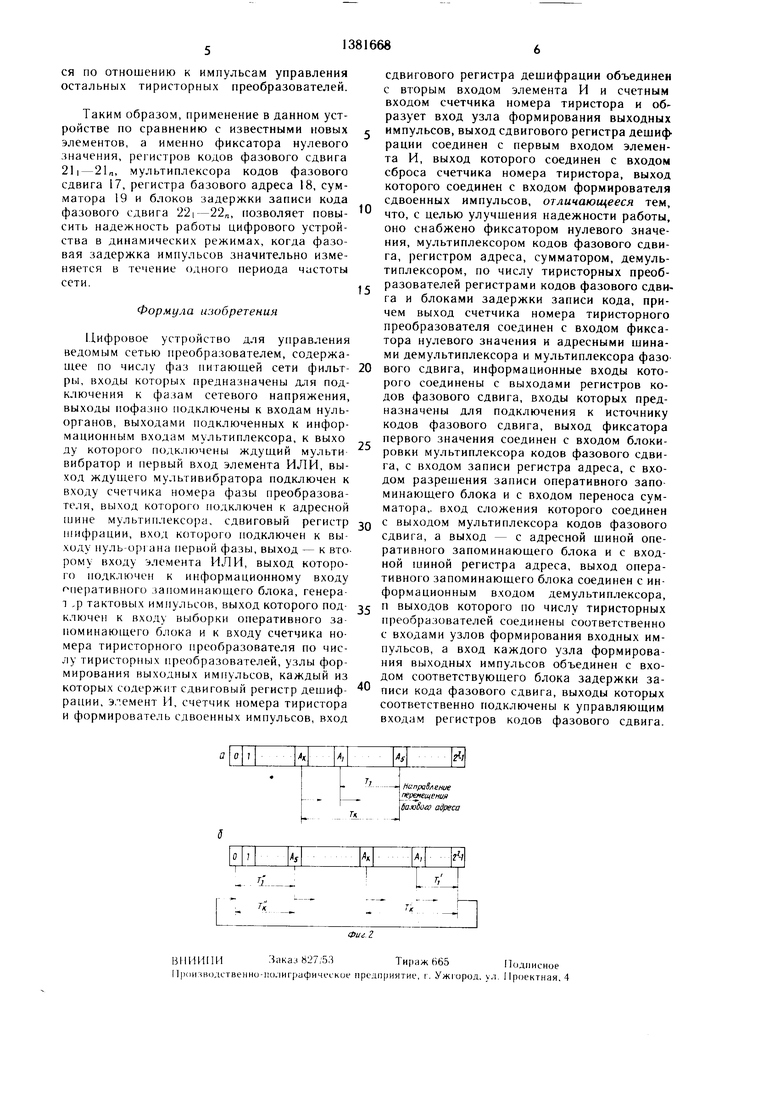

блокировкой мультиплексора 17 no входу С устанавливается нулевое состояние ши)Ы В сумматора 19, в результате чего код с выхода регистра адреса 18 увеличивается на 1, носкольку на вход переноса Р сумматора 19 поступает положительный импульс. В этом же также в случае появления на информационном входе D оперативного запоминающего блока 8 сигнала синхронизации он будет записан в виде «1 в ячейку с адресом AJ (фиг. 2а), в протизном случае в нее записывается 0. По окончании нулевого такта в регистре адреса 18 спадом сигнала нулевого состояния фиксируется новое значение базового адреса (фиг. 2а).

В течение следующих тактов коды фазового сдвига управляющих импульсов соответствующих тиристорных преобразователей поочередно подключаются через мультиплексор 17 к щине В сумматора 19, при этом на выходе сумматора формируется адрес ячейки, из которой считывается информация

Ак (AS-TK)mod 2,(l)

где TK- код фазового сдвига (задержки);

С. - разрядность ОЗБ и сумматора;

К - номер обслуживаемого в данном такте тиристорного преобразователя (К 1, 2,...Г1).

Выходной сигнал переноса сумматора игнорируется, т.е. операция сложения выполняется по mod 2 (поскольку выходная UIH- на мультиплексора 17 содержит инверсные сигналы, фактически выполняется операция вычитания кода фазового сдвига из кода базового адреса).

Таким образом, в течение следующих тактов цикла оперативный запоминающий блок 8 переключается в режим считывания, а на п)ину В сумматора 1-9 поочередно поступают инвертированные коды фазового сдвига, а на его выходе формируется относительный адрес Ак. Базовый адрес, перемещаясь в поле ячеек ОЗБ 8, производит активизацию одной из них в момент прихода задерживаемого импульса, а считанная информация из нес будет через то время, на которое импульс в данном канале задерживается (фиг. 2а).

Импульсы с выхода оперативного запоминающего блока 8 поступают на информационный вход демультиплексора 20, соответствующий номеру канала, определяемого в данном такте, поскольку на ад1)есный вход демультиплексора подается тот же код, что и на адресный вход мультиплексора 17.

Во избежание нарушения работы устройства ввиду конечного числа ячеек оперативного запоминающего блока 8 необходимо выбрать соответствующую разрядность счетчика 10 и ОЗБ 8 таким образом, чтобы обновление информации в данной ячейке могло произойти только после считывания предыдущей информации, т.е. чтобы выполнялось условие

2

тах{Т..

(2)

В этом случае ситуация, возникшая в результате суммирования по модулю 2 (т.е. без переноса из старшего разряда сумматора), не приведет к сбою, поскольку ячейка с базовым адресо.м AR вновь опрашивается через заданное время, так как после ячейки 2-1 выбирается ячейка О (фиг. 26).

Разрядность ОЗБ 8 и сумматора 19 зависит от длительности фазового сдвига т, точности его установки ео и определяется соотношением

15

1 ent(log2|-) -f 1. t

(3)

Частота генератора тактовых импульсов определяется из условия 0

0

ео

(4)

0

где V logari.

Соответственно разрядность счетчика 10 - 1 + V.

Поступление нового задерживаемого импульса до считывания предыдущего оче5 видно не нарушает работы устройства, поскольку он просто записывается в соответствующую ячейку и будет считан с такой же задержкой, как и предыдущий.

Установка счетчика 14 осуществляется по дачей на его вход сброса потенциала в момент прихода сдвоенного импульса, которым защи4)рован управляющий импульс тиристора в первой фазе преобразователя. Каждый приходящий на вход счетчика 11 импульс задерживается на такт сдвиго- в,з1м регистром дешифрации 12 и поступает

5 I а вход элемента И 13i, поэтому по приходу (Двоенного импульса на выходе элемента И 13| формируется положительный потенциал, подаваемый на вход сброса счетчика 4|, осушествляя таким образом дешиф0 рацию.

После сдвоения имульсов, формируемых на выходе счетчика 14|, в формирователе 1о| они подаются на управляющие входы первого тиристорного преобразователя. Блок задержки записи кода фазового

5 сдвига 22i, на вход которого также подаются импульсы управления с соответствующего выхода демультиплексора 20, формирует импульс, инициирующий запись в соответствующий регистр 211, задержанный на интервал времени, который определяется ди0 намикой работы тиристорных преобразова телей. Это позволяет избежать повторное считывание информации в том случае, если на входе регистра 21i код фазового сдвига увеличивается сразу после появления управJ- ляющего импульса, что может привести к неправильному распределению управляющих импульсов по каналам.

В следующих тактах цик.та аналогичная последовательность операций повторяется по отношению к импульсам управ;1ения остальных тиристорных преобразователей.

Таким образом, применение в данном устройстве по сравнению с известными новых элементов, а именно фиксатора нулевого значения, регистров кодов фазового сдвига 211-21п, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22i-22„, позволяет повы- сить надежность работы цифрового устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется в течение одного периода частоты сети.

Формула изобретения

Цифровое устройство для управления ведомым сетью преобразователем, содержащее по числу фаз пигающей сети фильт- ры, входы которых предназначены .для подключения к фазам сетевого напряжения, выходы пофазно подключены к входам нуль- органов, выходами подключенных к информационным входам мультиплексора, к выхо ду которого подключены ждущий мультивибратор и первый вход элемента ИЛИ, выход ждущего мультивибратора подключен к входу счетчика номера фазы преобразователя, выход которого подключен к адресной пине мультип.чексора, сдвиговый регистр щифрации, вход которого подключен к выходу нуль-органа первой фазы, выход - к вто рому входу элемента ИЛИ, выход которого подключен к информационному входу 1ератив}1ого запоминающего блока, генера- 1 ,р тактовых импульсов, выход которого под- ключен к входу выборки оперативного запоминающего блока и к входу счетчика номера тиристорного преобразователя по числу тиристорных преобразователей, узлы формирования выходных импульсов, каждый из которых содержит сдвиговый регистр дещиф- рации, э. темент И, счетчик номера тиристора и формирователь сдвоенных импульсов, вход

сдвигового регистра дешифрации объединен с вторым входом элемента И и счетным входом счетчика номера тиристора и об разует вход узла формирования выходных импульсов, выход сдвигового регистра дешифрации соединен с первым входом элемента И, выход которого соединен с входом сброса счетчика номера тиристора, выход которого соединен с входом формирователя сдвоенных импульсов, отличающееся тем, что, с целью улучшения надежности работы, оно снабжено фиксатором нулевого значения, мультиплексором кодов фазового сдвига, регистром адреса, сумматором, демуль- типлексором, по числу тиристорных преобразователей регистрами кодов фазового сдвига и блоками задержки записи кода, причем выход счетчика номера тиристорного преобразователя соединен с входом фиксатора нулевого значения и адресными шинами демультиплексора и мультиплексора фазового сдвига, информационные входы которого соединены с выходами регистров кодов фазового сдвига, входы которых предназначены для подключения к нсточнику кодов фазового сдвига, выход фиксатора первого значения соединен с входом блокировки мультиплексора кодов фазового сдвига, с входом записи регистра адреса, с входом разрешения записи оперативного запоминающего блока и с входом переноса сумматора,, вход сложения которого соединен с выходом мультиплексора кодов фазового сдвига, а выход - с адресной шиной оперативного запоминающего блока и с входной щиной регистра адреса, выход оперативного запоминающего блока соединен с информационным входом демультиплексора, п выходов которого по числу тиристорных преобразователей соединены соответственно с входами узлов формирования входных импульсов, а вход каждого узла формирования выходных импульсов объединен с входом соответствующего блока задержки записи кода фазового сдвига, выходы которых соответственно подключены к управляющим входам регистров кодов фазового сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое устройство для управления ведомым сетью преобразователем | 1985 |

|

SU1259440A1 |

| Устройство поиска шумоподобного сигнала | 1988 |

|

SU1540020A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2502128C2 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ СДВИГОВ СЛУЧАЙНЫХ СИГНАЛОВ | 2012 |

|

RU2500025C2 |

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

Изобретение относится к электротехнике и может быть использовано в статических преобразователях. Цель изобретения - улучшение динамических характеристик и повышение надежности. За счет введения в устройство для управления преобразователем фиксатора нулевого значения, регистров кодов фазового сдвига 21i-21, мультиплексора кодов фазового сдвига 17, регистра базового адреса 18, сумматора 19 и блоков задержки записи кода фазового сдвига 22:-22 обеспечивается надежная работа устройства в динамических режимах, когда фазовая задержка импульсов значительно изменяется в течение одного гериода частоты сети. 2 ил. S (Л 00 00 О5 а оо /

| Авторское свидетельство СССР № 1184060, кл | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ управления тиристорным инвертором | 1985 |

|

SU1261071A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-03-15—Публикация

1986-03-17—Подача