(Л

оо сх оо

гч

Изобретение относится к измерительной технике, может быть использовано для измерения отношения часто или периодов, а также частоты или пе риода электрических сигналов и является усовершенствованием устройства по авт.св. № 1308919.

1,ель изобретения - расширение функциональных возможностей за счет обеспечения возможности определения отсутствия одной из входных частот.

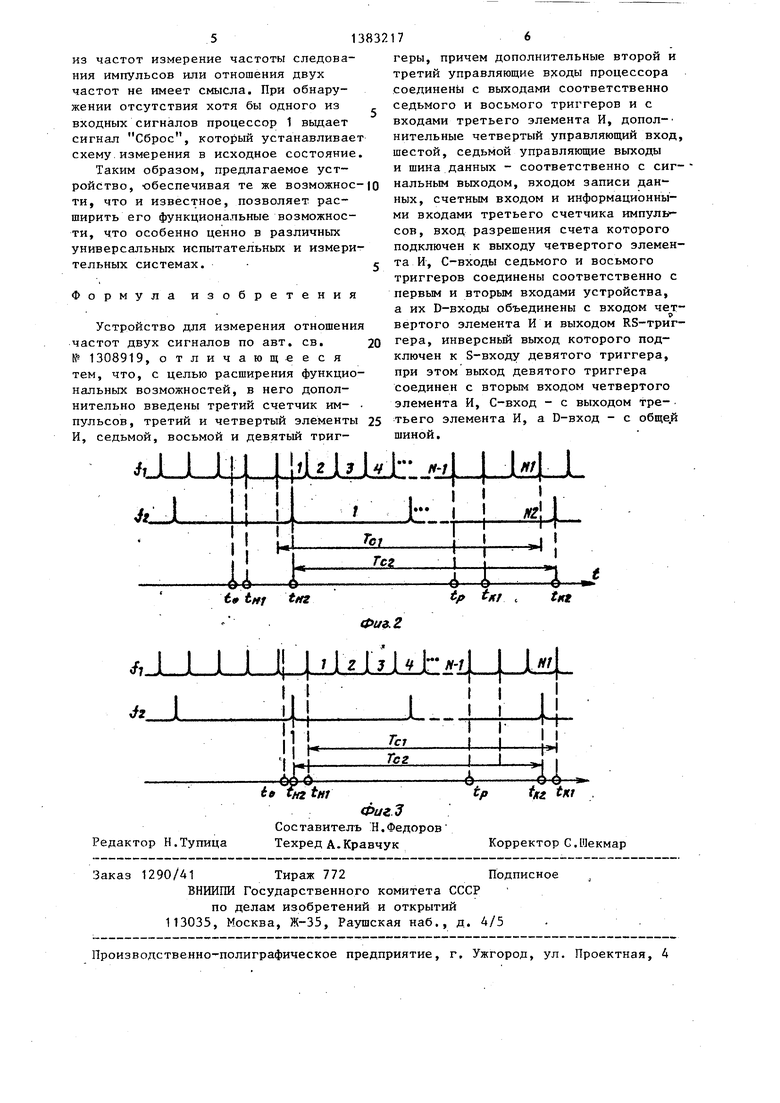

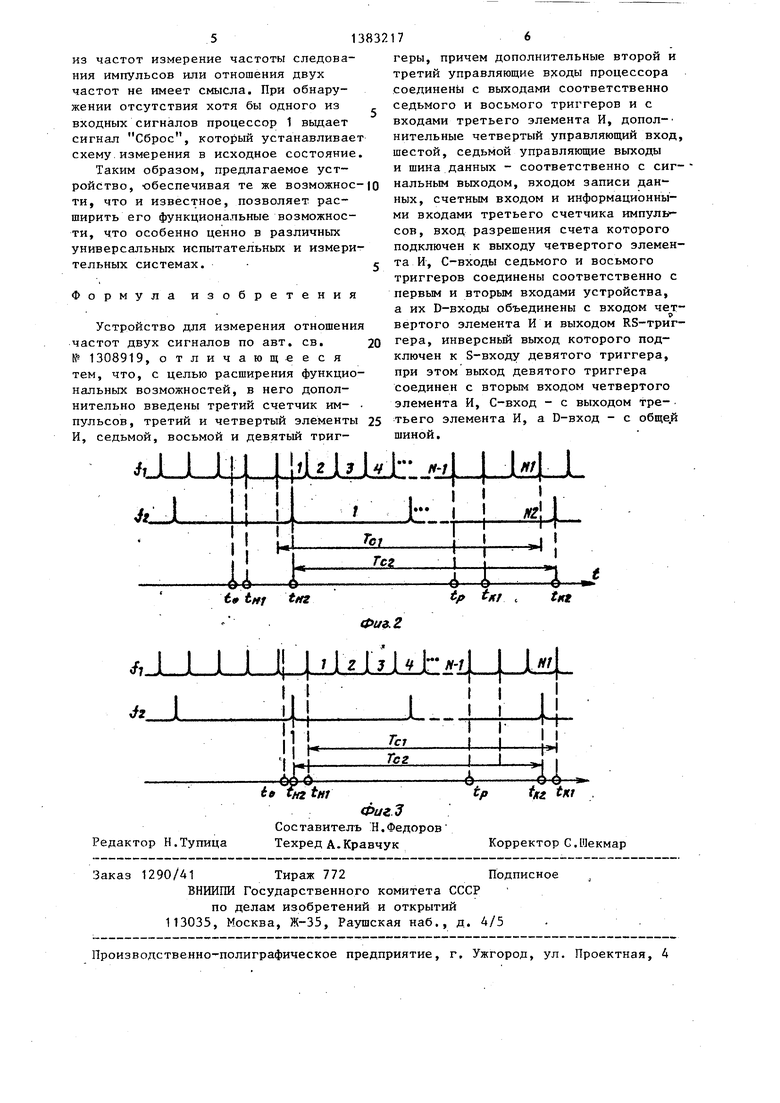

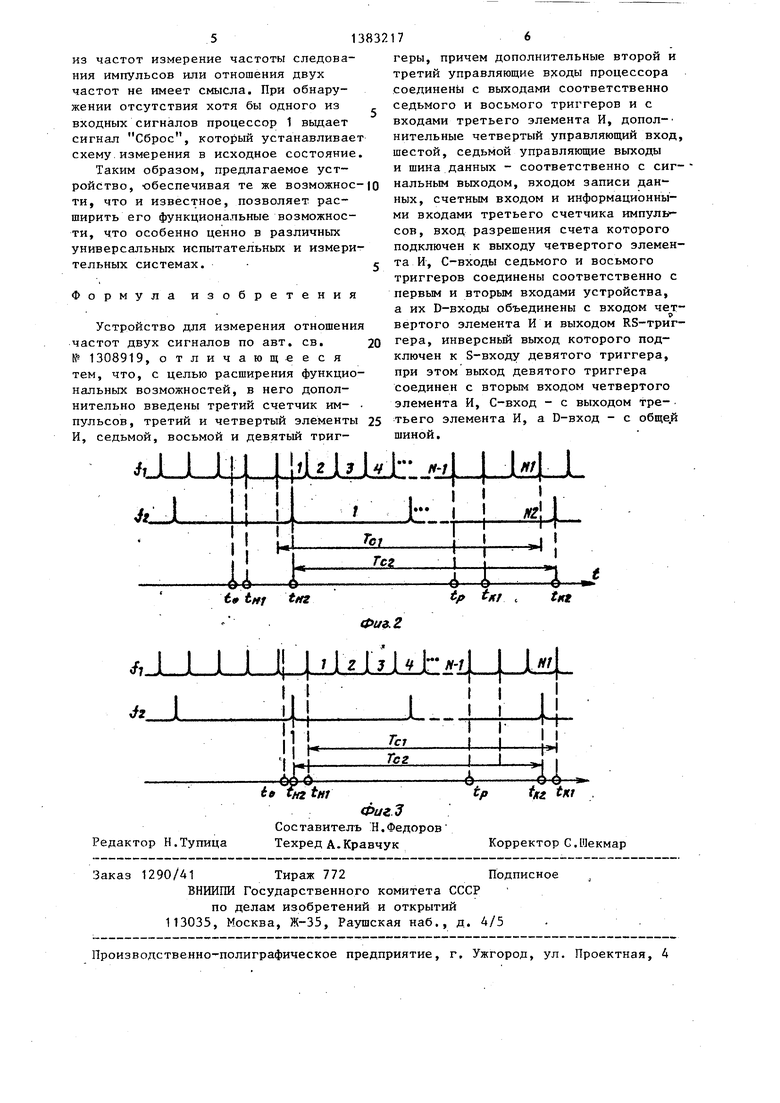

На фиг.1 приведена структурная схема устройства; на фиг,2 и 3 - временные диаграммы, поясняющие его ра- боту.

Устройство содержит процессор 1, счетчики 2-4 импульсов, RS-триггер 5 триггеры 6-14, элементы ШШ 15 и 16, элементы И 17-20, вход 21 частоты f вход 22 частоты f и шину 23 данных. Вход 21 частоты f, объединен с С-вхо дами триггеров 6, 10, 12 и входом элемента И 18, выход которого соединен со счетным входом счетчика 2 импульсов, а вход 22 частоты f - с С-входами триггеров 7, 11, 13 и входом элемента И 19, выход которого соединен со счетным входом счетчика 3 импульсов о Выход RS-триггера 5 об1:,единен с D-входом триггера 6, 7, 12,, 13 и входом элемента И 20, выход которого подключен к входу разрешения счета счетчика 4.импульсов, а ин версный выход RS-триггера 5 соединен с S-входом триггера 14, выход ко- торого подключен к второму входу элемента И 20. Выход триггера 6 объединен с D-входами триггеров 8, 11 и С входом триггера 9, выход ко- торого соединен с R-входом триггера 11, а выход триггера 7 - с D-входами триггеров 9, 10 и С-входом триггера 8, выход которого соединен с R-входом триггера 10. Выходы триггеров Ю и 11 соединены с входами элемента ИЛИ 15, выход которого объединен с вторыми входами элементов И 18, 19 и управляющим входом процессора 1, Уп- равляюш;ий выход процессора 1 соединен с 5 входом RS-триггера 5, а сигнальные выходы счетчиков 2 и 3 импульсов подключены к входам элемента И 16, выход которого соединен с R- входом RS-триггера 5. Выход тригге- pa 12 объединен с входом элемента И 17 и вторым управляющим входом процессора 1, а выход триггера 13 - с вторым входом элемента И 17 и третьи

управляющим входом процессора 1,,четвертый управляющий вход которого подключен к сигнальному выходу счетчика 4 .импульсов. Выход элемента И 17 соединен с С-входом триггера 14, D-вхой которого соединен с общей шиной. Шина данных процессора 1 объединена с информационными входами и выходами счетчиков 2-4 импульсов, входы .записи данных которых подключены соответственно к второму, третьему и шестому, а входы чтения данных - соответственно к четвертому, пятому и седьмому управляющим выходам процессора 1

Устройство работает следующим образом.

Перед началом измерений процессор 1 заносит в счетчики 2 и 3 импуль- сов код числа N-1, где N - некоторое заданное число, а в счетчик 4 импульсов код числа L, которое соответствует требуемому минимально необхо- димому времени измерения. Число L выбирается из условия

L7,I- , 1ф

где Т узд, - минимально необходимое

1

время измерения;

- период следования импуль- сов фиксированной частоты с шестого выхода процессора 1 на счетный вход счетчика 4 импульсов. При этом триггеры 5-7 и 10-13, находятся в нулевом, а триггеры 8 и 9 - « в произвольном состояниях. Сигнал 1 с инверсного выхода RS-триггера 5 устанавливает триггер 14 в единичное состояние, а О с его прямого выхода через элемент И 20 запрещает счет импульсов в счетчике 2 импульсов, «оторьй сброшен сигналом от процессора 1.

В момент tg (фиг.2 и 3) начала измерения процессор 1 вырабатывает на своем первом управляющем выходе сигнал 1, который переводит RS- триггер 5 в единичное состояние. Сигнал 1 с выхода RS-тpиггqpa 5 через элемент И 20 разрешает счет импульсов в счетчике 4 импульсов. Одновременно сигнал О с инверсного выхода RS-триггера 5 разрешает запись О в триггер 14. Ближайшие после t(, импульсы частот f, и f (моменты t ni и t,) заносят 1 с выхода RSтриггера 5 соответственно в триггеры 6, 12 и 7, 13. Если первым после момента to приходит импульс частоты f, (фиг.2), то первыми устанавливаются в единичное состояние триггеры 6 и 12. Переключение выходного сигнала триггера 6 из О в 1 записывает О с выхода триггера 7 в триггер 9, разрешая запись 1 в триггер 11. Ближайший импульс частоты f (момент t,), кроме записи 1 в триггеры 7 и 13, записывает 1 в триггер 11, 1 с выхода которого через элемент И-15 разрешает прохождение импульсов частот f, и f соответственно через элементы И 18 и 19 на счетные входы счетчиков 2 и 3 импульсов. Одновременно переключение выходного сигнала триггера 13 из О в 1 через элемент И 17 записывает О в триггер 14, который через элемент И 20 сбрасывает в О счетчик А импульсов, и удерживает его в этом состоянии до момента окончания изме- р«ния (момент t ц) Переключение выходного сигнала триггера 7 из О в 1 записывает 1 в триггер 8, 1 с выхода которого удерживает триггер 10 в нулевом состоянии в течение данного измерения. При равенстве одного из подсчитываемых в счетчиках 2 или 3 импульсов количеств импульсо частот f , или fj заданному числу N-1 (момент t ) в нем срабатывает с:хема сравнения и на его выходе появляется 1, которая через элемент И 16 сбрасывает RS-триггер 5, сигнал О с выхода которого через элемент И 20 блокирует счетчик 4 импульсов на время между измерениями. Ближайшие после момента to импульсы частот f, и f,j записывают О в триггеры 6, 12 и 7, 13, а ближайший импульс частоты f (момент t ,5) следующий после ближай шего с момента tp импульса частоты f (момент t к,), записывает О в триггер 11.

Переключение выходного сигнала триггера 11 из 1 в О через элемент ИЛИ 15 свидетельствует об окончании счета импульсов, а О с выхода элемента ИЛИ 15 запрещает прохождение импульсов частот f, и fJ через элементы И 18 и 19 на счетные входы счетчиков 2 и 3 импульсов. Процессор 1 считывает содержимое счетчиков 2 и 3 импульсов и производит

п

.. с

0

необходимые вычисления из соотношения

NCI

f, N;;

где N и содержимое счетчиков 2 и 3 импульсов, соответственно, по окончании счета.

Если первым после момента t р приходит ближайший импульс частоты f (фиг.З), то первым устанавливаются в единичное состояние триггеры 7 и 13 (момент tj,). Переключение выходного сигнала триггера 7 из О в 1 записывает О с выхода триггера 6 в триггер 8, а ближайший и 5пyльc частоты f (момент t„,), кроме записи 1 в триггеры 6 и 12, записывает 1 с выхода триггера 7 в триггер 10, 1 с выхода которого через элемент ИЛИ 15 разрешает счет импульсов обеих частот. Переключение выходного сигнала триггера 12 через элемент И 17, записьтая О в триггер 14, тем самьм блокирует счетчик 4 импульсов. Переключение выходного сигнала триггера 6 из О в 1 записывает 1 в триггер 9, с выхода которого удерживает в течение всего измерения триггер-1.1 в нулёЪом состоянии.

Далее устройство работает так же, как и в предыдущем случае, за исключением того, что ближайший после момента -t, импульс частоты f (момент t 1,) записывает О с выхода тригге- ра 7 в триггер 10, переключение выходного сигнала которого из 1 в О приводит 1 такому же изменению состояния элемента ИЛИ 15, как рассмотрено вьш1е.

При отсутствии хотя бы одной из частот f а fj сигнал О с выхода соответственно триггеров 12 и 13 блокирует элемент И 17. Триггер 14 остается в единичном состоянии и разрешает дальнейший счет импульсов счетчику 4 импульсов. При равенстве подсчитываемого в счетчике 4 импульсов количества импульсов частоты f числу L в нем срабатывает схема сравнения и на выходе появляется 1, что свидетельствует об окончании измерения.

Дальнейшее считывание содержимого jсчетчиков 2 и 3 импульсов необязательно, так как при отсутствии одной

из частот измерение частоты следования импульсов или отношения двух частот не имеет смысла. При обнаружении отсутствия хотя бы одного из входных сигналов процессор 1 вьздает сигнал Сброс, который устанавливает схему,измерения в исходное состояние.

Таким образом, предлагаемое устройство, обеспечивая те же возможноети, что и известное, позволяет расширить его функциональные возможности, что особенно ценно в различных универсальных испытательных и измерительных системах.

Формула изобретения

Устройство для измерения отношения частот двух сигналов по авт. св. IP 1308919, отличающееся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены третий счетчик им- пульсов, третий и четвертый элементы И, седьмой, восьмой и девятый триггеры, причем дополнительные второй и третий управляющие процессора соединены с выходами соответственно седьмого и восьмого триггеров и с входами третьего элемента И, допол- нительные четвертый управляющий вход, шестой, седьмой управляющие выходы и шина данных - соответственно с сигнальным выходом, входом записи данных, счетным входом и информационными входами третьего счетчика импульсов , вход разрешения счета которого подключен к выходу четвертого элемента И, С-входы седьмого и восьмого триггеров соединены соответственно с первым и вторым входами устройства, а их D-входы объединены с входом чет9

вертого элемента И и выходом RS-триг- гера, инверсньш выход которого подключен к S-входу девятого триггера, при этом выход девятого триггера соединен с вторым входом четвертого элемента И, С-вход - с выходом третьего элемента И, а D-вход - с обще.й шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения отношения частот двух сигналов | 1985 |

|

SU1308919A1 |

| Преобразователь код-временной интервал | 1984 |

|

SU1248073A1 |

| Цифровой регулятор угловой скорости дугостаторного асинхронного двигателя | 1984 |

|

SU1203481A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Преобразователь амплитуда-код нестационарных механических колебаний | 1987 |

|

SU1481888A1 |

| Цифровой фазовый дискриминатор | 1986 |

|

SU1343542A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Система для передачи телеизмерительной информации | 1981 |

|

SU1037313A1 |

| Устройство для управления ведущим шаговым двигателем | 1981 |

|

SU999022A1 |

| Контроллер для связи процессоров с общей магистралью | 1988 |

|

SU1575197A1 |

J J UJ} |LlXJil b i| |J |

2

Фиг. г

| Устройство для измерения отношения частот двух сигналов | 1985 |

|

SU1308919A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-13—Подача