1

1236487

и.икфетение относится к вычислительной технике, а именно к функциональному контролю ЭВМ.

Цель изобретения - повьгаение достоверности контроля.

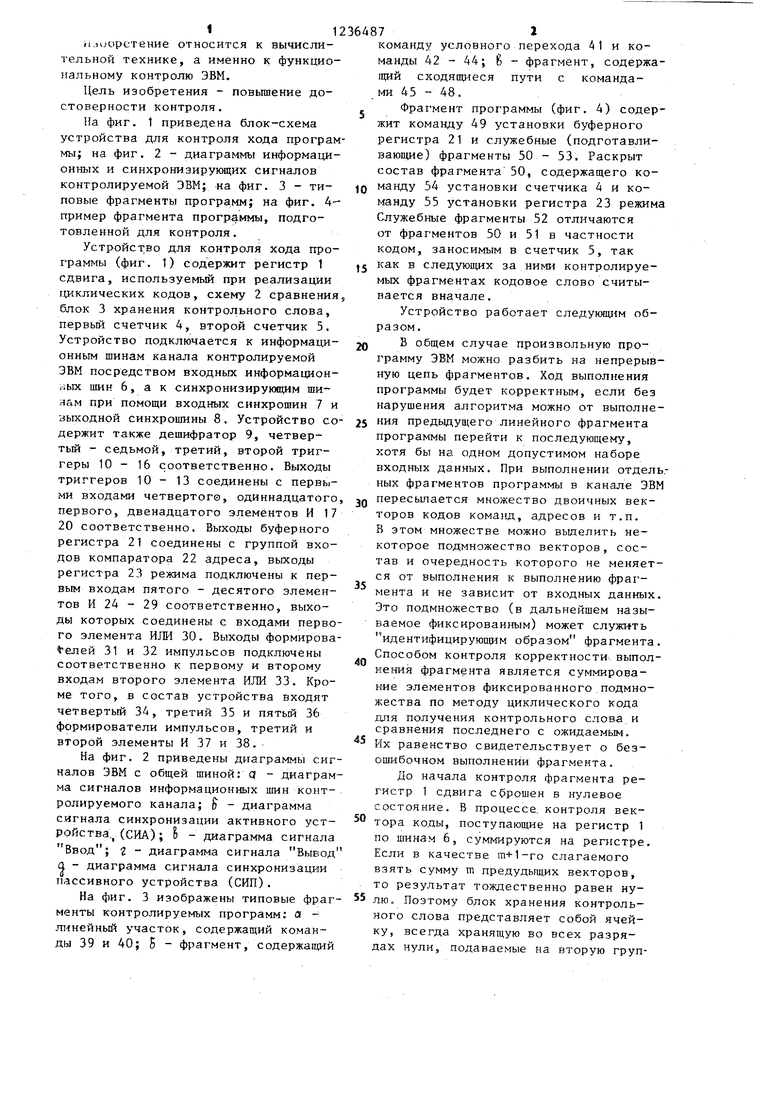

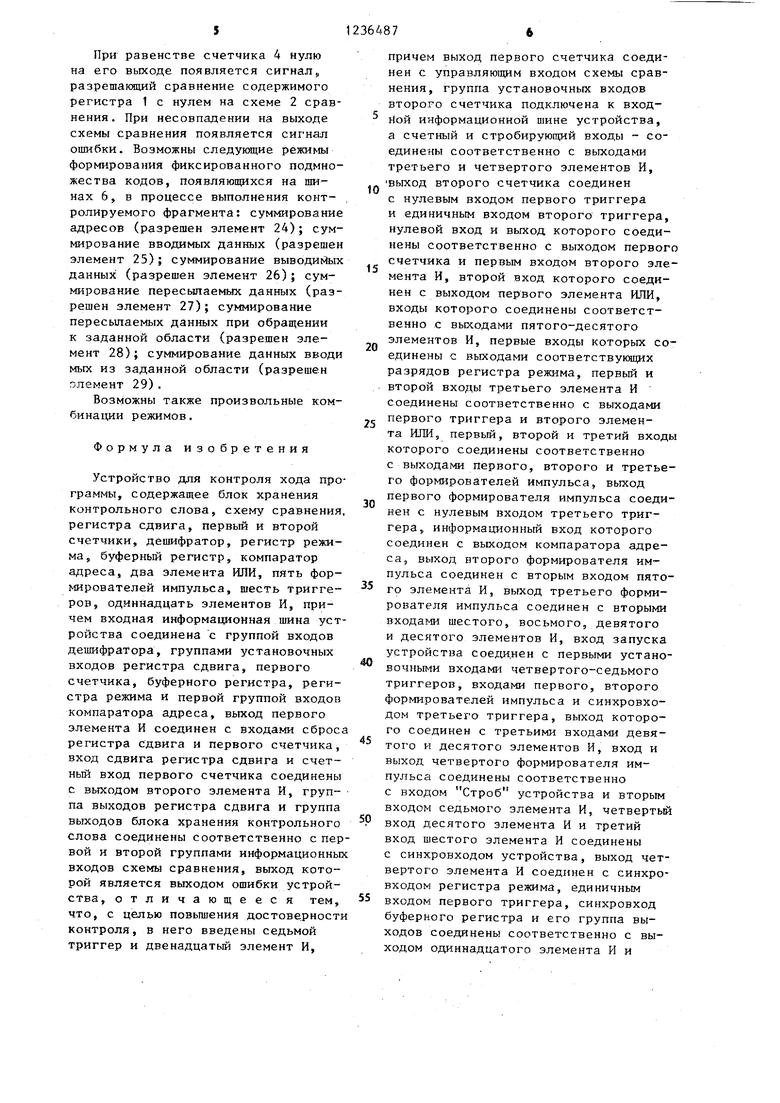

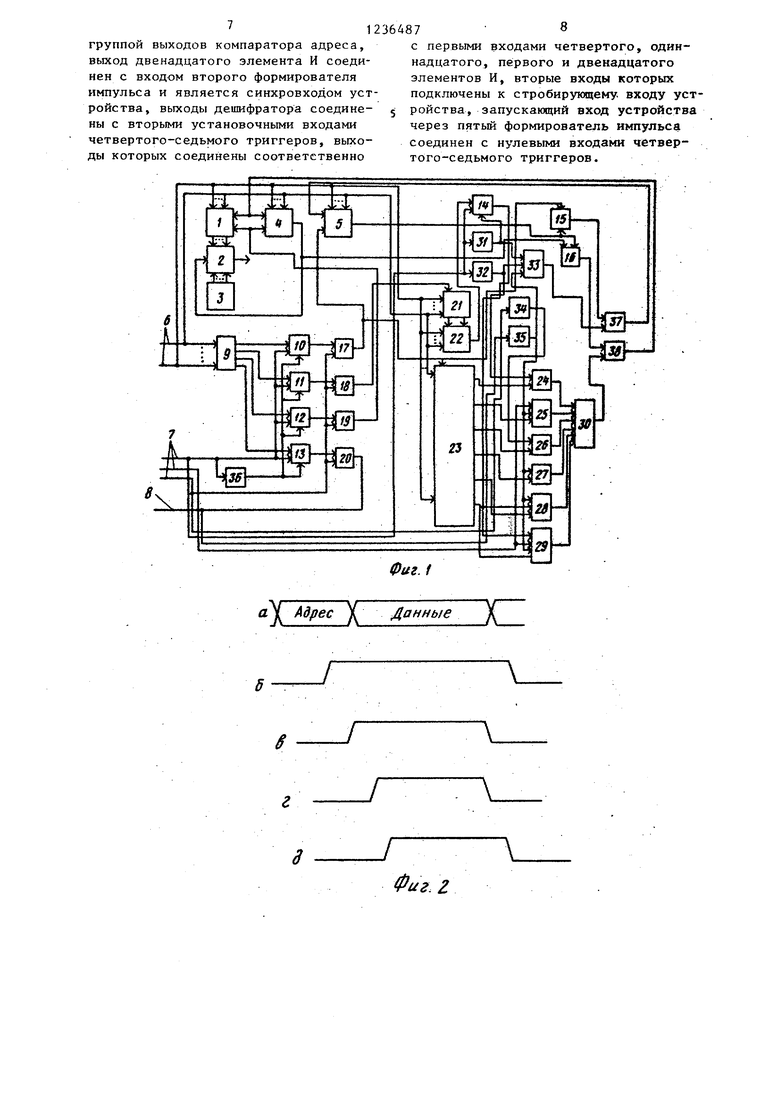

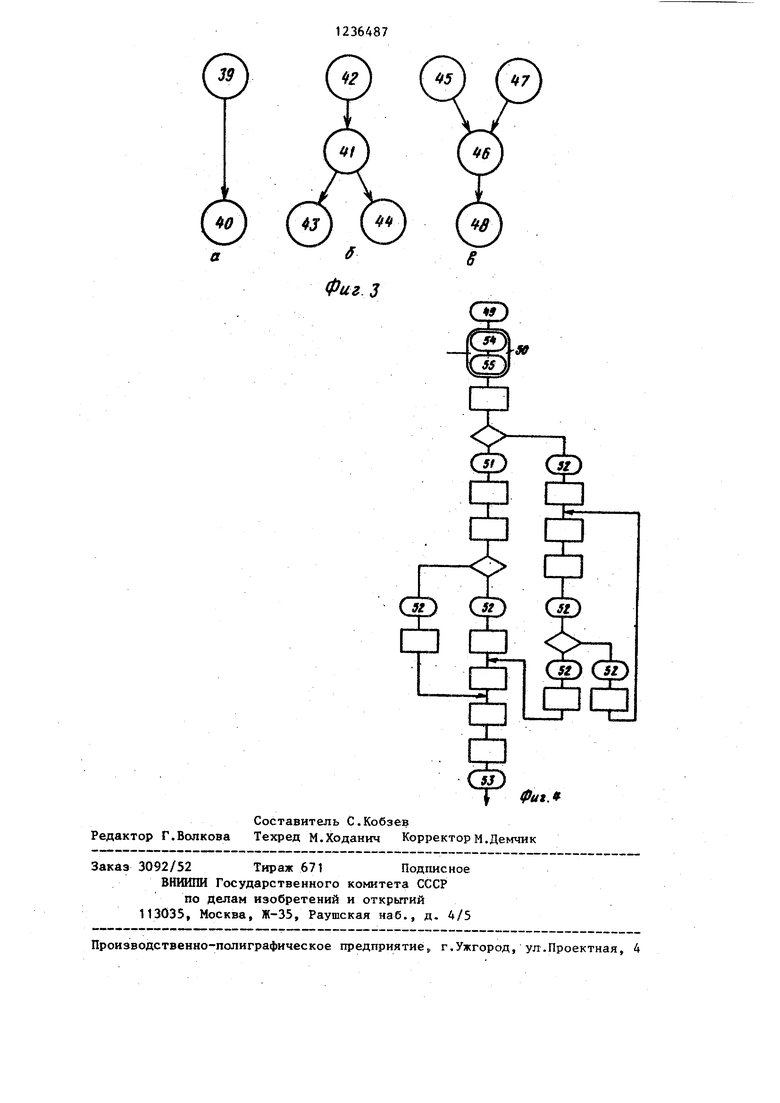

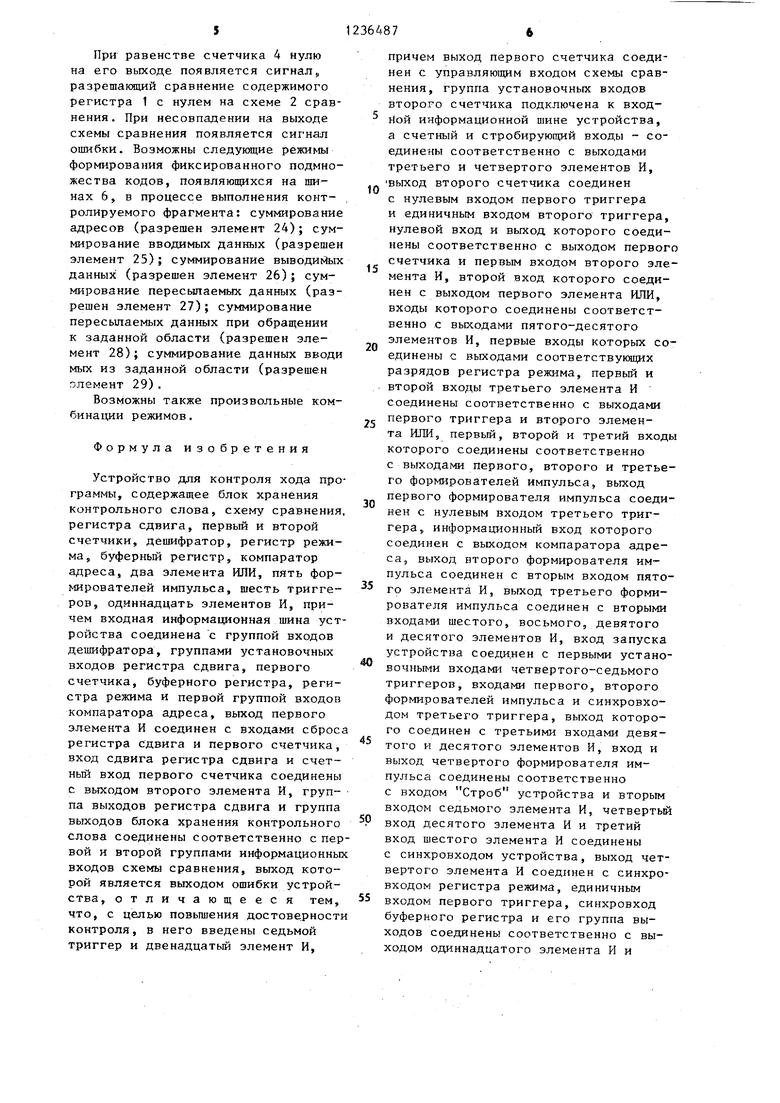

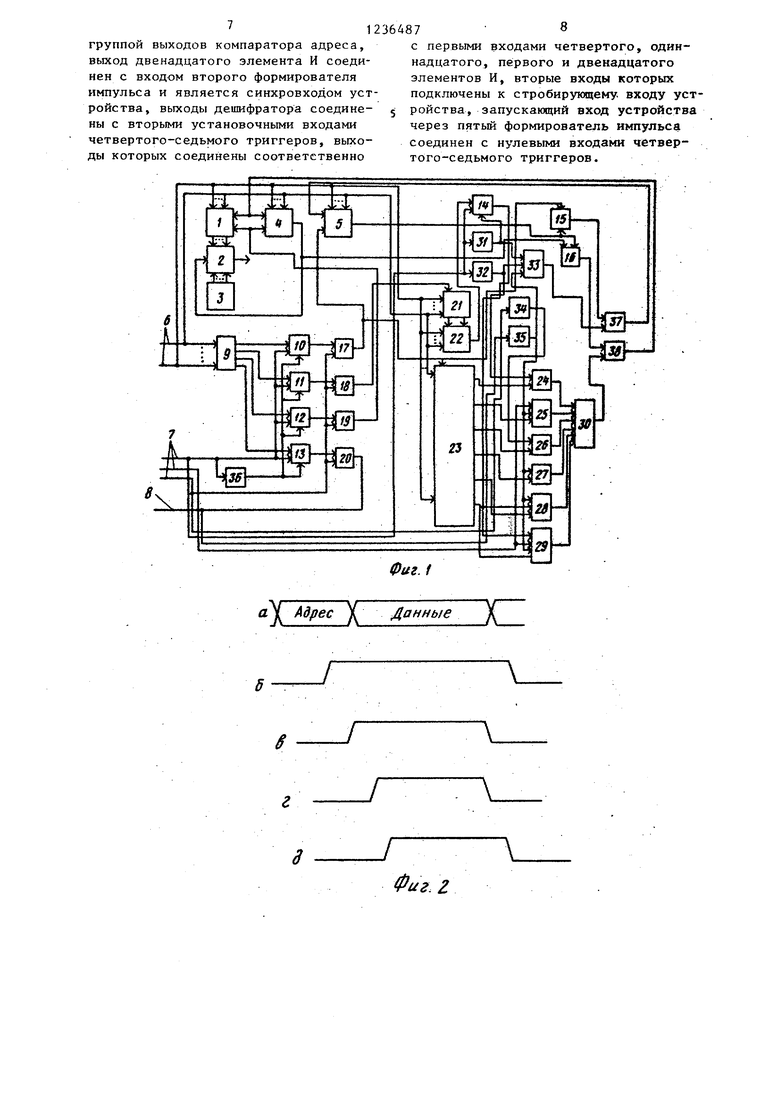

На фиг. 1 приведена блок-схема устройства для контроля хода программы; на фиг. 2 - диаграммь информади- онных и синхронизирующих сигналов контролируемой ЭВМ; на фиг. 3 - ти- повые фрагменты программ; на фиг. А пример фрагмента прогр4ммы, подготовленной для контроля.

Устройство для контроля хода программы (фиг. 1) содержит регистр 1 сдвига, используемьй при реализации циклических кодов, схему 2 сравнения блок 3 хранения контрольного слова, первьм счетчик 4, второй счетчик 5. Устройство подключается к информаци- онным шинам канала контролируемой ЭВМ посредством входных информацион- .1ых шин 6, а к синхронизирукицим шинам при помощи входных синхрошин 7 и выходной синхрошины 8, Устройство со держит также дешифратор 9, четвертый - седьмой, третий, второй три1- геры 10 - 16 соответственно. Выходы триггеров 10 - 13 соединены с первыми входами четвертого, одиннадцатого первого, двенадцатого элементов И 17 20 соответственно. Выходы буферного регистра 21 соединены с группой входов компаратора 22 адреса, выходы регистра 23 режима подключены к первым входам пятого - десятого элементов И 24 - 29 соответственно, выходы которых соединены с входами первого элемента ИЛИ 30. Выходы формирова елей 31 и 32 импульсов подключены соответственно к первому и второму входам второго элемента ИЛИ 33. Кроме того, в состав устройства входят четвертый 34, третий 35 и пятый 36 формирователи импульсов, третий и второй элементы И 37 и 38.

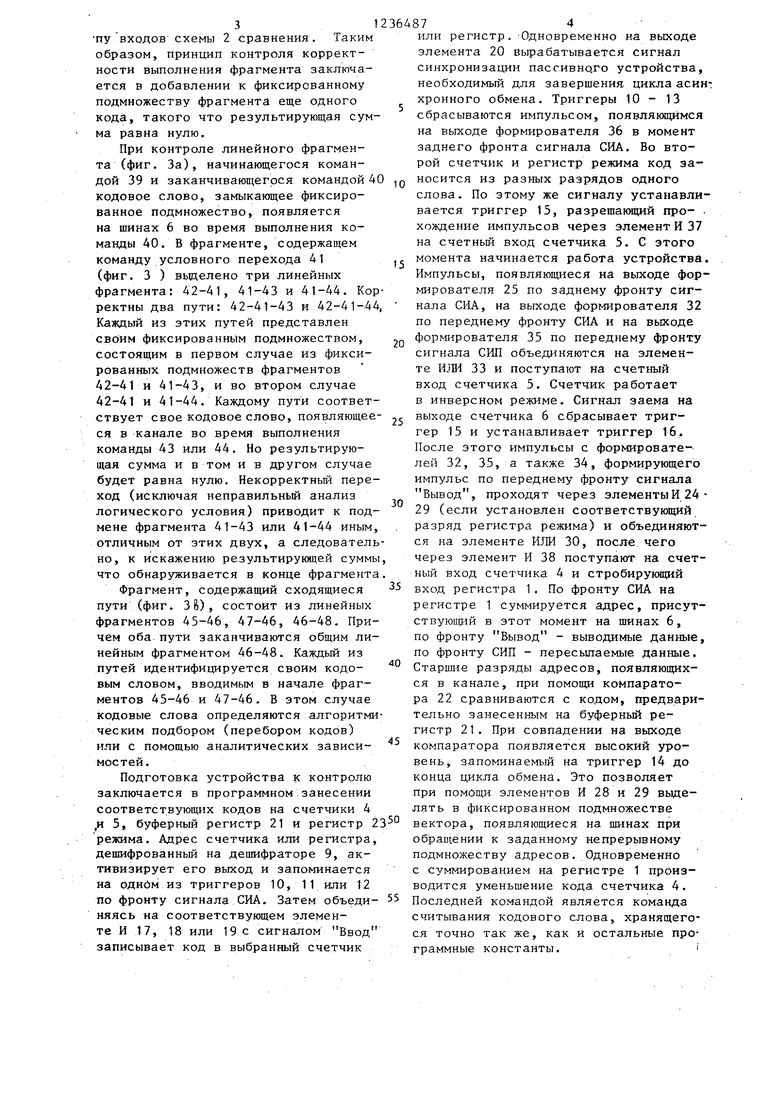

На фиг. 2 приведены диаграммы сигналов ЭВМ с общей шиной: О - диаграмма сигналов информационных шин контролируемого канала; - диаграмма сигнала синхронизации активного устройства, (СИЛ) ; & - диаграмма сигнала 1 - диаграмма сигнала Вывод а - диаграмма сигнала синхронизации пассивного устройства (СИП).

На фиг. 3 изображены типовые фраг менты контролируемых программ: и - линейный участок, содержащий команды 39 и 40; S - фрагмент, содержащий

5 д

5

5

0

3

0

команду условного перехода 41 и команды 42 -- 44; 6 - фрагмент, содержащий сходя циеся пути с команда- ivm 45 - 48.

Фрагмент программы (фиг. 4) содержит команду 49 установки буферного регистра 21 и служебные (подготавливающие) фрагменты 50 - 53. Раскрыт состав фрагмента 50, содержащего команду 54 установки счетчика 4 и команду 55 установки регистра 23 режима Служебные фрагменты 52 отличаются от фрагментов 50 и 51 в частности кодом, заносимым в счетчик 5, так как в следуюнщх за ними контролируемых фрагментах кодовое слово считывается вначале.

Устройство работает следующим образом.

В общем случае произвольную программу ЭВМ можно разбить на непрерывную цепь фрагментов. Ход выполнения программы будет корректным, если без нарушения алгоритма можно от выполнения предыдущего линейного фрагмента программы перейти к последующему, хотя бы на одном допустимом наборе входных данных. При выполнении отдель.- ных фрагментов программы в канале ЭВМ пересылается множество двоичных векторов кодов команд, адресов и т.п. В этом множестве можно выделить некоторое подмножество векторов, состав и очередность которого не меняется от выполнения к выполнению фрах - мента и Не зависит от входных данных. Это подмножество (в дальнейшем называемое фиксированным) может служить идентифицирующим образом фрагмента. Способом контроля корректности выполнения фрагмента является суммирование элементов фиксированного подмножества по методу циклического кода для получения контрольного слова и сравнения последнего с ожидаемым. Их равенство свидетельствует о безошибочном выполнении фрагмента.

До начала контроля фрагмента регистр 1 сдвига сброшен в нулевое состояние. В процессе, контроля вектора коды, поступающие на регистр 1 по шинам 6, суммируются на регистре. Если в качестве m+1-ro слагаемого взять сумму m предудыщих векторов, то результат тож;дественно равен нулю. Поэтому блок хранения контрольного слова представляет собой ячейку, всегда хранящую во всех разрядах нули, подаваемые на вторую груп

пу входов схемы 2 сравнения. Таким образом, принцип контроля корректности выполнения фрагмента заключается в добавлении к фиксированному подмножеству фрагмента еще одного кода, такого что результирующая сумма равна нулю.

При контроле линейного фрагмента (фиг. За), начинающегося командой 39 и заканчивающегося командой 4 кодовое слово, замыкающее фиксированное подмножество, появляется на шинах 6 во время выполнения команды 40. В фрагменте, содержащем команду условного перехода 41 (фиг. 3 ) вьщелено три линейных фрагмента: 42-41, 41-43 и 41-44. Корректны два пути: 42-41-43 и 42-41-44 Каждый из этих путей представлен своим фиксированным подмножеством, состоящим в первом случае из фиксированных подмножеств фрагментов 42-4 Г и 41-43, и во втором случае 42-41 и 41-44. Каждому пути соответствует свое кодовое слово, появляющееся в канале во время выполнения команды 43 или 44. Но результирующая сумма и в том и в другом случае будет равна нулю, Некорректньш переход (исключая неправильный анализ логического условия) приводит к подмене фрагмента 41-43 или 41-44 иным, отличным от этих двух, а следовательно, к искажению результирующей суммы что обнаруживается в конце фрагмента

Фрагмент, содержащий сходящиеся пути (фиг. 3 и), состоит из линейных фрагментов 45-46, 47-46, 46-48. Причем оба пути заканчиваются общим линейным фрагментом 46-48. Калсдый из путей идентифицируется своим кодовым словом, вводимым в начале фрагментов 45-46 и 47-46. В этом случае кодовые слова определяются алгоритмическим подбором (перебором кодов) или с помощью аналитических зависимостей.

Подготовка устройства к контролю заключается в программном занесении соответствующих кодов на счетчики 4 ,и 5, буферный регистр 21 и регистр 2 режима. Адрес счетчика или регистра, дешифрованный на дешифраторе 9, активизирует его выход и запоминается на одним из триггеров 10, 11 или 12 по фронту сигнала СИЛ. Затем объеди- няясь на соответствующем элементе И 17, 18 или 19 с сигналом Ввод записывает код в выбранный счетчик

f5

20

25

,Q

° 5

30

35

0

5

или регистр. -Одновременно на выходе элемента 20 вырабатывается сигнал синхронизации пассивного устройства, необходимый для завершения, цикла асин: хронного обмена. Триггеры 10 - 13 сбрасываются импульсом, появляющимся на выходе формирователя 36 в момент заднего фронта сигнала СИА. Во второй счетчик и регистр режима код заносится из разных разрядов одного слова. По этому же сигналу устанавливается триггер 15, разрешакнций про- . хождение импульсов через элемент И 37 на счетный вход счетчика 5. С этого момента начинается работа устройства. Импульсы, появляющиеся на выходе формирователя 25 по заднему фронту сигнала СИА, на выходе формирователя 32 по переднему фронту СИА и на выходе форм1фователя 35 по переднему фронту сигнала СИП объединяются на элементе ШВ- 33 и поступают на счетный вход счетчика 5. Счетчик работает в инверсном режиме. Сигнал заема на выходе счетчика 6 сбрасывает триггер 15 и устанавливает триггер 16. После этого импульсы с формирователей 32, 35, а также 34, формирующего импульс по переднему фронту сигнала Вывод, проходят через элементы И 24- 29 (если установлен соответствующий разряд регистра режима) и объединяются на элементе ИЛИ 30, после чего через элемент И 38 поступают на счетный вход счетчика 4 и стробирукщий вход регистра 1. По фронту СИА на регистре 1 суммируется адрес, присутствующий в этот момент на щинах 6, по фронту Вывод - выводимые данные, по фронту СИП - пересыпаемые данные. Старшее разряды адресов, появляющихся в канале, при помощи компаратора 22 сравниваются с кодом, предварительно занесенным на буферный регистр 21. При совпадении на выходе компаратора появляется высокий уровень, запоминаемый на триггер 14 до конца цикла обмена. Это позволяет при помощи элементов И 28 и 29 выделять в фиксированном подмножестве вектора, появляющиеся на щинак при обращении к заданному непрерывному подмножеству адресов. Одновременно с суммированием на регистре 1 производится уменьшение кода счетчика 4. Последней командой является команда считывания кодового слова, хранящегося точно так же, как и остальные программные константы.

При равенстве счетчика 4 нулю на его выходе появляется сигнал,, разрешающий сравнение содержимого регистра 1 с нулем на схеме 2 сравнения. При несовпадении на выходе схемы сравнения появляется сигигш ошибки. Возможны следующие режимы формирования фиксированного подмножества кодов, появляющихся на шинах 6, в процессе выполнения конт- ролируемого фрагмента: суммирование адресов (разрешен элемент 24); суммирование вводимых данных (разрешен элемент 25); суммирование выводимых данных (разрешен элемент 26); суммирование пересылаемых данных (разрешен элемент 27); суммирование пересыпаемых данных при обращении к заданной области (разрешен элемент 28); суммирование данных вводи мых из заданной области (разрешен элемент 29).

Возможны также произвольные комбинации режимов.

Формула изобретения

Устройство для контроля хода программы, содержащее блок хранения контрольного слова, схему сравнения регистра сдвига, первый и второй счетчики, дешифратор, регистр режима, буферный регистр, компаратор адреса, два элемента ИЛИ, пять формирователей импульса, шесть триггеров, одиннадцать элементов И, причем входная информационная шина устройства соединена с группой входов дешифратора, группами установочных входов регистра сдвига, первого счетчика, буферного регистра, регистра режима и первой группой входов компаратора адреса, выход первого элемента И соединен с входами сброс регистра сдвига и первого счетчика, вход сдвига регистра сдвига и счетный вход первого счетчика соединены с выходом второго элемента И, группа выходов регистра сдвига и группа выходов блока хранения контрольного слова соединены соответственно с первой и второй группами информационны входов схемы сравнения, выход которой является выходом ошибки устройства, отличающееся тем, что, с цепью повьш1ения достоверност контроля, в него введены седьмой триггер и двенадцатьш элемент И,

0

5

0

5

0

5

5

5

причем выход первого счетчика соединен с управляю111;им входом схемы сравнения, группа установочных входов второго счетчика подключена к вход- р(ой информационной шине устройства, а счетный и стробирующий входы соединены соответственно с выходами третьего и четвертого элементов И, ВЫХОД второго счетчика соединен с нулевым входом первого триггера и единичным входом второго триггера, нулевой вход и выход которого соединены соответственно с выходом первого счетчика и первым входом второго элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, входы которого соединены соответственно с выходами пятого-десятого элементов И, первые входы которых соединены с выходами соответствукнцих разрядов регистра режима, первый и второй входы третьего элемента И соединены соответственно с выходами первого триггера и второго элемента ИЛИ, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего формирователей импульса, выход первого формирователя импульса соединен с нулевым входом третьего триггера, информационный вход которого соединен с выходом компаратора адреса, выход второго формирователя импульса соединен с вторым входом пятого элемента И, выход третьего формирователя импульса соединен с вторыми входами шестого, восьмого, девятого и десятого элементов И, вход запуска устройства Соединен с первьгми установочными входами четвертого-седьмого триггеров, входами первого, второго формирователей импульса и синхровхо- дом третьего триггера, выход которого соединен с третьими входами девятого и десятого элементов И, вход и выход четвертого формирователя импульса соединены соответственно с входом Строб устройства и вторым входом седьмого элемента И, четвертьй вход десятого элемента И и третий вход шестого элемента И соединены с синхровходом устройства, выход четвертого элемента И соединен с синхровходом регистра режима, единичным входом первого триггера, синхровход буферного регистра и его группа выходов Соединены соответственно с выходом одиннадцатого элемента И и

71

группой выходов компаратора адреса, выход двенадцатого элемента И соединен с входом второго формирователя импульса и является синхровходом уст ройства, выходы дешифратора соединены с вторыми установочными входами четвертого-седьмого триггеров, выходы которых соединены соответственно

236487 8

с первыми входами четвертого, одиннадцатого, первого и двенадцатого элементов И, вторые входы которых подключены к стробирующему входу устройства, запускающий вход устройства через пятый формирователь импульса соединен с нулевыми входами четвертого-седьмого триггеров.

Фиг. 1 g У Мрес X ManHbie д

g

J

I

Фиг г

с«.) сю с«

п б с

фuг.

Редактор Г.Волкова

Составитель С.Кобзев

Техред М.Ходанич Корректор М.Демчик

Заказ 3092/52 Тираж 671 Подгшсное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие,, г.Ужгород, ул.Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для контроля микропроцессорной системы | 1985 |

|

SU1287161A1 |

| Устройство для контроля хода программ | 1989 |

|

SU1645960A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1501065A1 |

Изобретение относится к области вычислительной техники. Целью изобретения является повьшение достоверности контроля. Устройство содержит регистр сдвига, схему сравнения, блок хранения контрольного слова, счетчики, триггеры, элементы И, буферный регистр, компаратор адреса, регистр режима, элементы ИЛИ. 4 ил. к оо О5 4; ОО

| Патент США № 4108359, кл, G 06 F 11/08 | |||

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Патент США № 4099668, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1983-03-23—Подача