(Л

d

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная цифровая телеметрическая система | 1985 |

|

SU1280420A1 |

| Устройство для контроля параметров | 1986 |

|

SU1401483A1 |

| Устройство для определения границ микропика на контуре основного пика | 1987 |

|

SU1575209A1 |

| Устройство для приема многократно передаваемой информации | 1989 |

|

SU1647914A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для преобразования временных интервалов в двоичный код | 1980 |

|

SU945980A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1520531A1 |

| Функциональный преобразователь | 1982 |

|

SU1037272A1 |

| Устройство для приема сигналов, закодированных с избыточностью | 1988 |

|

SU1605275A2 |

| Адаптивное телеметрическое устройство | 1979 |

|

SU858060A1 |

Изобретение относится к централизованному контролю и может быть использовано при цифровой обработке в .реальном масштабе времени измеренных сигналов датчиков контролируемых параметров 5 искаженных случайными помехами. Цель изобретения - повышение быстродействия устройства. Устройство содержит первый 1 и второй 2 блоки памяти, первый 3 и второй 4 блоки вы

00

00 со

00

о

СП

питания, первый 5 и второй 6 блоки деления, первый 7 и второрг 8 блоки сравнения, первьй 9 и второй 10 счетчики, первый 11 и второй 12 блоки сложения, блок 13 извлечения квадратного корня, блок 14 умножения, квадратор 15, задатчик кодов 16, элемент

1

Изобретение относится к централизованному контролнр и может быть использовано при цифровой обработке в реальном масштабе времени измеренных сигна-лов датчиков контролируемых параметров , искаженных случайными помехами.

Целью изобретения является повышение быстродействия устройства.

Работа устройства основывается на следующем.

Для проверки достоверности измеренного на k-M цикле опроса (k 1,2,...) значения сигнала дат чика некоторого контролируемого пара метра X воспользуемся известньгм критерием: значение x k считается недос тсверН1.1М на уровне значимости |Ь , если

,|Hlis nl, (1)

де п - количество достоверных измеренных значений сигнала датчика пара-; метра X, .предшествовавших k-му измерению, ns2;

- квантиль распределения Стьюдента, Значения которого табулированы; - оценка среднего, вычисленная по h достоверным значениям х , г i,п по формуле

- ::

(2)

111 - несмещенная оценка дисперсии, также вычисленная по п достоверным

ИЛН 17, блок 18 регистрации и блок синхронизации. Поскольку в устроГ-т- ве нроверке на достоверность подвергается каждое измеренное значение ла- раметра после его измерения, то это повьшшет его быстродействие. 1 з,п. ф-лы, 3 ил., 1 табл.

значениям по фор-, муле

5 - ) 3)

10

15

Соотношения (1) - (3) неудобны для схемной реализации, так как содержат множители вида (п+ 1), 1/п и 1/{п-1).

Приведем соотношение (1) к виду, более удобному для схемной реализации.

Подставляя (3) в правую часть неравенства (1), получают

)

И

-jpW- H,

где

(4)

г .-| ГЧ- 1

ta n-1 К г - новые табулиронанр - п- 1

ные константы, зависящие от уровня значимости и количества достоверных данных п (значения для некоторых и приведены в табли- и.е) ;

(х(г) )Mii - 5:ме1ценная 40опенка среднего квадра- тического отклонения.

С.педонатечьнп, яераненс /гво (1) tie-- реписыг аетгя в виде

- I :, tp п X п . (5)

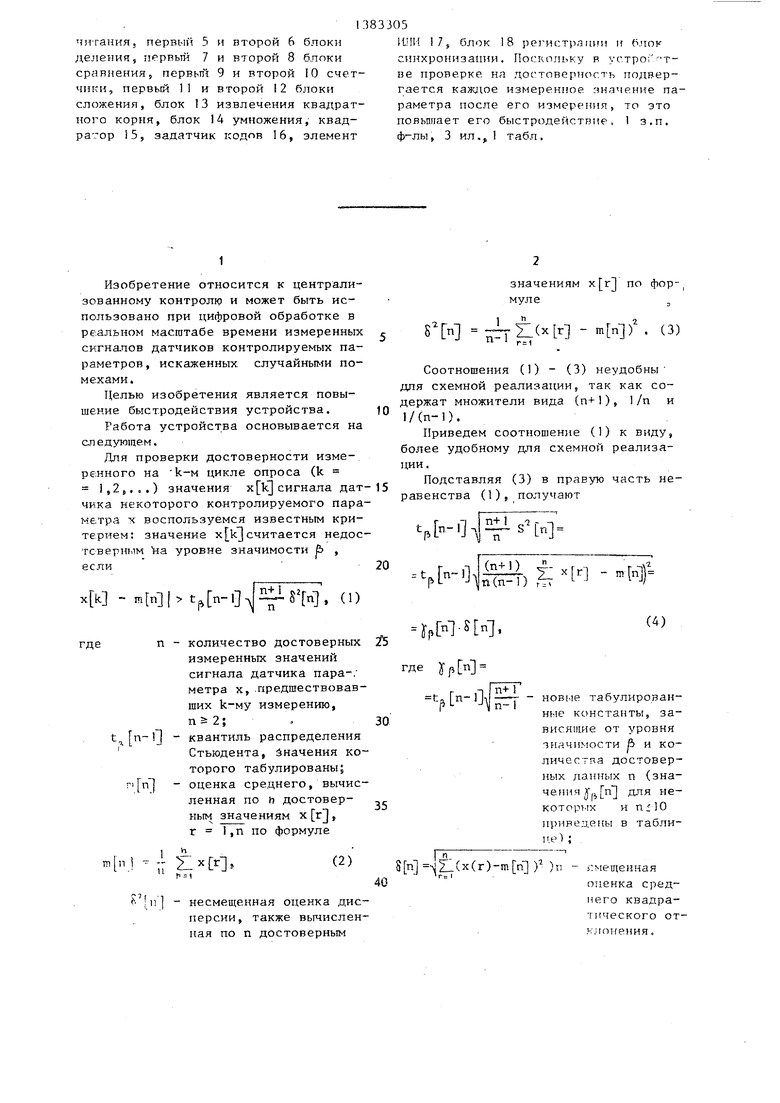

Значения констант J a цля различных В и п приведены в таблипе.

Если условие (5) выполнено, т.е. значение x k недостоверно, то при проверке на достоверность следующего измеренного значения оценки среднего и среднего квадратического отклонения, а также константа остаются теми же, что и для последнего из предшествующих достоверных значений.

Если условие (5) не. в{)Шолняется, т.е. значение достоверно, то при проверке на достоверность следующего измеренного значения оценки среднего и среднего квадратического отклонения пересчитываются С учетом значения рекуррентным формулам:

1 n+1

(), (6)

f +-.L. ((хИ-шМ) - ). Чо 0,,

a константа Jf n для n+1.

)

10

15

20

25

30

о

юС

35

40

45

50

) 55

Из того, что п. 5--2, следует, п при проверке на ;.1остове1м п:ть ш.рчо- го X l и второго X 2 15змеррчии.ч значений параметра х условие Ci) не должно выполняться, т.е. и х 2 должнь быть достовернрл.

Так как п о О и и п О, то условие достоверности для первого значения х l3 , принимающе-е вид - о -О, не может быть выполнено положительное число не может быть меньше либо равно нулю).

Для обеспечения достоверности значения необходимо сделать до- . статочно малым числом, например 10, а константу Jj p.LOj очень бо.т ычим числом, например 10.

Так как m l (в чем можно убедиться, подставив в формулы (6) и (,7) k 1 ип 0), то условие достоверности для второго значения х 2J, принимающее вид

/хН -xDlHy Dl х, выполняется для любых реальных х fzl

nu -J также при очень большом значении равном, например, 10 .

Таким образом, для обеспечения работоспособности технического решения, реализующего критерий (5) с учетом рекуррентных соотношений (6) и (7), необходимо след тощее; константы J, и fttO должны быть очень бо.чьшими положительньин числами, например 10 ; начальное значение среднего квадратического отклонения S О должно быть очень мал ым числом, например 10.

Итак, сущностью изобретения является схемная реализация критерия (5) с учетом рекуррентных формул (6) и (7) и указанных замечаний относительно значений Ja fo , Jn г и S о , обеспечивающая повышенное быстродействие устройства, так как проверке на достоверность подвергается каждое измеренное значение непосредственно после его измерения.

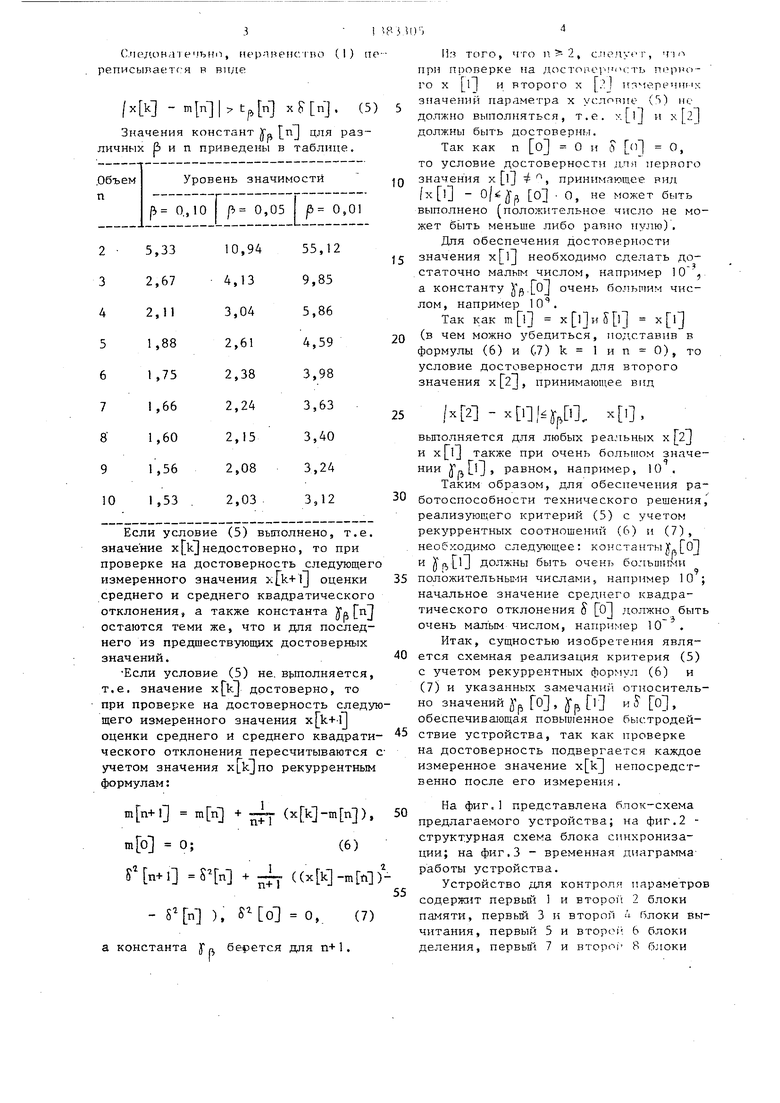

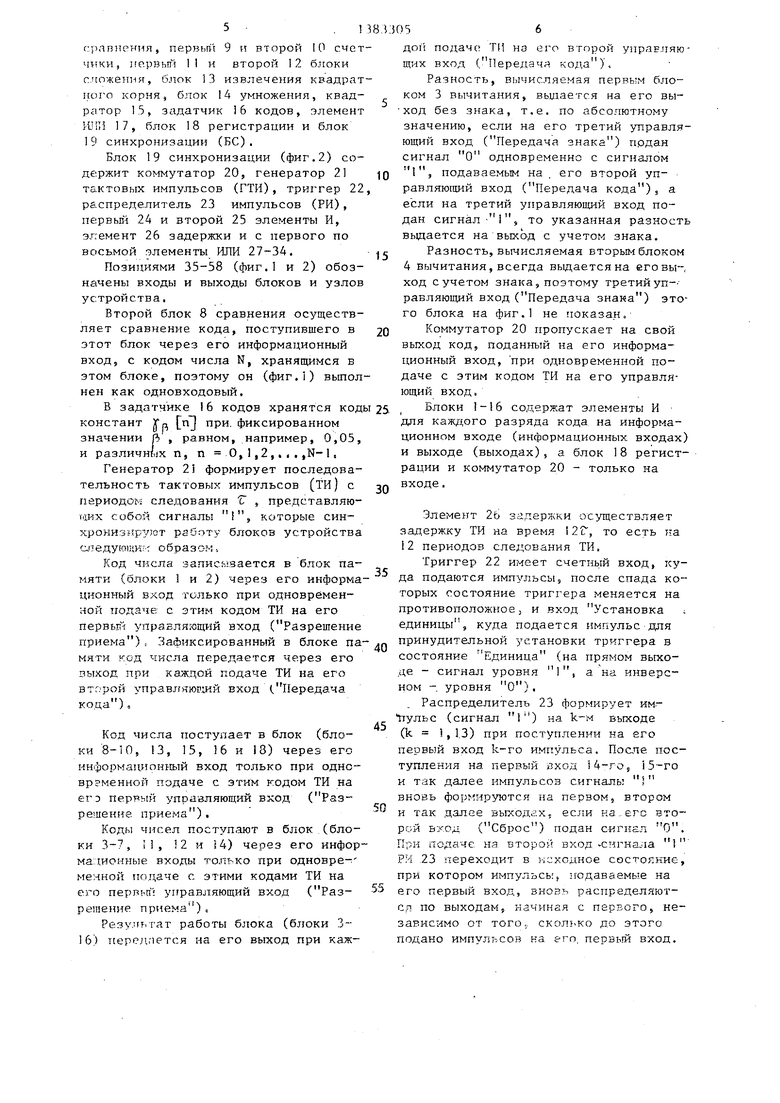

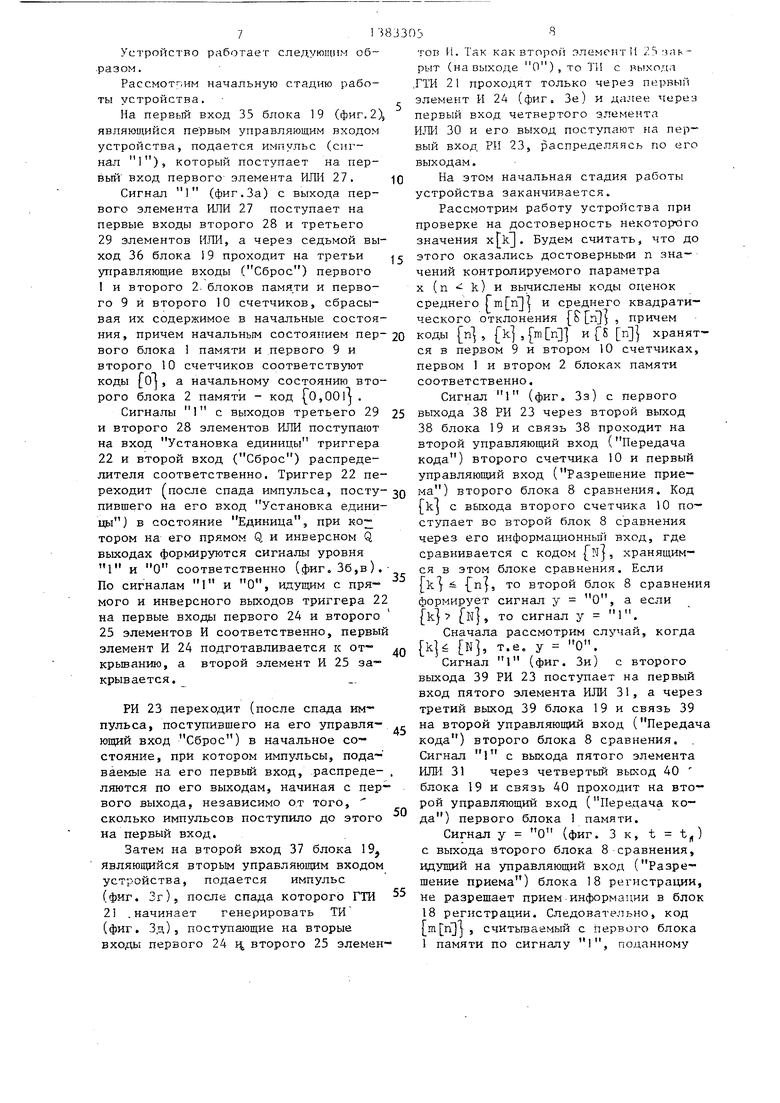

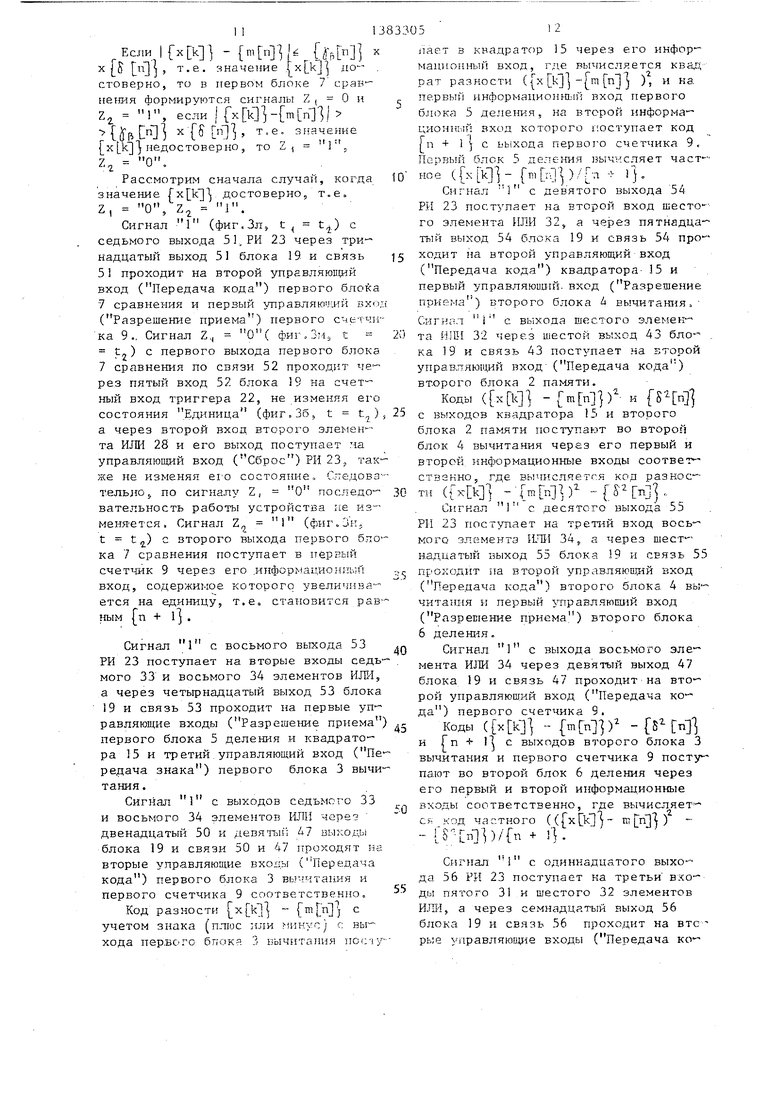

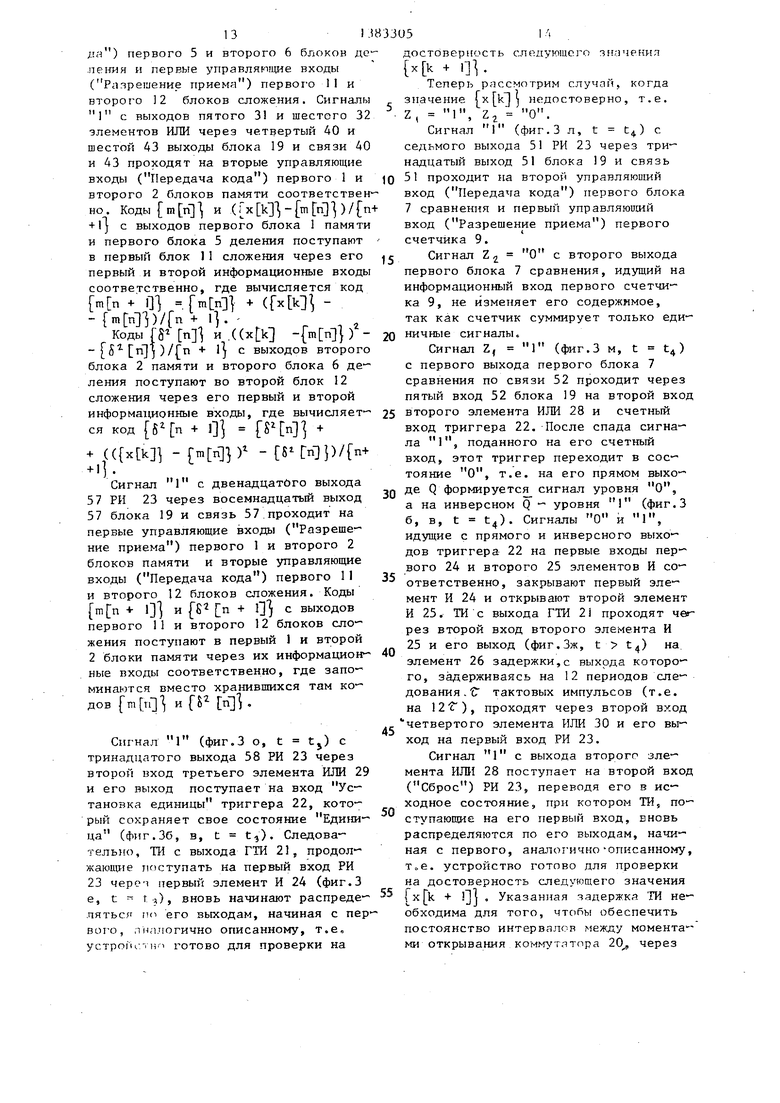

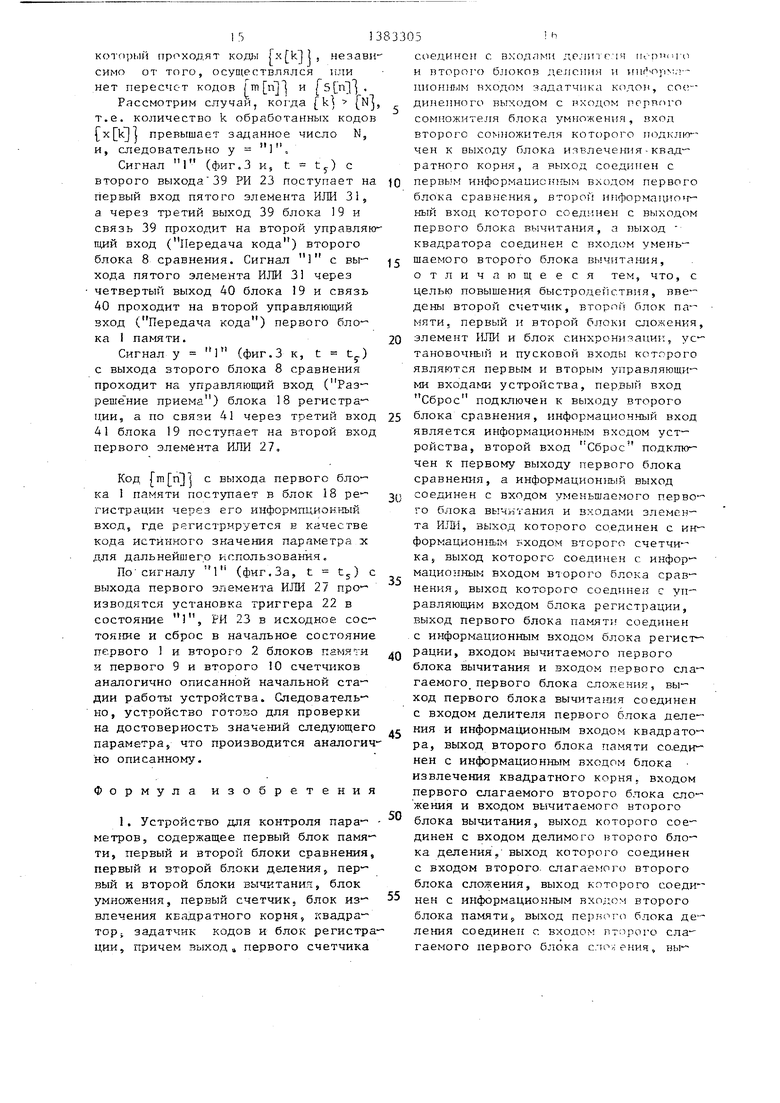

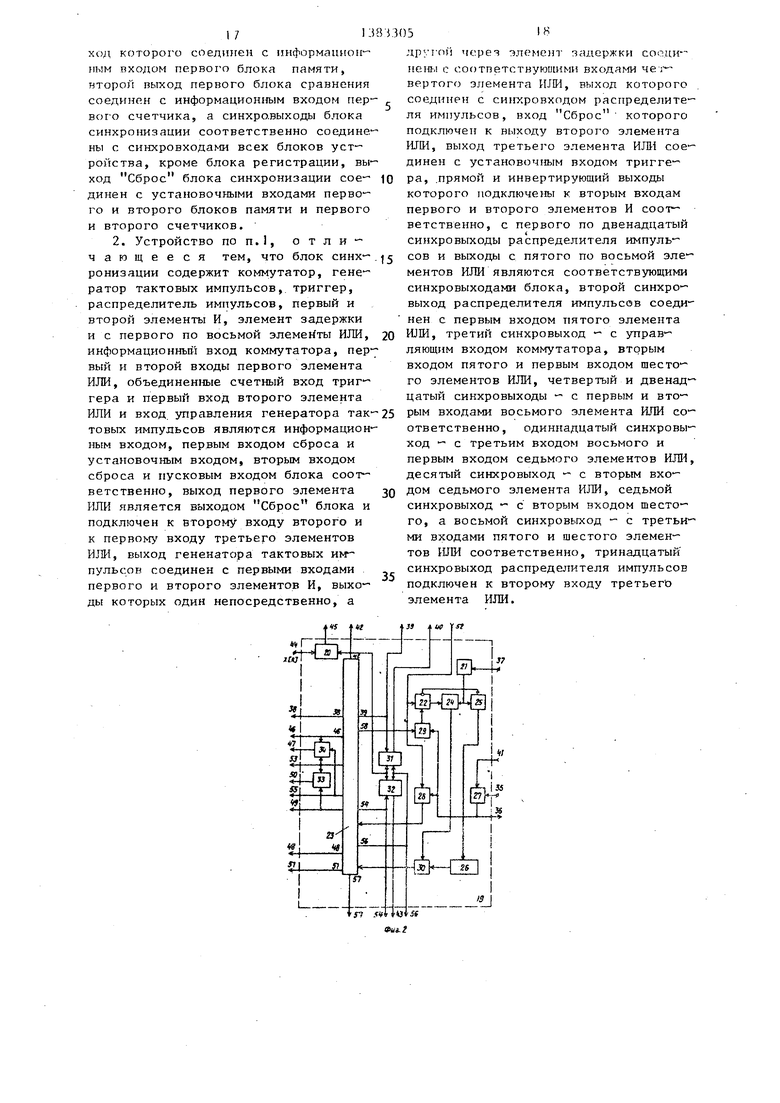

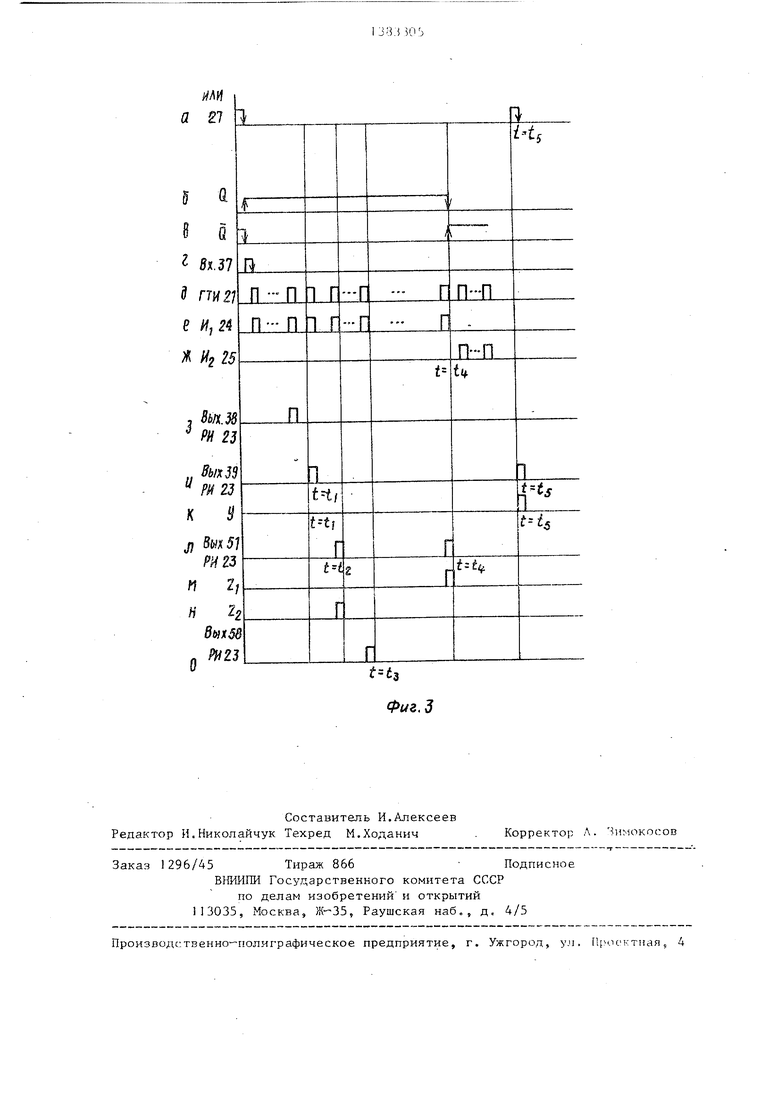

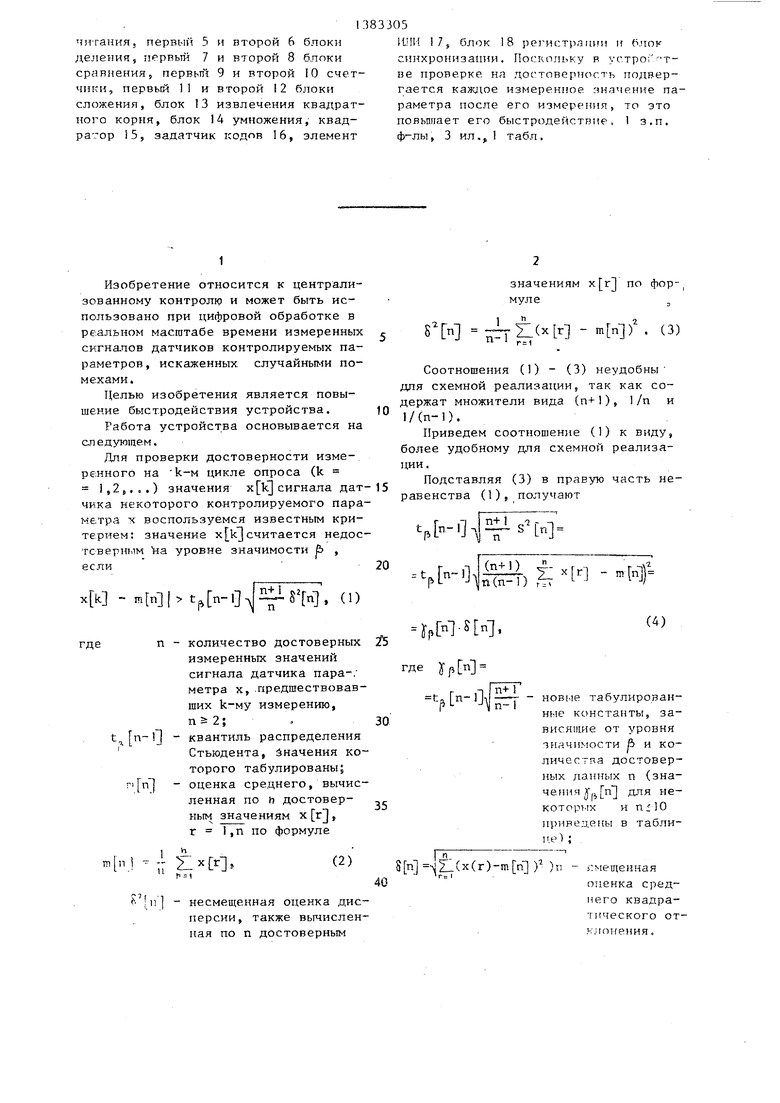

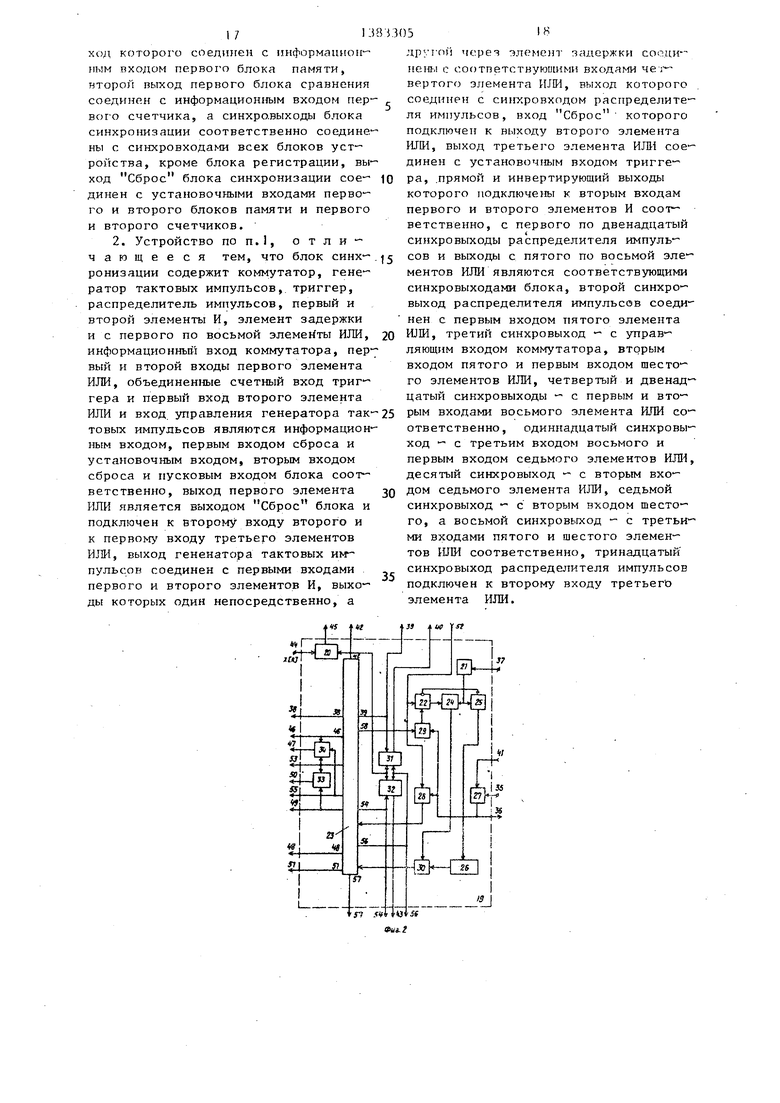

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - структурная схема блока синхронизации; на фиг.З - временная диаграмма- работы устройства.

Устройство для контроля параметров содержит первьй I и второ 2 блоки пш-1яти, первый 3 и второй Л блоки вычитания, первый 5 и второй. 6 блоки деления, первьй 7 и второг В блоки

срлпнения, nepBbrii 9 и второй 10 счет , ие.рвьй II н второй 12 блоки сложения, блок 13 извлече}1ия квадратного корня, блок 14 умножения, квадратор 15, задатчик 16 кодов, элемент l-UiIi 17, блок 18 регистрации и блок 19 синхронизации (БС).

Блок 19 синхронизации (фиг.2) содержит коммутатор 20, генератор 21 тактовых импульсов (ГТН), триггер 22 распределитель 23 импульсов (РИ), первьп 24 и второй 25 элементы И, элемент 26 задержки и с первого по восьмой элементы ИЛИ 27-34.

Позициями 35-58 (фиг.1 и 2) обоз- н 1чены входы и выходы блоков и узлов устройства,

Второй блок 8 сравнения осуществляет сравнение кода, поступившего в этот блок через его информационный вход, с кодом числа N, хранящимся в этом блоке, поэтому он (фиг,1) выполнен как одновходовый.

Б задатчике 16 кодов хранятся код констант 1 п nj при. фиксированном значении ft , равном, например, 0,05, и различных п, п О,1,2,.,.,N-1,

Генератор 21 формирует последовательность тактовых импульсов (ТИ) с периодом следования Т , представляго- 1№х собой сигналы , которые син- хронизяругот работу блоков устройства следующк;-; образом.

Код числа запись зается в блок памяти (блоки 3 и 2) через его информа ционный вход только при одновременной подаче с этим кодом ТИ на его первьш управляющий вход (Разрешение приема), Зафиксированный в блоке па мяти код числа передается через его зыход при каждой подаче ТИ на его второй управляюр кй вход (Передача кода),

Код числа поступает в блок (блоки 8-10, 13, 15, }6 и 18) через его информационный вход только при одно- вр менной подаче с этим кодом ТИ на егэ первый управляющий вход (Разрешение приема),

Коды Ч1тсел поступают в блок, (блоки 3-7, И, 12 и 4) через его информационные входы только при одновре- менной подаче с этими кодами ТИ на его первьп управляющий вход (Раз- решение приема).

Резул.гат работы блока (блоки 3- 16) 1 ередпется на его выход при каж

Q

0

5

Q

п

5

0

5

J056

до11 подаче ТИ но его второй управляющих вход (Передача кода).

Разность, вычисляемая первь;м блоком 3 вычитания, выдается на его вы- ход без знака, т.е. по абсолютному значению, если на его третий управляющий вход (Передача знака) прдан сигнал О одновременно с сигналом t, подаваемым на, его второй управляющий вход (Передача кода), а если на третий управляющий вход подан сигнал Г , то указанная разность выдается на выхЬд с учетом знака.

Разность, вычисляемая вторым блоком 4 вычитания,всегда вьщаетсяна его выход с учетом знака, поэтому третий уп--- равляющий вход (Передача знака) этого блока на фиг.1 не показан.

Коммутатор 20 пропускает на свой выход код, поданный на его информационный вход, при одновременной подаче с этим кодом ТИ на его управляющий вход.

Блоки 1-16 содержат элементы И дпя каждого разряда кода на информационном входе (информационных входах) и выходе (выходах), а блок 18 регистрации и коммутатор 20 - только на входе.

Элемент 2о задержки осуществляет задержку ТИ на время 12Г, то есть т;а 12 периодов следования ТИ,

Триггер) 22 имеет счетный вход, куда подаются импульсыэ после спада которых состояние триггера меняется на противоположное, и вход Установка ; единицы , куда подается импульс для принудительной установки триггера в состояние Единица (на прямом выходе - сигнал уровня 1, а на инверсном -. уровня О),

Распределитель 23 формирует им- Ттульс (сигнал 1) на k-м выходе (k , 1.3) при поступлении на его первый вход k-ro импульса. После поступления на первый вход t4-rc 5. i5-ro и так далее импульсов сигналы вновь формируются на первом, втором и так далее выходах; если нашего второй вход (Сброс) подан сигна.л О. При подаче на второй вход снгна.аа 1 РИ .23 переходит в -;скодное состояние, при котором импульсы, подаваемые на его первый вход, вновь распределяются по выходам, начиная с первого, независимо от ТОГО;, сколько до этого подано импульсов ка его. первый вход.

Устройство работает cneAvioinHNs об- .разом.

Расс.мотпим начальную стадию работы устройства.

На первый вход 35 блока 19 (фиг. 2 являющийся первым управляющим входом ycTpoiiCTBa, подается импульс (сигнал 1), который поступает на первый вход первого элемента ИЛИ 27.

Сигнал 1 (фиг.За) с выхода первого элемента ИЛИ 27 поступает на первые входы второго 28 и третьего 29 элементов ИЛИ, а через седьмой выход 36 блока 19 пр.оходит на третьи управляющие входы (Сброс) первого и второго 2. блоков памяти и первого 9 и второго 10 счетчиков, сбрасыческого отклонения

И ,

причем

вал их содержимое в начальные состояния, причем начальньгм состоянием пер-20 коды М , Г, и S п хранятся в первом 9 и втором 10 счетчиках, первом 1 и втором 2 блоках памяти соответственно,

Сигнал 1 (фиг. Зз) с 25

вого блока 1 памяти и первого 9 и второго 10 счетчиков соответствуют коды Oj, а начальному состоянию втопервого

выхода 38 РИ 23 через второй выход 38 блока 19 и связь 38 проходит на второй управляющий вход (Передача

10 и первый

,ti

рого блока 2 памяти - код ,00А .

Сигналы 1 с выходов третьего 29 и второго 28 элементов ИЛИ поступают на вход; Установка единицы триггера 22 и второй вход (Сброс) распределителя соответственно. Триггер 22 переходит (после спада импульса, посту-30 ма) второго блока 8 сравнения. Код пившего на его вход Установка едини- Щз1) в состояние Единица, при ко тором на его прямом Q и инверсном Q выходах формируются сигналы уровня 1 и О соответственно (фиг.3б,в). По сигналам 1 и О

второго счетчика управляющий вход (Разрешение приеl k с выхода второго счетчика 10 поступает во второй блок 8 сравнения через его информацнонньп вход, где сравнивается с кодом fN, хранящимся в этом блоке сравнения,

сигналам I и U, идущим с прямого и инверсного выходов триггера 22 на первые входы первого 24 и второго 25 элементов И соответственно, первый элемент И 24 подготавливается к от крьшанию, а второй элемент И 25 закрывается.

РИ 23 переходит (после спада импульса, поступившего на его управляющий вход Сброс) в начальное состояние, при котором импульсы, подаваемые на его первый вход, распределяются по его выходам, начиная с первого выхода, независимо от того, сколько импульсов поступило до этого на первый вход.

Затем на второй вход 37 блока 19 являющийся вторым управляющим входом устройства, подается импульс (фиг. Зг), после спада которого ГТИ 2i .начинает генерировать ТИ (фиг. Зд), поступающие на вторые входы первого 24 i второго 25 элемен-

k Гг, то второй блок о формирует сигнал у О, а

40

45

50

Если

сравнения если k N, то сигнал у 1.

Сначала рассмотрим случай, когда N, т.е. у О.

Сигнал 1 (фиг. Зи) с второго выхода 39 РИ 23 поступает на первый вход пятого элемента ИЛИ 31, а через третий вькод 39 блока 19 и связь 39 на второй управляющий вход (Передача кода) второго блока 8 сравнения. Сигнал 1 с выхода пятого элемента ИЛИ 31 через четвертый вькод 40 блока 19 и связь 40 проходит на второй управляющий вход (Передача кода) первого блока 1 памяти.

Сигнал у О (фиг. 3

t tj

55

с выхода зторого блока 8 сравнения, идущий на управляющий вход (Разрешение приема) блока 18 регистрации, не разрешает прием информации в блок 18 регистрации. Следовательно, код , считьгааемый с первого блока 1 памяти по сигналу 1, поданному

тов и. Так как BTOpofj элемент И 25:зак- рыт (на выходе О), то ТИ с выхода ,ГТИ 21 проходят только через первый элемент И 24 (фиг. Зе) и далее через первый вход четвертого элемента ИЛИ 30 и его выход поступают на первый вход РИ 23, распределяясь по его выходам.

На этом начальная стадия работы устройства заканчивается.

Рассмотрим работу устройства при проверке на достоверность некоторого значения . Будем считать, что до этого оказались достоверными п значений контролируемого параметра X (п « k) и вычислены коды оценок среднего и среднего квадратического отклонения

И ,

причем

коды М , Г, и S п хранятся в первом 9 и втором 10 счетчиках, первом 1 и втором 2 блоках памяти соответственно,

Сигнал 1 (фиг. Зз) с

первого

выхода 38 РИ 23 через второй выход 38 блока 19 и связь 38 проходит на второй управляющий вход (Передача

10 и первый

,ti

ма) второго блока 8 сравнения. Код

второго счетчика управляющий вход (Разрешение прие0 ма) второго блока 8 сравнения. Код

с выхода второго счетчика 10 поступает во второй блок 8 сравнения через его информацнонньп вход, где сравнивается с кодом fN, хранящимся в этом блоке сравнения,

k Гг, то второй блок о формирует сигнал у О, а

0

5

0

Если

сравнения если k N, то сигнал у 1.

Сначала рассмотрим случай, когда N, т.е. у О.

Сигнал 1 (фиг. Зи) с второго выхода 39 РИ 23 поступает на первый вход пятого элемента ИЛИ 31, а через третий вькод 39 блока 19 и связь 39 на второй управляющий вход (Передача кода) второго блока 8 сравнения. Сигнал 1 с выхода пятого элемента ИЛИ 31 через четвертый вькод 40 блока 19 и связь 40 проходит на второй управляющий вход (Передача кода) первого блока 1 памяти.

Сигнал у О (фиг. 3

t tj

с выхода зторого блока 8 сравнения, идущий на управляющий вход (Разрешение приема) блока 18 регистрации, не разрешает прием информации в блок 18 регистрации. Следовательно, код , считьгааемый с первого блока 1 памяти по сигналу 1, поданному

на его второй управляюпщй вход (Передача кода), в блок 18 регистрации на его второй управляющий вход (ПеКод rS вь1хода второго ка 2 памяти поступает в блок 13 влечещ-1я квадратного где в

редача кода), в блок 18 регистрации t числяется код 1 S И) fS l

.. «е.

не проходит. По сигналу у О, иду щему также по связи 4 через третий вход 41 блока 19 на второй вход первого элемента ИЛИ. 27 и далее по соот

Сигнал 1 с четвертого выхода РИ 23 поступает на первый вход во мого элемента ИЛ1 34, а через вос мой выход 46 блока 19 и связь 46

ветствующим цепям, состояние .триггера 10 ходит на первый управлятпщй вход 22 не изменяется, РИ 23 не переходит (Разрешение приема) задатчика 16 в исходное состояние, а блоки 1 и 2 памяти и счетчики 9 и 10 не сбрасывакодов. Сигнал 1 с выхода восьмог элемента ИЛИ 34 БС через девятый вы ход 47 блока 9 и связь 47 проходи

ются в начальные состояния, т.е. по

кодов. Сигнал 1 с выхода восьмого элемента ИЛИ 34 БС через девятый выход 47 блока 9 и связь 47 проходит

сл едовательность работы устройства в 15 на второй управляющий вход (Переда-

20

25

30

случае {k - «s изменяется.

Сигнал 1 с третьего выхода 42 РИ 23 проходит на управляющий вход коммутатора 20, открьшая его, и на первый и второй входы шестого 32 и пятого 31 элементов ИЛИ соответственно, а через пятый выход 42 блока 19 . и связь 42 проходит на первые управ- лянлдие входы (Разрешение приема) первого блока 3 вычитания, второго счетчика 10 и блока 13 извдечения квадратного корня.

Сигналы 1 с выходов пятого 31 и шестого 32 элементов ИЛИ через вефтый 40 и шестой 43 выходы проходят по связям 40 и 43 на вторые управляющие входы (Передача кода) первого и второго 2 блоков памяти соответственно.

Код проходит через четвер тый вход 44 блока 19, являющийся информационным входом устройства,, информационньй вход коммутатора 20, его выход и первый выход 45 блока 19 и поступает по связи 45 на эле мент ИЛИ 7 и первый информационный вход первого блока 3 вычитания, на второй информационный вход которого поступает код с выхода первого блока 1 памяти г Первьй блок 3 вычи

тания вычисляет код разности fxTkl - г г -ilL 1- J-

рМ}.

Код поступает на элемент ИЛИ 17, имеющий г входов (по количеству разрядов .входного кода). Поэтому при налич ш 1 .хотя бы в одном разряде входного кода, на вьйсоде этого элемента ИЛИ всегда имеется сиг- . I, поступающий во второй счёт- 5 чн к 10 через его информационный вход, содержимое которого увеличивается на единицу и становится равным {k + l.

35

40

45

50

ча кода) первого счетчика 9, с выхо- да которого код поступает в. за- датчик 16 кодов через его информационный вход, где по значению выбирается значение { « I

Сигнал 1 с пятого выхода 48 РИ 23 через десятый выход 48 блока 19 и связь 48 проходит на первый управляющий вход (Разрешение приема ) блока 14 умножения и вторые управляющие входы (Передача кода) задатчика 16 кодов и блока 13 извлечения квадратного корня. Коды рИ и п с выходов задатчика 16 кодов и блока 13 извлечения квадратного корня поступают в блок 14 умножения через его первый и второй информационные входы, где вычисляется произведение f М W Сигнал 1 с шестого выхода 49 .РИ 23 поступает на первый вход седьмого элемента ИЛИ 33, а через один-- надцатьй выход 49 блока 19 и связь

49проходит на второй управляющий вход (Передача кода) блока 14 умножения и первый управляюидай вход (Разреше-ние приема) первого блока 7 сравнения. Сигнал 1 с выхода седьмого элемента ШЖ 33 через двенадцатый выход 50 б.пока 19 и связь

50проходит на второй управляющий вход, (Передача кода) первого блока 3 вычитания.

Код f К пЗ и коа абсолютного значения разности (без знака) И.Й выходов блока 14 умножения и первого блока 3 вычитания поступшот в первый блок 7 сравнения через его первый и второй информационные входы соответстБанно, где осуществляется сравнение кодов,. поступивших в этот блок.

383305 0

Код rS вь1хода второго блока 2 памяти поступает в блок 13 i3- влечещ-1я квадратного где вычисляется код 1 S И) fS l

«е.

Сигнал 1 с четвертого выхода 46 РИ 23 поступает на первый вход восьмого элемента ИЛ1 34, а через восьмой выход 46 блока 19 и связь 46 про ходит на первый управлятпщй вход (Разрешение приема) задатчика 16

кодов. Сигнал 1 с выхода восьмого элемента ИЛИ 34 БС через девятый выход 47 блока 9 и связь 47 проходит

0

5

0

5

5

0

5

0

ча кода) первого счетчика 9, с выхо- да которого код поступает в. за- датчик 16 кодов через его информационный вход, где по значению выбирается значение { « I

Сигнал 1 с пятого выхода 48 РИ 23 через десятый выход 48 блока 19 и связь 48 проходит на первый управляющий вход (Разрешение приема ) блока 14 умножения и вторые управляющие входы (Передача кода) задатчика 16 кодов и блока 13 извлечения квадратного корня. Коды рИ и п с выходов задатчика 16 кодов и блока 13 извлечения квадратного корня поступают в блок 14 умножения через его первый и второй информационные входы, где вычисляется произведение f М W Сигнал 1 с шестого выхода 49 .РИ 23 поступает на первый вход седьмого элемента ИЛИ 33, а через один-- надцатьй выход 49 блока 19 и связь

49проходит на второй управляющий вход (Передача кода) блока 14 умножения и первый управляюидай вход (Разреше-ние приема) первого блока 7 сравнения. Сигнал 1 с выхода седьмого элемента ШЖ 33 через двенадцатый выход 50 б.пока 19 и связь

50проходит на второй управляющий вход, (Передача кода) первого блока 3 вычитания.

Код f К пЗ и коа абсолютного значения разности (без знака) И.Й выходов блока 14 умножения и первого блока 3 вычитания поступшот в первый блок 7 сравнения через его первый и второй информационные входы соответстБанно, где осуществляется сравнение кодов,. поступивших в этот блок.

Если - -рГп x X J Т.е. значение .( до- . стоверно, то в первом блоке 7 срав нетшя формируются сигналы Z ; О и Z , если X пП , т.е. значение х недостоверно , то Z Г ,

7 - п /. - и ,

Рассмотрим сначала случай, когда значение ГхЩУ достоверно, т.е

7 t n 7 -

i- и 5 2.

Сигнал 1 (фиг.3л, с t.) с седьмого выхода 5., РИ 23 через тринадцатый выход 51 блока 19 и связь 51 проходит на второй управляюп 5Й вход (Передача кода) первого блока 7 сравнения и первыр управляюишн вхо; (Разрешение приема ) первого с аг тч - - ка 9., Сигнал Z., 0( фиг.-Зм. t tj) с первого выхода первого блока 7 сравнения по связи 52 проходит через пятый вход 52 блока 19 на счетный вход триггера 22, не изменяя его состояния Единица (, t t) а через второй вход второго элемен- та ИЛ1-1 28 и его выход поступает la управляющий вход (Сброс) РН 23., также не изменяя его состояние, С-едовз- т.ельнО;. по сигналу Z, О последовательность работы устройства не из- меняется. Сигнал Z, i (фиг.Зи,, t 12) с второго выхода первого блока 7 сравнения поступает в первый счетчик 9 через его .информациоиньи вход, содержимое которого увели знва-- ется на единицу, т.е. становится равным {п + l .

Сигнал 1 с восьмого выхода 53

РИ 23 поступает на вторые входы седь мого 33 и восьмого 34 элементов ИЛИ, а через четырнадцатый выход 53 блока 19 и связь 53 проходит на первые управляющие входы (Разрешение приема) первого блока 5 деления и квадратора 15 и третий,управляющий вход (Передача знака) первого блока 3 вычитания .

Сигнал 1 с выходов седьмг;го 33 и восьмого 34 элементов ИЛИ через двенадцатый 50 и девятыГ; 47 выходы блока 19 и связи 50 и 47 проходят на вторые управляющие входы ( Передача кода) первого блока 3 вы -ггания и первого счетчика 9 соответственно.

Код разности ,l - с учетом знака (плюс или мянус) с выхода первого бпокя 3 вычитания посчу

0

5

5

0

лает в квадратор 15 через его инфор- мадионшлй вход, где вычисляется квад par разности ( п ), и на первый информациопШ;1Й вход первого блока 5 деления, на второй информационный вход которого г оступает код Гп + 1 i с первого счетчика 9, Первый блок 5 деления вычисляет част-- нее ( тГгЛ 1 )/Г-л ,

Сигнал 1 с девятого выхода 54 РИ 23 постз пает на второй вход шесто-- го элемента ИЛИ 32, а через пятнадцатый выход 54 блока 19 и связь 54 про- ходит на второй управляющий вход (Передача кода) квадратора- 15 и первый управляюпшй. вход (Разрешение приема ) второго блока вь читания - Сигнал Г с выхода шестого элемента 32 через шестой вь:ход 43 , ка 19 и связь 43 поступает на второй управляющий вход (Передача кода) второго блока 2 памяти.

Коды ( )- и SHn с вь ходов квадратора 15 и второго блока 2 памяти поступают во второй блок 4 вычитания через его первый и второй информационные входы соответственно, где вычисляется код разнос-

ти (ГкВд -ТшНЪ

иигкал

1 с десятого выхода

0

0

5

РИ 23 поступает на третий вход вось кого элемента ILTII 34 а через надцатый выход 55 блока 19 и связь 55 пр оходпт iia второй управляющий вход (Передача кода) второго блока 4 вычитания и первый управляющий вход (Разрешение приема) второго блока 6 делеш я.

Сигнал 1 с выхода восьмого эле мента ЗА через девятьп выход 47 блока 19 и связь 47 проходит на вто- рой управляющий вход (Передача кода) первого счетчика 9.

Коды (хИ - тГп1р -fS4n l и Гп 1 с ВЫХОДОВ второго блока 3 вычитания и первого счетчика 9 посту пагот во второй блок 6 деления через его первый и второй информационные входы соответственно, где вычисляет ск код частного ((ГхВДЯ- п Гп1 ) . .

Сигнал 1 с одиннадцатого выхо-- да 56 РИ 23 поступает на третьи входы пятого 31 и шестого 32 элементов И.ПИ, а через семнадцатый выход 56 блока 19 и связь 56 проходит на втс- у-правляювц1е входы (Передача ко-

13

да) первого 5 и второго 6 блоков д .neiTHH и первые управлякидие входы (Разрешение приема) первог-о II и второго 12 блоков сложения. Сигнал 1 с выходов пятого 31 и шестого 3 элементов ИЛИ через четвертый АО и шестой 43 выходы блока 19 и связи 4 и 43 проходят на вторые управляющие входы (Передача кода) первого 1 и второго 2 блоков памяти соответствено. и ()/ +1J с выходов первого блока 1 памят и первого блока 5 деления поступают в первый блок 1 1 сложения через его первый и второй информационные вход соответственно, где вычисляется код 4- 0 .тИ + ( -f ) + l .

Коды S n и .((xtk ) ri J )/Гп -I- 1 с выходов второг блока 2 памяти и второго блока 6 де ления поступают во второй блок 12 сложения через его первый и второй информационные входы, где вычисляет ся код -1- 1 +

+ (( ) + l.

Сигнал 1 с двенадцатого выхода 57 РИ 23 через восемнадцатый выход 57 блока 19 и связь 57.проходит на первые управляющие входы (Разреше ние приема) первого 1 и второго 2 блоков памяти и вторые управляющие входы (Передача кода) первого 11 и второго 12 блоков сложения. Коды + 1 и Б п + 1 с выходов первого 11 и второго 12 блоков сло женин поступают в первый 1 и второй 2 блоки памяти через их информацион ные входы соответственно, где запо- минаьзтся вместо хранившихся там кодов тИ и 8 и ,

Сигнал 1 (фиг.З о, t tj) с тринадцатого выхода 58 РИ 23 через второй вход третьего элемента ИЛИ 29 и его выход поступает на вход Установка единицы триггера 22, который сохраняет свое состояние Едини

ца (фиг.Зб,

С t). Следователь}), ТИ с выхода ГТИ 21, продолжающие поступать на первый вход РИ 23 черо 1 первый элемент И 24 (фиг.З е, t - t 3), вновь начинают распреде литься его выходам, начиная с пер вог о, пиа.иогично описанному, т.е, устроГи .тн готово для проверки на

достоверкость слелуюшс.го ЗИЯЧРНИЯ -f I-.

Теперь рассмотрим случай, когда значение fх k недостоверно, т.е. Z, 1, Z О.

Сигнал 1 (фиг.З л, t t.) с седьмого выхода 51 РИ 23 через тринадцатый выход 51 блока 19 и связь 51 проходит на второй управляющий вход (Передача кода) первого блока 7 сравнения и первый управляюидай вход (Разрешение приема) первого счетчика 9.

Сигнал Z,

О с второго выхода

первого блока 7 сравнения, идущий на информационный вход первого счетчика 9, не изменяет его содержимое, так как счетчик суммирует только еди

ничные сигналы.

и 1 tt

Сигнал Z, 1 (фиг.З м, t t) с первого выхода первого блока 7 сравнения по связи 52 проходит через пятый вход 52 блока 19 на второй вход

второго элемента ИЛИ 28 и счетный вход триггера 22. После спада сигнала 1, поданного на его счетный вход, этот триггер переходит в состояние О, т.е. на его прямом выхое Q формируется сигнал уровня О, а на инверсном Q - уровня 1 (фиг.З

35

40

45

50

55

б, в, t t). Сигналы О и 1, идущие с прямого и инверсного выходов триггера 22 на первые входы первого 24 и второго 25 элементов И соответственно, закрывают первый элемент И 24 и открывают второй элемент И 25. ТИ с выхода ГТИ 21 проходят чет- рез второй вход второго элемента И 25 и его выход (фиг.Зж, t t) на элемент 26 задержки,с выхода которого, задерживаясь на 12 периодов следования. С тактовых импульсов (т.е. на ), проходят через второй вход четвертого элемента ИЛИ 30 и его выход на первый вход РИ 23.

Сигнал 1 с выхода второго элемента ИЛИ 28 поступает на второй вход (Сброс) РИ 23, переводя его в исходное состояние, при котором ТИ, по- ступаюпще на его первый вход, вновь распределяются по его выходам, начиная с первого, аналогично Описанному, . устройство готово для проверки на достоверность следующего значения + ij , Указанная задержка ГИ необходима для того, чтобы обеспечить постоянство интервалов между моментами открывания коммутатора 20, через

который троходят коды , симо от того, осуп(ествлялся

незавиилш

нет пересчет кодов и .

Рассмотрим случаи, ког да k f т.е. количество k обработанных кодов превышает заданное число N, и, следовательно у 1,

Сигнал 1 (фиг.З и, г. t) с второго выхода 39 РИ 23 поступает на первый вход пятого элемента ИЛИ 31, а через третий выход 39 блока 19 и связь 39 проходит на второй управляро щий вход (Передача кода) второго блока 8 сравнения. Сигнал 1 с вы- хода пятого элемента ИЛИ 31 через четвертый выход 40 блока 19 и связь

40проходит на второй управляющий вход (Передача кода) первого бло

ка 1 памяти.

Сигнал у 1 (фиг.З к, t t.) с выхода второго блока 8 сравнения проходит на управляющий вход (Раз- реше ние приема) блока 18 регистра ции, а по связи 41 через третий вход

41блока 19 поступает на второй вход первого элемента ИЛИ 27,

Код с выхода первого бло ка I памяти поступает в блок 18 ре гистрации через его информпциоккый вход, где регистрируется в качестве кода истинного значения параметра х для дальнейшего использования.

По сигналу 1 (фиг,За, t t) с выхода первого элемента ИЛИ 27 производятся установка триггера 22 в состояние , РИ 23 в исходное сос и сброс в начальное состояние первого 1 и второго 2 блоков памяти и первого 9 и второго 0 счетчиков аналогично описанной начальной ста дин работы устройства. Следователь но, устройство готово для проверки на достоверность значений следующего параметраS что производится аналогич но описанному.

Формула изобретения

Q

0

5

5

5

0

5

0

соединен с ВХОДПМИ ДРЛИТГ- Ч ГК- П ЧЧ1

и BTOpoi o 6JJOKOB л,елс1шя н Hiu -oyiN:, -- входом зпдатчика к одо}), сосг- динепного выходом с нхоцом герппго сомножителя блока умножения, вход второго сомножителя которого подклю чей к выходу блока иявлеченпяквадратного корня, а выход соеди1 ен с первым информа11ио1Т ;ЫМ первого блока сравнения, второй ир1формацио г- ньш вход которого соединен с выходом первого блока вычитания, а выход квадратора соединен с входом умень- щаемого второго блока вычитания, отличающееся тем, что, с целью повышения быстродействия, введены второй с етчик, второй блок памяти, первый и второй блоки сложения, элемент ИЛИ и блок синхронизаци -:, ус- тановоч№.1Й и пусковой входы которого являются первым и вторым управляющими входами устройства, первый вход Сброс подключен к выходу второго блока сравнения, информационный вход является информационным входом устройства, второй вход Сброс подключен к первому выходу первого блока сравнения, а информационный выход соединен с входом уменьшаемого первого блока вычитания и входами элемента ШН, выход которого соединен с ин- формационньгм входом второго счетчика, выход которого соединен с инфор- мацио}1ным входом второго блока сравнения, выход которого соедннен с управляющим входом блока регистрации, выход первого блока памяти соединен с информационным входом блока регистрации, входом вычитаемого первого блока вычитания и входом первого слагаемого первого блока сложения, выход первого блока вычитания соединен с входом делителя первого блока деления и информационным входом квадратора, выход второго блока памяти со.еди- иен с информационным входом блока извлечения квадратного корня, входом первого слагаемого второго блока сложения и входом вычитаемого второго блока вычитания, выход которого соединен с входом делимого второго блока деления, выход которого соединен с входом второго, cлaгae oг« второго блока сложения, выход которого соединен с информационным входом второго блока памяти, выход nepriord блока деления соединен с входом nrtiporo слагаемого первого блока с.-ю,-; ения, вы-

на

If

t--t3

Фиг.З

| Цифровой фильтр | 1976 |

|

SU577533A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для контроля параметров | 1979 |

|

SU849152A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-29—Подача