Изобретение относится к электросвязи и может использоваться для последовательного анализа сигналов декодирования.

Целью изобретения является повышение достоверности информации.

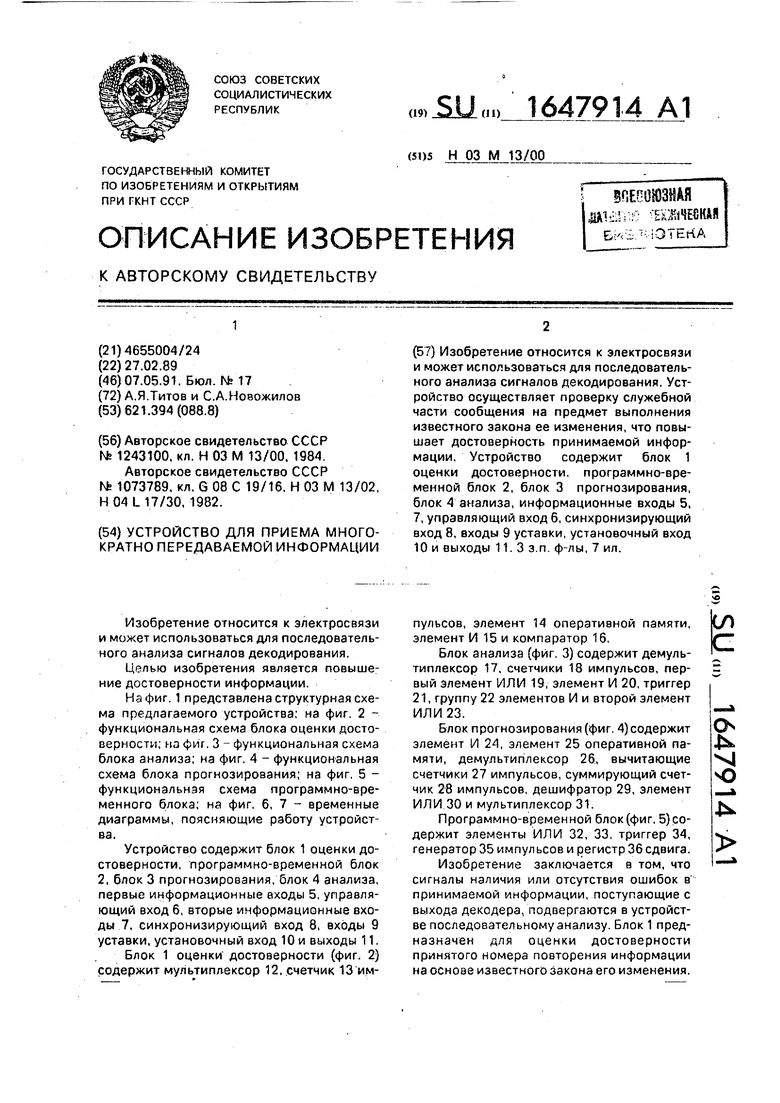

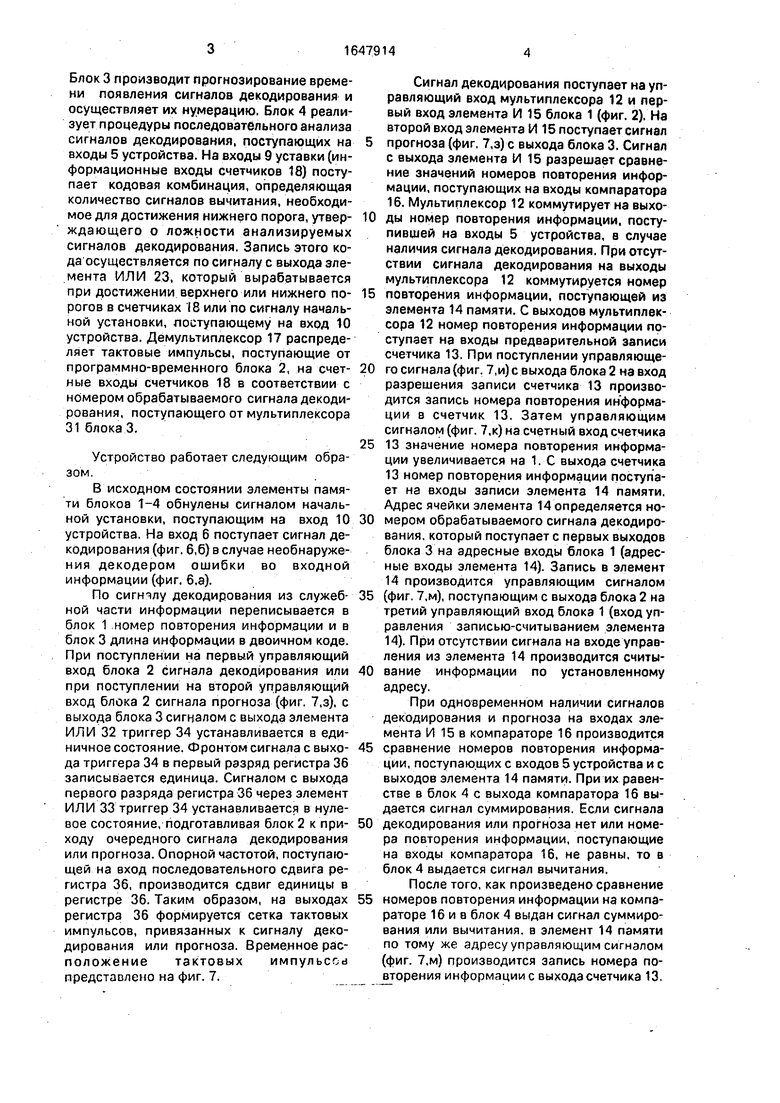

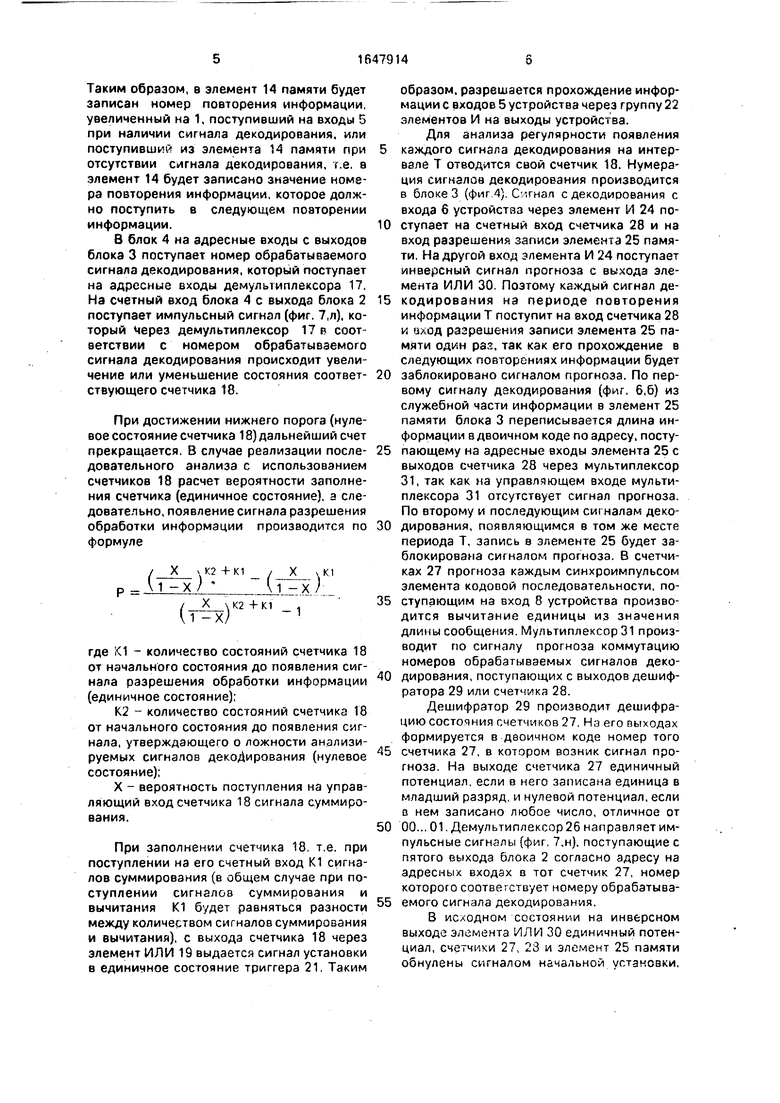

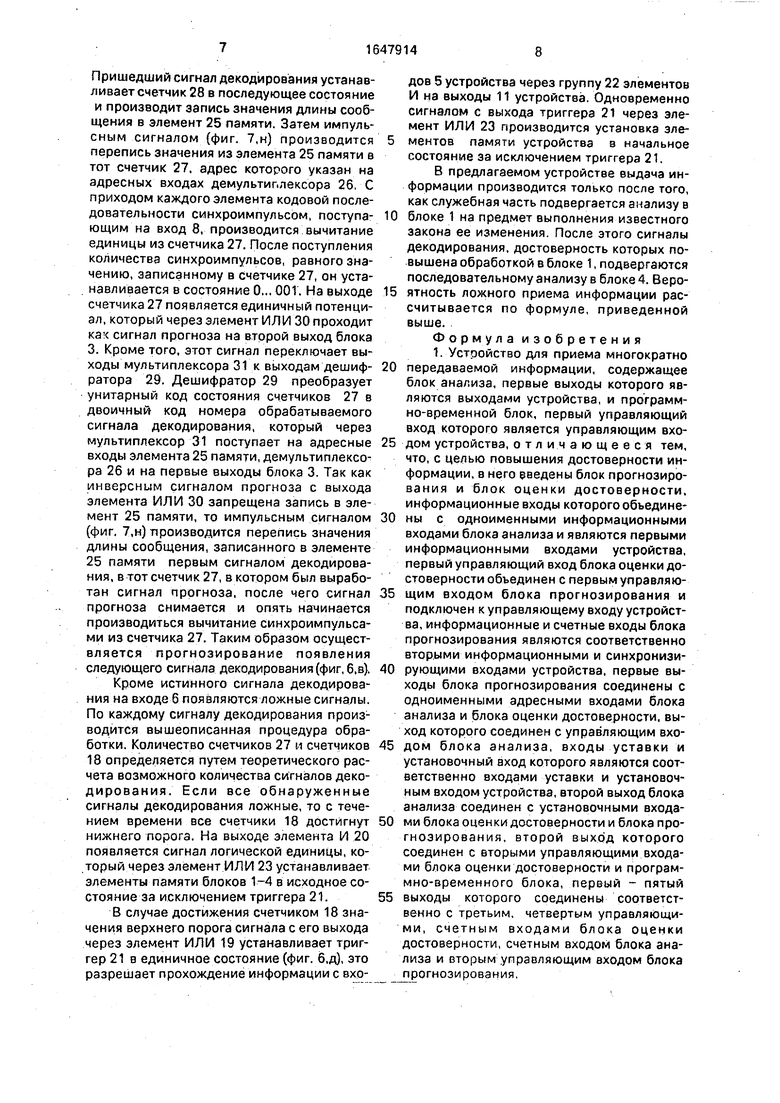

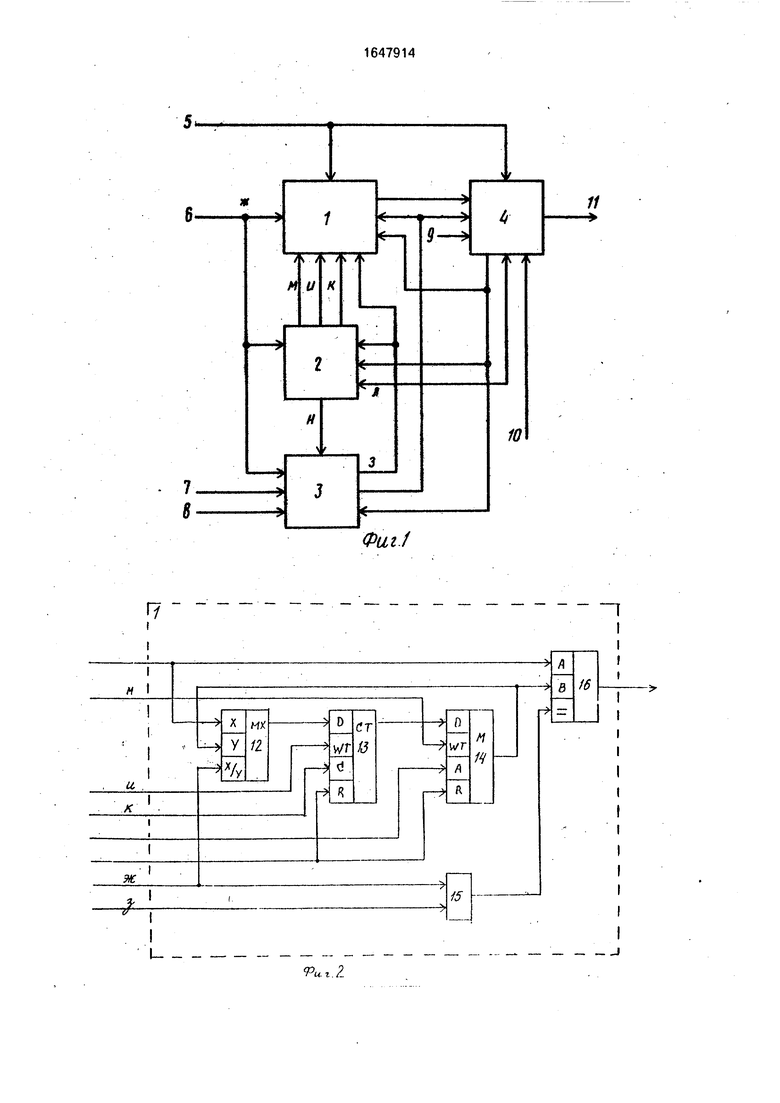

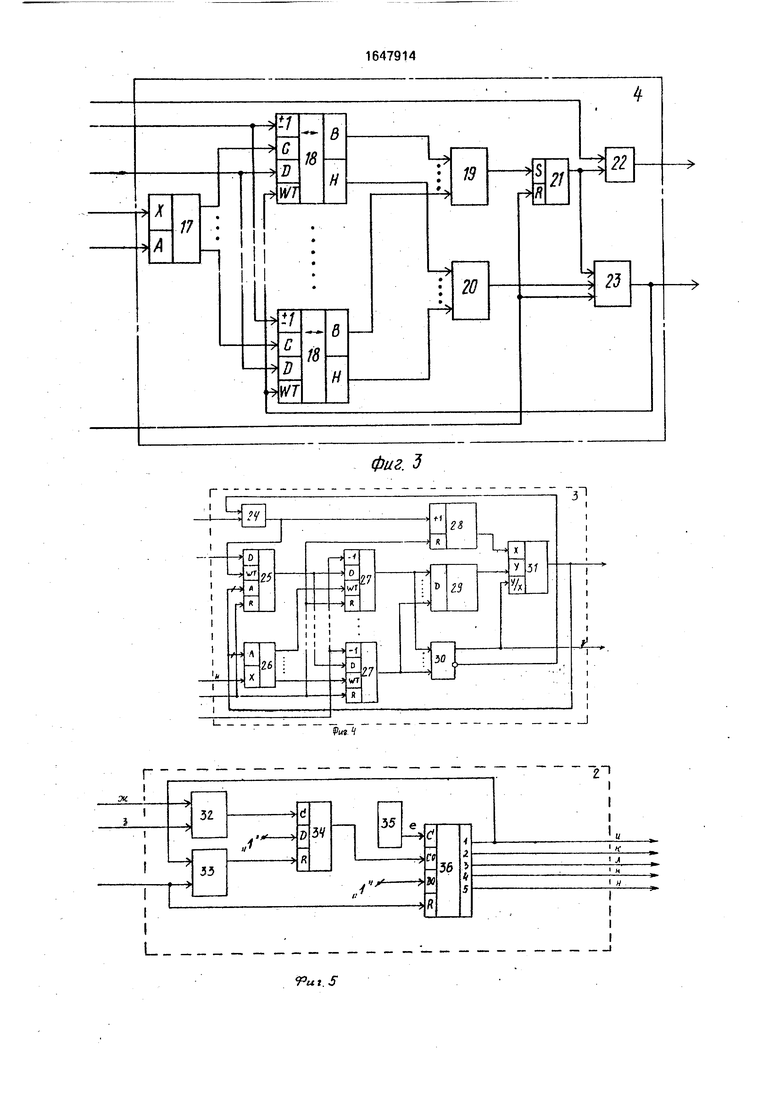

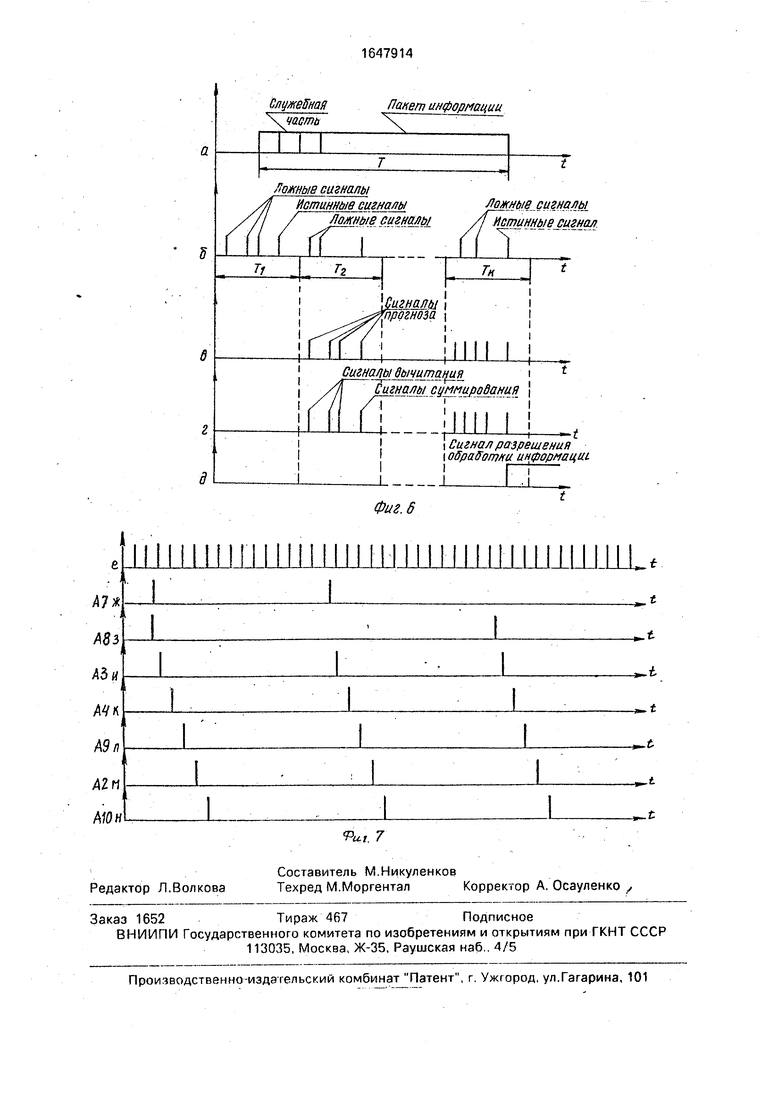

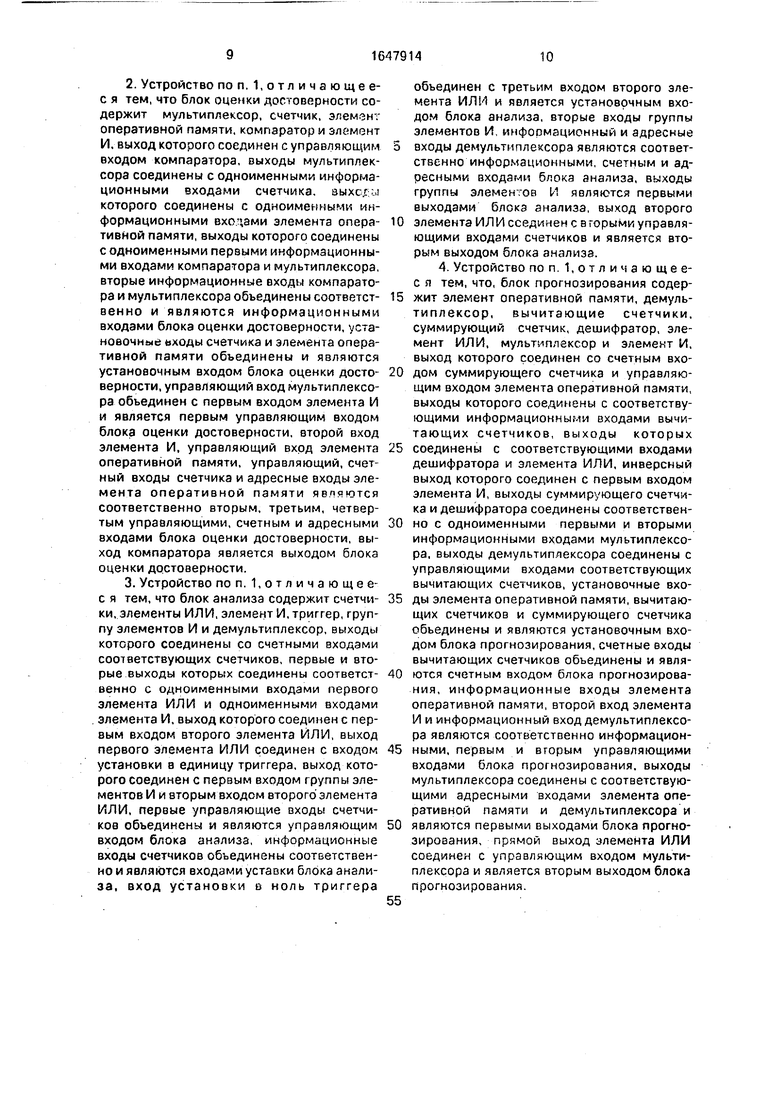

На фиг. 1 представлена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока оценки достоверности; на фиг. 3 - функциональная схема блока анализа; на фиг. 4 - функциональная схема блока прогнозирования; на фиг. 5 - функциональная схема программно-временного блока; на фиг. 6, 7 - временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 оценки достоверности, программно-временной блок 2, блок 3 прогнозирования, блок 4 анализа, первые информационные входы 5, управляющий вход 6, вторые информационные входы 7, синхронизирующий вход 8, входы 9 уставки, установочный вход 10 и выходы 11.

Блок 1 оценки достоверности (фиг. 2) содержит мультиплексор 12. счетчик 13 импульсов, элемент 14 оперативной памяти, элемент И 15 и компаратор 16.

Блок анализа (фиг. 3) содержит демуль- типлексор 17, счетчики 18 импульсов, первый элемент ИЛИ 19, элемент И 20, триггер 21, группу 22 элементов И и второй элемент ИЛИ 23.

Блок прогнозирования (фиг. 4) содержит элемент И 24, элемент 25 оперативной памяти, демультиплексор 26, вычитающие счетчики 27 импульсов, суммирующий счетчик 28 импульсов, дешифратор 29, элемент ИЛИ 30 и мультиплексор 31.

Программно-временной блок (фиг. 5) содержит элементы ИЛИ 32, 33, триггер 34, генератор 35 импульсов и регистр 36 сдвига.

Изобретение заключается в том, что сигналы наличия или отсутствия ошибок в принимаемой информации, поступающие с выхода декодера, подвергаются в устройстве последовательному анализу. Блок 1 предназначен для оценки достоверности принятого номера повторения информации на основе известного закона его изменения.

(Л

С

о

XI ЧЭ

Блок 3 производит прогнозирование времени появления сигналов декодирования и осуществляет их нумерацию. Блок 4 реализует процедуры последовательного анализа сигналов декодирования, поступающих на входы 5 устройства. На входы 9 уставки (информационные входы счетчиков 18} поступает кодовая комбинация, определяющая количество сигналов вычитания, необходимое для достижения нижнего порога, утверждающего о ложности анализируемых сигналов декодирования. Запись этого кода осуществляется по сигналу с выхода элемента ИЛИ 23, который вырабатывается при достижении верхнего или нижнего порогов в счетчиках 18 или по сигналу начальной установки, поступающему на вход 10 устройства. Демультиплексор 17 распределяет тактовые импульсы, поступающие от программно-временного блока 2, на счетные входы счетчиков 18 в соответствии с номером обрабатываемого сигнала декодирования, поступающего от мультиплексора 31 блока 3.

Устройство работает следующим образом.

В исходном состоянии элементы памяти блоков t-4 обнулены сигналом начальной установки, поступающим на вход 10 устройства. На вход 6 поступает сигнал декодирования (фиг. 6,6) в случае необнаружения декодером ошибки во входной информации (фиг. 6,а).

По сигналу декодирования из служебной части информации переписывается в блок 1 номер повторения информации и в блок 3 длина информации в двоичном коде. При поступлении на первый управляющий вход блока 2 сигнала декодирования или при поступлении на второй управляющий вход блока 2 сигнала прогноза (фиг. 7,з). с выхода блока 3 сигналом с выхода элемента ИЛИ 32 триггер 34 устанавливается в единичное состояние. Фронтом сигнала с выхода триггера 34 в первый разряд регистра 36 записывается единица. Сигналом с выхода первого разряда регистра 36 через элемент ИЛИ 33 триггер 34 устанавливается в нулевое состояние, подготавливая блок 2 к приходу очередного сигнала декодирования или прогноза. Опорной частотой, поступающей на вход последовательного сдвига регистра 36, производится сдвиг единицы в регистре 36. Таким образом, на выходах регистра 36 формируется сетка тактовых импульсов, привязанных к сигналу декодирования или прогноза. Временное расположение тактовых импульсов представлено на фиг. 7.

Сигнал декодирования поступает на управляющий вход мультиплексора 12 и первый вход элемента И 15 блока 1 (фиг. 2). На второй вход элемента И 15 поступает сигнал

прогноза (фиг. 7,з) с выхода блока 3. Сигнал с выхода элемента И 15 разрешает сравнение значений номеров повторения информации, поступающих на входы компаратора 16. Мультиплексор 12 коммутирует на выхо0 ды номер повторения информации, поступившей на входы 5 устройства, в случае наличия сигнала декодирования. При отсутствии сигнала декодирования на выходы мультиплексора 12 коммутируется номер

5 повторения информации, поступающей из элемента 14 памяти. С выходов мультиплексора 12 номер повторения информации поступает на входы предварительной записи счетчика 13. При поступлении управяяюще0 го сигнала (фиг. 7,и) с выхода блока 2 на вход разрешения записи счетчика 13 производится запись номера повторения информации в счетчик 13. Затем управляющим сигналом (фиг. 7,к) на счетный вход счетчика

5 13 значение номера повторения информации увеличивается на 1. С выхода счетчика

13номер повторения информации поступает на входы записи элемента 14 памяти. Адрес ячейки элемента 14 определяется но0 мером обрабатываемого сигнала декодирования, который поступает с первых выходов блока 3 на адресные входы блока 1 (адресные входы элемента 14). Запись в элемент

14производится управляющим сигналом 5 (фиг. 7,м), поступающим с выхода блока 2 на

третий управляющий вход блока 1 (вход управления записью-считыванием элемента 14). При отсутствии сигнала на входе управления из элемента 14 производится считы0 вание информации по установленному адресу.

При одновременном наличии сигналов декодирования и прогноза на входах элемента И 15 в компараторе 16 производится

5 сравнение номеров повторения информации, поступающих с входов 5 устройства и с выходов элемента 14 памяти. При их равенстве в блок 4 с выхода компаратора 16 выдается сигнал суммирования. Если сигнала

0 декодирования или прогноза нет или номера повторения информации, поступающие на входы компаратора 16, не равны, то в блок 4 выдается сигнал вычитания.

После того, как произведено сравнение

5 номеров повторения информации на компараторе 16 и в блок 4 выдан сигнал суммирования или вычитания, в элемент 14 памяти по тому же адресу управляющим сигналом (фиг. 7,м) производится запись номера повторения информации с выхода счетчика 13.

Таким образом, в элемент 14 памяти будет записан номер повторения информации, увеличенный на 1, поступивший на входы 5 при наличии сигнала декодирования, или поступивший из элемента 14 памяти при отсутствии сигнала декодирования, г.е. в элемент 14 будет записано значение номера повторения информации, которое должно поступить в следующем повторении информации.

В блок 4 на адресные входы с выходов блока 3 поступает номер обрабатываемого сигнала декодирования, который поступает на адресные входы демулыиплексора 17. На счетный вход блока 4 с выхода блока 2 поступает импульсный сигнал (фиг, 7,л), который через демультиплексор 17 в соответствии с номером обрабатываемого сигнала декодирования происходит увеличение или уменьшение состояния соответствующего счетчика 18.

При достижении нижнего порога (нулевое состояние счетчика 18) дальнейший счет прекращается. В случае реализации последовательного анализа с использованием счетчиков 18 расчет вероятности заполнения счетчика (единичное состояние), а следовательно, появление сигнала разрешения обработки информации производится по формуле

/ X v K2 +К1 / X

1 -X/ )

К1

/ X К2 +К1

()

-1

где - количество состояний счетчика 18 от начального состояния до появления сигнала разрешения обработки информации (единичное состояние);

К2 - количество состояний счетчика 18 от начального состояния до появления сигнала, утверждающего о ложности анализируемых сигналов декодирования (нулевое состояние);

X - вероятность поступления на управляющий вход счетчика 18 сигнала суммирования.

При заполнении счетчика 18, т.е. при поступлении на его счетный вход К1 сигналов суммирования (в общем случае при поступлении сигналов суммирования и вычитания К1 будет равняться разности между количеством сигналов суммирования и вычитания), с выхода счетчика 18 через элемент ИЛИ 19 выдается сигнал установки в единичное состояние триггера 21. Таким

образом, разрешается прохождение информации с входов 5 устройства через группу 22 элементов И на выходы устройства.

Для анализа регулярности появления

каждого сигнала декодирования на интервале Т отводится свой счетчик 18. Нумерация сигналов декодирования производится в блоке 3 (фиг 4). О.гнал с декодирования с входа 6 устройства через элемент И 24 поступает на счетный вход счетчика 28 и на вход разрешения записи элемента 25 памяти. На другой вход элемента И 24 поступает инверсный сигнал прогноза с выхода элемента ИЛИ 30. Поэтому каждый сигнал декодирования на периоде повторения информации Т поступит на вход счетчика 28 и ЦАОД разрешения записи элемента 25 памяти одкн раз, так как его прохождение в следующих повторениях информации будет

заблокировано сигналом прогноза. По первому сигналу декодирования (фиг. 6,6) из служебной части информации в элемент 25 памяти блока 3 переписывается длина информации в двоичном коде по адресу, постулающему на адресные входы элемента 25 с выходов счетчика 28 через мультиплексор 31, так как на управляющем входе мультиплексора 31 отсутствует сигнал прогноза. По второму и последующим CHI налам декодирования, появляющимся в том же месте периода Т, запись в элементе 25 будет заблокирована сигналом прогноза. В счетчиках 27 прогноза каждым синхроимпульсом элемента кодовой последовательности, поступающим на вход 8 устройства производится вычитание единицы из значения длины сообщения. Мультиплексор 31 производит по сигналу прогноза коммутацию номеров обрабатываемых сигналов декодирования, поступающих с выходов дешифратора 29 или счетчика 28.

Дешифратор 29 производит дешифрацию состояния счетчиков 27. На его выходах формируется в двоичном коде номер того

счетчика 27, в котором возник сигнал прогноза. На выходе счетчика 27 единичный потенциал, если в него записана единица в младший разряд, и нулевой потенциал, если о нем записано любое число, отличное от

00... 01. Демультиплексор 26 направляет импульсные сигналы (фиг. 7,н), поступающие с пятого выхода блока 2 согласно адресу на адресных входах в тот счетчик 27, номер которого соответствует номеру обрабатываемого сигнала декодирования.

В исходном состоянии на инверсном выходе элемента ИЛИ 30 единичный потенциал, счетчичи 27, 23 и элемент 25 памяти обнулены сигналом начальной установки.

Пришедший сигнал декодирования устанавливает счетчик 28 в последующее состояние и производит запись значения длины сообщения в элемент 25 памяти. Затем импульсным сигналом (фиг. 7,н) производится перепись значения из элемента 25 памяти в тот счетчик 27. адрес которого указан на адресных входах демультиплексора 26, С приходом каждого элемента кодовой последовательности синхроимпульсом, поступающим на вход 8, производится вычитание единицы из счетчика 27. После поступления количества синхроимпульсов, равного значению, записанному в счетчике 27, он устанавливается в состояние 0... 001. На выходе счетчика 27 появляется единичный потенциал, который через элемент ИЛИ 30 проходит как сигнал прогноза на второй выход блока 3. Кроме того, этот сигнал переключает выходы мультиплексора 31 к выходам дешифратора 29. Дешифратор 29 преобразует унитарный код состояния счетчиков 27 в двоичный код номера обрабатываемого сигнала декодирования, который через мультиплексор 31 поступает на адресные входы элемента 25 памяти, демультиплексора 26 и на первые выходы блока 3. Так как инверсным сигналом прогноза с выхода элемента ИЛИ 30 запрещена запись в элемент 25 памяти, то импульсным сигналом (фиг. 7,н) лроизводится перепись значения длины сообщения, записанного в элементе 25 памяти первым сигналом декодирования, в тот счетчик 27, в котором был выработан сигнал прогноза, после чего сигнал прогноза снимается и опять начинается производиться вычитание синхроимпульсами из счетчика 27. Таким образом осуществляется прогнозирование появления следующего сигнала декодирования (фиг, 6,в).

Кроме истинного сигнала декодирования на входе 6 появляются ложные сигналы. По каждому сигналу декодирования производится вышеописанная процедура обработки. Количество счетчиков 27 и счетчиков 18 определяется путем теоретического расчета возможного количества сигналов декодирования. Если все обнаруженные сигналы декодирования ложные, то с течением времени все счетчики 18 достигнут нижнего порога. На выходе элемента И 20 появляется сигнал логической единицы, который через элемент ИЛИ 23 устанавливает элементы памяти блоков 1-4 в исходное состояние за исключением триггера 21.

В случае достижения счетчиком 18 значения верхнего порога сигнала с его выхода через элемент ИЛИ 19 устанавливает триггер 21 в единичное состояние (фиг. 6,д), это разрешает прохождение информации с входов 5 устройства через группу 22 элементов И на выходы 11 устройства. Одновременно сигналом с выхода триггера 21 через элемент ИЛИ 23 производится установка элементов памяти устройства в начальное состояние за исключением триггера 21.

В предлагаемом устройстве выдача информации производится только после того, как служебная часть подвергается анализу в

0 блоке 1 на предмет выполнения известного закона ее изменения. После этого сигналы декодирования, достоверность которых повышена обработкой в блоке 1, подвергаются последовательному анализу в блоке 4. Веро5 ятность ложного приема информации рассчитывается по формуле, приведенной выше.

Формула изобретения

1. Устройство для приема многократно

0 передаваемой информации, содержащее блок анализа, первые выходы которого являются выходами устройства, и программно-временной блок, первый управляющий вход которого является управляющим вхо5 дом устройства, отличающееся тем, что, с целью повышения достоверности информации, в него введены блок прогнозиро- вания и блок оценки достоверности, информационные входы которого обьедине0 ны с одноименными информационными входами блока анализа и являются первыми информационными входами устройства, первый управляющий вход блока оценки достоверности объединен с первым управляю5 щим входом блока прогнозирования и подключен к управляющему входу устройства, информационные и счетные входы блока прогнозирования являются соответственно вторыми информационными и синхронизи0 рующими входами устройства, первые выходы блока прогнозирования соединены с одноименными адресными входами блока анализа и блока оценки достоверности, выход которого соединен с управляющим вхо5 дом блока анализа, входы уставки и установочный вход которого являются соответственно входами уставки и установочным входом устройства, второй выход блока анализа соединен с установочными входа0 ми блока оценки достоверности и блока про- гнозирования, второй выход которого соединен с вторыми управляющими входами блока оценки достоверности и программно-временного блока, первый - пятый

5 выходы которого соединены соответственно с третьим, четвертым управляющими, счетным входами блока оценки достоверности, счетным входом блока анализа и вторым управляющим входом блока прогнозирования.

2.Устройство по п. 1,отличающее- с я тем, что блок оценки достоверности содержит мультиплексор, счетчик, злемэнг оперативной памяти, компаратор и элемент И. выход которого соединен с управляющим входом компаратора, выходы мультиплексора соединены с одноименными информационными входами счетчика. аыхсЈ;. которого соединены с одноименными информационными входами элемента оперативной памяти, выходы которого соединены с одноименными первыми информационными входами компаратора и мультиплексора, вторые информационные входы компаратора и мультиплексора объединены соответст- венно и являются информационными входами блока оценки достоверности, установочные «ходы счетчика и элемента оперативной памяти объединены и являются установочным входом блока оценки достоверности, управляющий вход мультиплексора объединен с первым входом элемента И и является первым управляющим входом блока оценки достоверности, второй вход элемента И, управляющий вход элемента оперативной памяти, управляющий, счетный входы счетчика и адресные входы элемента оперативной памяти яепаются соответственно вторым, третьим, четвертым управляющими, счетным и адресными входами блока оценки достоверности, выход компаратора является выходом блока оценки достоверности.

3.Устройство по п. 1,отличающее- с я тем, что блок анализа содержит счетчики, элементы ИЛИ, элемент И, триггер, группу элементов И и демультиплексор, выходы которого соединены со счетными входами соответствующих счетчиков, первые и вторые выходы которых соединены соответственно с одноименными входами первого элемента ИЛИ и одноименными входами элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход первого элемента ИЛИ соединен с входом установки в единицу триггера, выход которого соединен с первым входом группы элементов И и вторым входом второго элемента ИЛИ, первые управляющие входы счетчиков объединены и являются управляющим входом блока анализа, информационные входы счетчиков объединены соответственно и являются входами уставки блока анализа, вход установки в ноль триггера

объединен с третьим входом второго элемента ИЛИ и является установочным входом блока анализа, вторые входы группы элементов И, информационный и адресные

входы демультиплексора являются соответственно информационными, счетным и адресными входами блока анализа, выходы группы элементов И являются первыми выходами блока анализа, выход второго

элемента ИЛ И ссединен с вторыми управляющими входами счетчиков и является вторым выходом блока анализа.

4. Устройство по п. 1,отличающее- с я тем, что, блок прогнозирования содержит элемент оперативной памяти, демультиплексор, вычитающие счетчики, суммирующий счетчик, дешифратор, элемент ИЛИ, мультиплексор и элемент И, выход которого соединен со счетным входом суммирующего счетчика и управляющим входом элемента оперативной памяти, выходы которого соединены с соответствующими информационными входами вычитающих счетчиков, выходы которых

соединены с соответствующими входами дешифратора и элемента ИЛИ, инверсный выход которого соединен с первым входом элемента И, выходы суммирующего счетчика и дешифратора соединены соответственно с одноименными первыми и вторыми информационными входами мультиплексора, выходы демультиплексора соединены с управляющими входами соответствующих вычитающих счетчиков, установочные входы элемента оперативной памяти, вычитающих счетчиков и суммирующего счетчика объединены и являются установочным входом блока прогнозирования, счетные входы вычитающих счетчиков объединены и являются счетным входом блока прогнозирования, информационные входы элемента оперативной памяти, второй вход элемента И и информационный вход демультиплексора являются соответственно информационными, первым и вторым управляющими входами блока прогнозирования, выходы мультиплексора соединены с соответствующими адресными входами элемента оперативной памяти и демультиплексора и

являются первыми выходами блока прогнозирования, прямой выход элемента ИЛИ соединен с управляющим входом мультиплексора и является вторым выходом блока прогнозирования.

Риг 2.

г

I

О)

-Сж

--J

(О

Служебная часть

Пакет информации

| название | год | авторы | номер документа |

|---|---|---|---|

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Устройство для диагностики и прогнозирования отказов | 1989 |

|

SU1629898A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

| Многоканальный цифроаналоговый преобразователь | 1989 |

|

SU1709527A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ СВЕРТОЧНОГО КОДА | 1991 |

|

RU2035124C1 |

| Устройство для анализа частоты использования блоков информации в вычислительных комплексах | 1990 |

|

SU1793442A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство сбора дефектоскопической информации | 1985 |

|

SU1298719A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

Изобретение относится к электросвязи и может использоваться для последовательного анализа сигналов декодирования. Устройство осуществляет проверку служебной части сообщения на предмет выполнения известного закона ее изменения, что повышает достоверность принимаемой информации. Устройство содержит блок 1 оценки достоверности, программно-временной блок 2, блок 3 прогнозирования, блок 4 анализа, информационные входы 5, 7, управляющий вход 6, синхронизирующий вход 8, входы 9 уставки, установочный вход 10 и выходы 11.3 з.п ф-лы, 7 ил.

Ложные сигналы Истинные сигналы

Сигналы вычитания

игналы суммиродания

А8з Ада АЧК А9п

АШ АЮи

Ложные сигналы Истинные сигнал

Сигнал разрешения i обработки информации

t

Фиг. 6

LL1U

| Устройство для обнаружения и исправления ошибок | 1984 |

|

SU1243100A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для приема и адаптивного мажоритарного декодирования дублированных сигналов | 1982 |

|

SU1073789A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1991-05-07—Публикация

1989-02-27—Подача