(Л

оо

00 оо

оо

Изобретение относится к вычислитель- ной технике и может быть использовано при проектировании и разработке логических структур дискретных систем.

Цель изобретения - повышение быстродействия элемента.

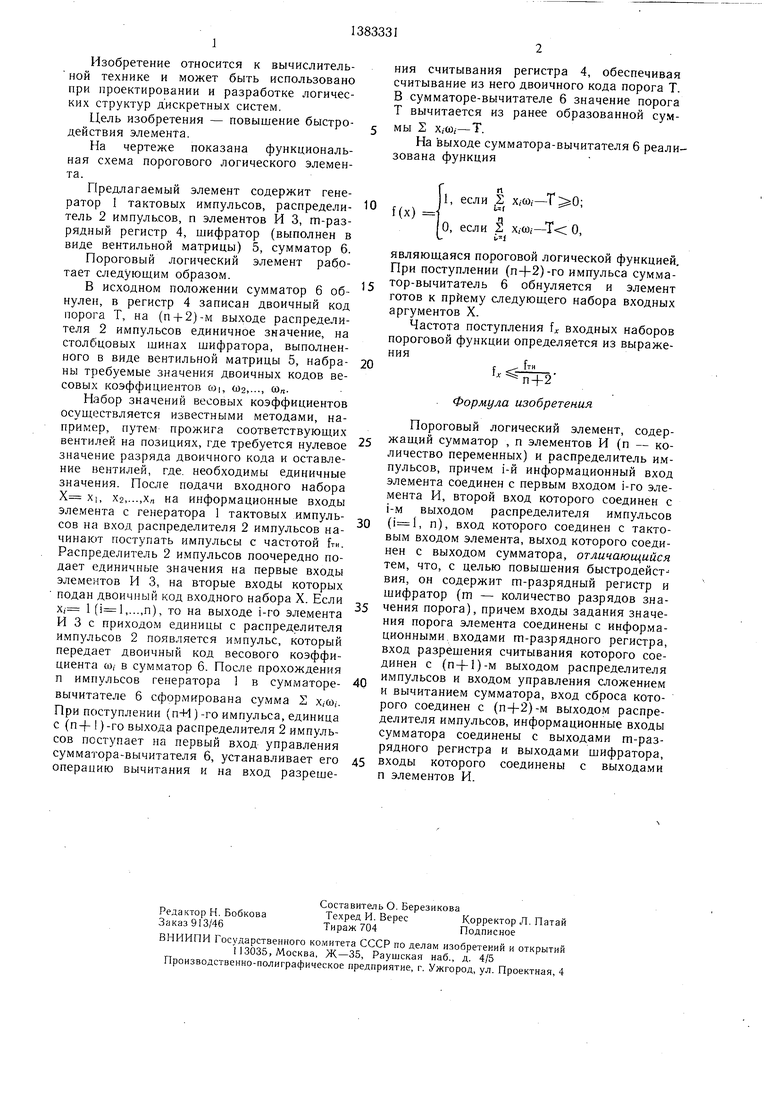

На чертеже показана функциональная схема порогового логического элемента.

Предлагаемый элемент содержит генератор 1 тактовых импульсов, распределитель 2 импульсов, п элементов И 3, т-раз- рядный регистр 4, шифратор (выполнен в виде вентильной матрицы) 5, сумматор 6.

Пороговый логический элемент работает следуюш,им образом.

В исходном положении сумматор 6 обнулен, в регистр 4 записан двоичный код порога Т, на (п + 2)-м выходе распределителя 2 импульсов единичное значение, на столбцовых шинах шифратора, выполненного в виде вентильной матрицы 5, набраны требуемые значения двоичных кодов весовых коэффициентов со|, «2,..., ««.

Набор значений весовых коэффициентов осуществляется известными методами, например, путем прожига соответствующих вентилей на позициях, где требуется нулевое значение разряда двоичного кода и оставление вентилей, где. необходимы единичные значения. Пооте подачи входного набора Х xi, Х2,...,Хл на информационные входы элемента с генератора 1 тактовых импульсов на вход распределителя 2 импульсов начинают поступать импульсы с частотой Ьи. Распределитель 2 импульсов поочередно подает единичные значения на первые входы элементов И 3, на вторые входы которых подан двоичный код входного набора X. Если х,- 1 (,...,n), то на выходе i-ro элемента И 3 с приходом единицы с распределителя импульсов 2 появляется импульс, который передает двоичный код весового коэффициента со,- в сумматор 6. После прохождения п импульсов генератора 1 в сумматоревычитателе 6 сформирована сумма 2 х,со,-. При поступлении (п-И) -го импульса, единица с (п4-1 )-го выхода распределителя 2 импульсов поступает на первый вход управления сумматора-вычитателя 6, устанавливает его операцию вычитания и на вход разрешения считывания регистра 4, обеспечивая считывание из него двоичного кода порога Т. В сумматоре-вычитателе 6 значение порога Т вычитается из ранее образованной суммы 2 х/(о,--Т.

На выходе сумматора-вычитателя 6 реализована функция

f(x) i

1tr

1, если 2 х/со,

о, если 2 х,-(о,-Т О,

5

0

5

0

5

0

5

являющаяся пороговой логической функцией. При поступлении (п+2)-го импульса сумма- тор-вычитатель б обнуляется и элемент готов к приему следующего набора входных аргументов X.

Частота поступления f входных наборов пороговой функции определяется из выражения

f

Формула изобретения

Пороговый логический элемент, содержащий сумматор , п элементов И (п - количество переменных) и распределитель импульсов, причем i-й информационный вход элемента соединен с первым входом i-ro элемента И, второй вход которого соединен с i-M выходом распределителя импульсов (, п), вход которого соединен с тактовым входом элемента, выход которого соединен с выходом сумматора, отличающийся тем, что, с целью повышения быстродействия, он содержит ш-разрядный регистр и шифратор (т - количество разрядов значения порога), причем входы задания значения порога элемента соединены с информационными, входами т-разрядного регистра, вход разрешения считывания которого соединен с (п + 1)-м выходом распределителя импульсов и входом управления сложением и вычитанием сумматора, вход сброса которого соединен с (п+2)-м выходом распределителя импульсов, информационные входы сумматора соединены с выходами т-разрядного регистра и выходами шифратора, входы которого соединены с выходами п элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый логический элемент | 1987 |

|

SU1439571A2 |

| ДЕКОДЕР СВЕРТОЧНОГО КОДА | 1992 |

|

RU2085035C1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

| Пороговый многофункциональный элемент | 1988 |

|

SU1608642A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Устройство для вычисления функций | 1987 |

|

SU1411775A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Изобретение относится к вычислительной технике и может быть использовано при проектировании и разработке логических структур дискретных систем | |||

| Целью изобретения является повышение быстродействия элемента | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цель достигается за счет программируемого задания порога и весовых коэффициентов порогового логического элемента | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-03-23—Публикация

1986-06-13—Подача