ff Г7 Я И

(Л

со X со со

4:; t

Ф1Л1

W

представлении операндов и результата достигается другим методом ввода знака для кодирования цифры, позволяющей сократить диапазон ее пр.ед ставления и использовать новый алгоритм алгебраического сложения в зна- коразрядной позиционно-остаточной системе счисления и новые аппаратно- схемные решения. Исходя из этого, сумматор в знакоразрядной позиционно-остаточной системе счисления, содержащий группы дешифраторов 1, 2,

83349

группу матриц 4 элементов И, группу шифраторов 5 сложения, группу блоков 10 шифрации суммы, блок 11 сравнения промежуточной суммы с набором констант и блок 9 формирования сигналов переноса, содержит блок 3 сравнения слагаемых с набором констант, группу шифраторов 6 вычитания, группу коммутаторов 7, блок 8 задания вида операции и блок I2 формирования знака с соответствующими связями. 5 з.п. ф-лы, 8 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2006 |

|

RU2336562C2 |

| МОДУЛЬ ДЛЯ ОРГАНИЗАЦИИ ОБМЕНА СООБЩЕНИЯМИ | 2007 |

|

RU2359320C2 |

| Устройство для распознавания функциональной полноты систем логических функций | 1979 |

|

SU960795A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ СОВМЕСТНО ХРАНИМЫХ ГРАНИЦ ПРИ ИНТЕРВАЛЬНЫХ ВЫЧИСЛЕНИЯХ | 2012 |

|

RU2497179C1 |

| Вычислительная система "Антикон" для предотвращения столкновения судов | 1983 |

|

SU1136178A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2016 |

|

RU2613844C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 2004 |

|

RU2280278C1 |

| Система записи и воспроизведения видеосигнала | 1990 |

|

SU1783635A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРИВОДОМ РОБОТА | 2007 |

|

RU2355563C2 |

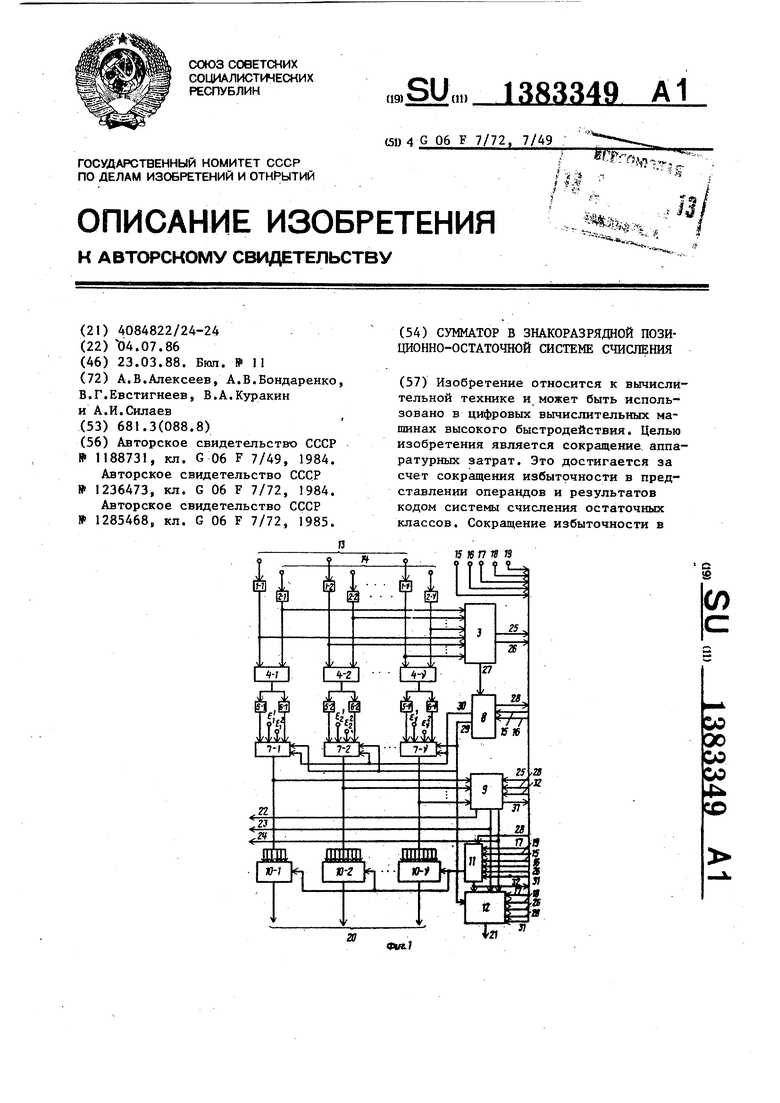

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах высокого быстродействия. Целью изобретения является сокращение аппаратурных затрат. Это достигается за счет сокращения избыточности в представлении операндов и результатов кодом системы счисления остаточных классов. Сокращение избыточности в

1

Изобретение относится к вычислительной технике и может быть использовано при построении цифровых вычис лительных машин высокого быстродействия, в частности в системах автоматизированного управления и цифровой обработки сигналов.

Цель изобретения - сокращение аппаратурных затрат.

Особенностью технического решения является реализация нового алгоритма алгебраического суммирования в знако разрядной позиционно-остаточной системе счисления, основанного на оригинальном методе введения знака.

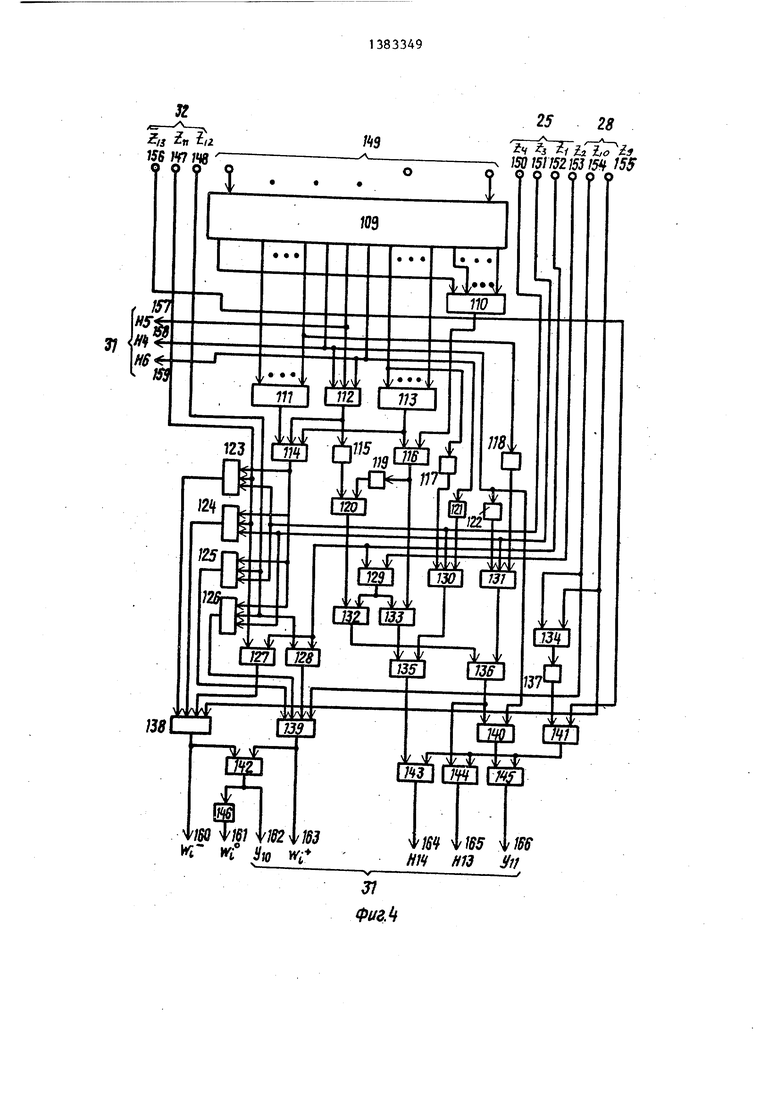

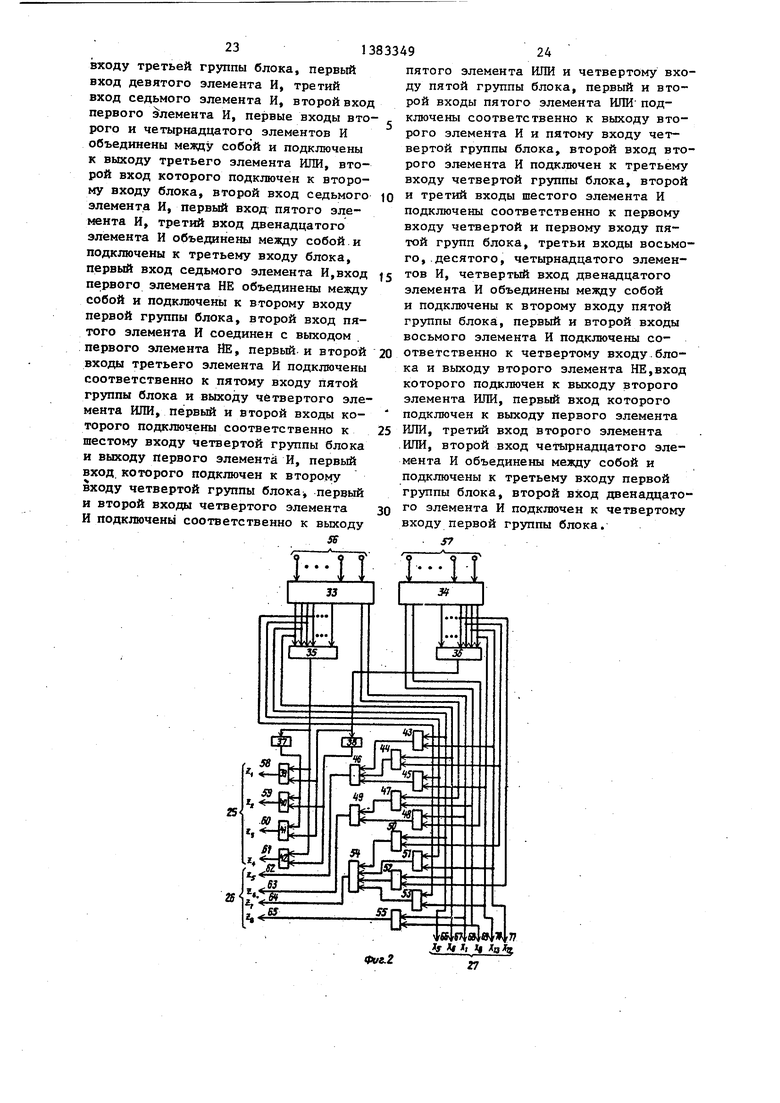

На фиг.) представлена схема сумматора в знакоразрядной позиционно-остаточной системе счисления; на фиг.2 схема блока сравнения слагаемых с набором констант; на фиг. 3 - схема блока задания вида операции;на фиг.4- схема блока формирования сигналов переноса; на фиг.5 - схема блока сравнения промежуточной суммы с набором констант; на фиг.6 - схема блока формирования знака; на фиг.7 - схема сумматора по модулю три; на фиг.8 - схема блока шифрации суммы для модуля три.

Сумматор в знакоразрядной позиционно-остаточной системе счисления (фиг.1) содержит первую и вторую гр;/ппы из О дешифраторов I и 2, блок 3 сравнения слагаемых с набором констант, группу из Q матриц 4 элементов И, группу из - шифраторов 5 спо- жения, группу из -5 шифраторов 6 вычитания , группу- из коммутаторов 7,

блок 8 задания вида операции, блок 9 формирования сигналов переноса, группу из Q блоков 10 шифрации суммы, с блок II сравнения промежуточной суммы с набором констант, блок 12 формирования знака, вход 13 первого слагаемого сумматора, вход 14 второго слагаемого сумматора, вход 15 знака пер10 вого слагаемого сумматора, вход 16 знака второго слагаемого сумматора, входы 17, 18 и 19 соответственно отрицательного, нулевого и положительного переносов сумматора, выход 20 15 суммы сумматора, выход 21 знака сумматора, выходы 22, 23 и 24 соответственно отрицательного, нулевого и положительного переносов сумматора, первую 25, вторую 26 -и третью 27

20 группы выходов блока 3 сравнения слагаемых с набором констант, первую 28, вторую 29 и третью 30 группы выходов блока 8 задания вида операции, группу 31 выходов блока 9 формирова25 ния сигналов переноса, вторую группу 32 выходов блока 11 сравнения промежуточной суммы с набором констант.

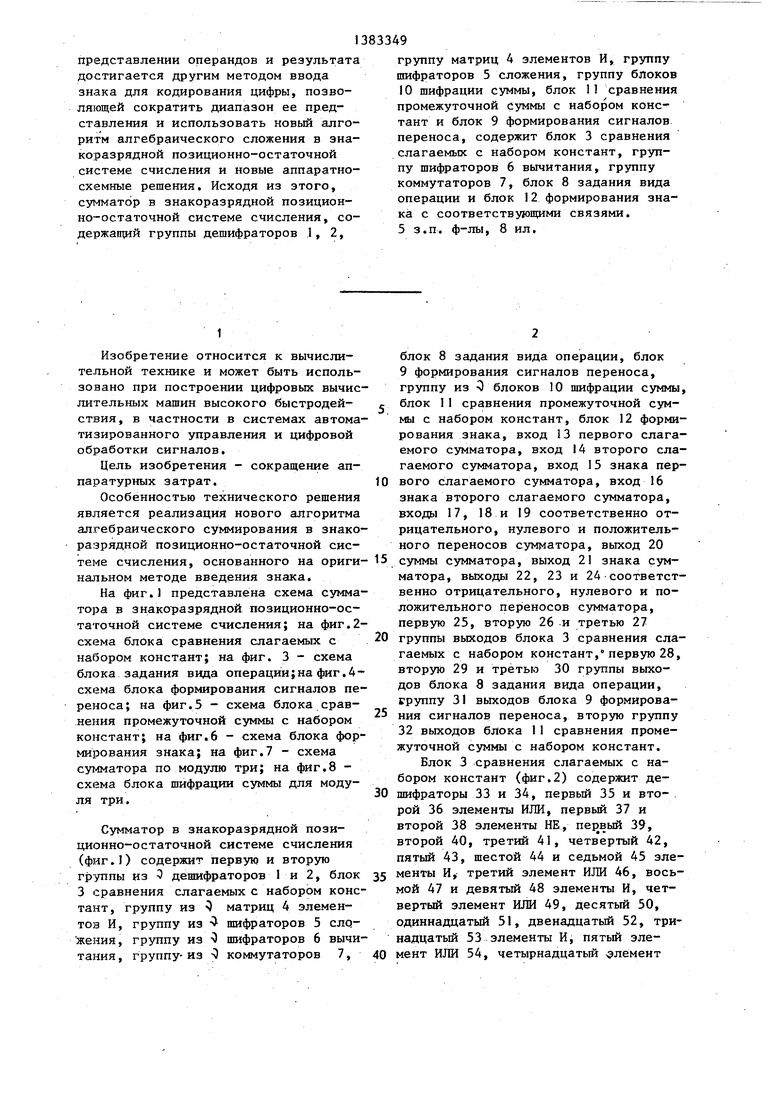

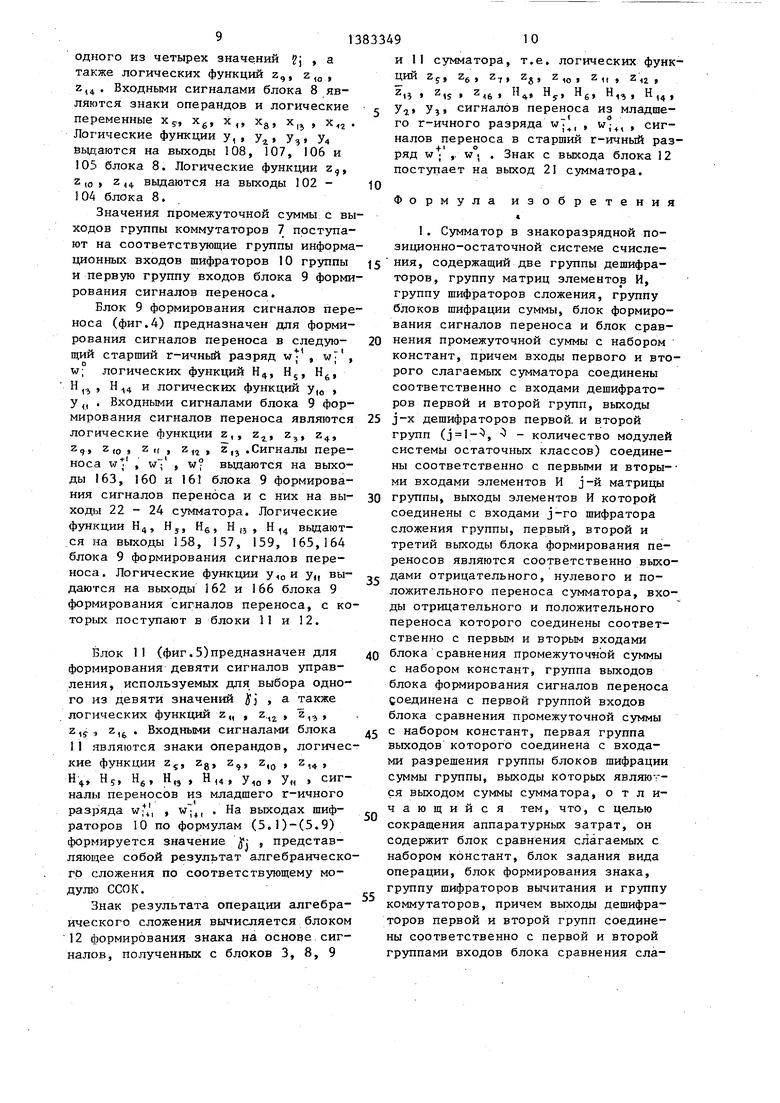

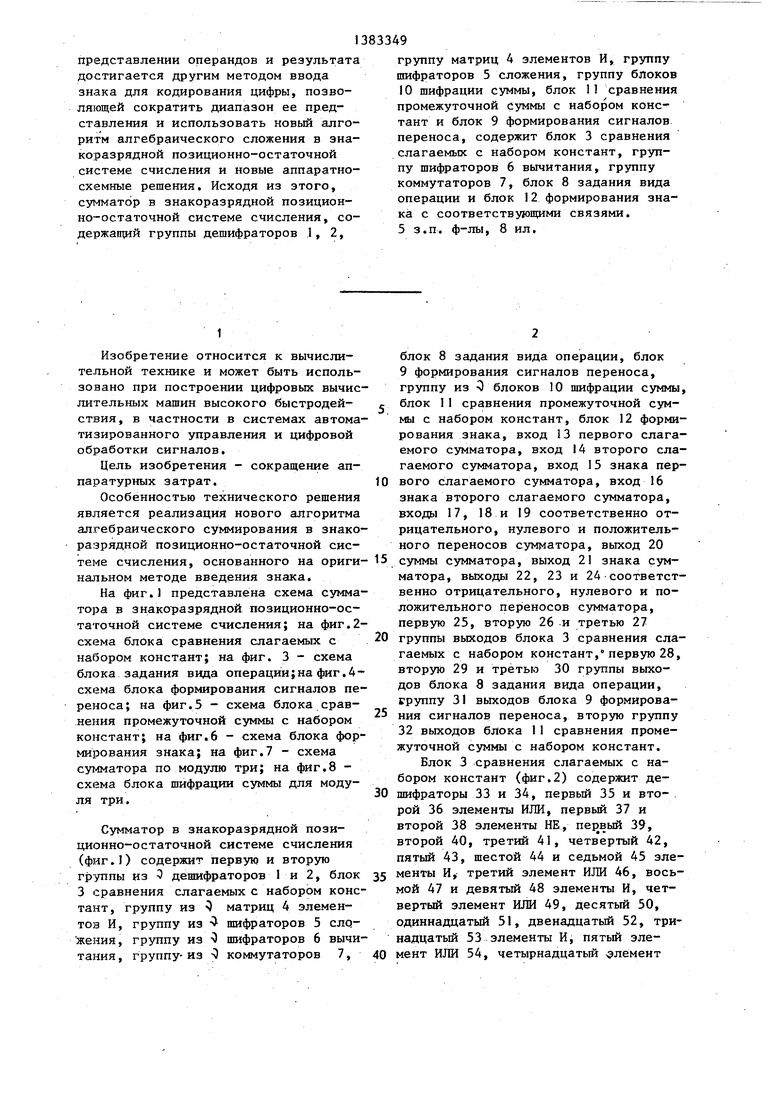

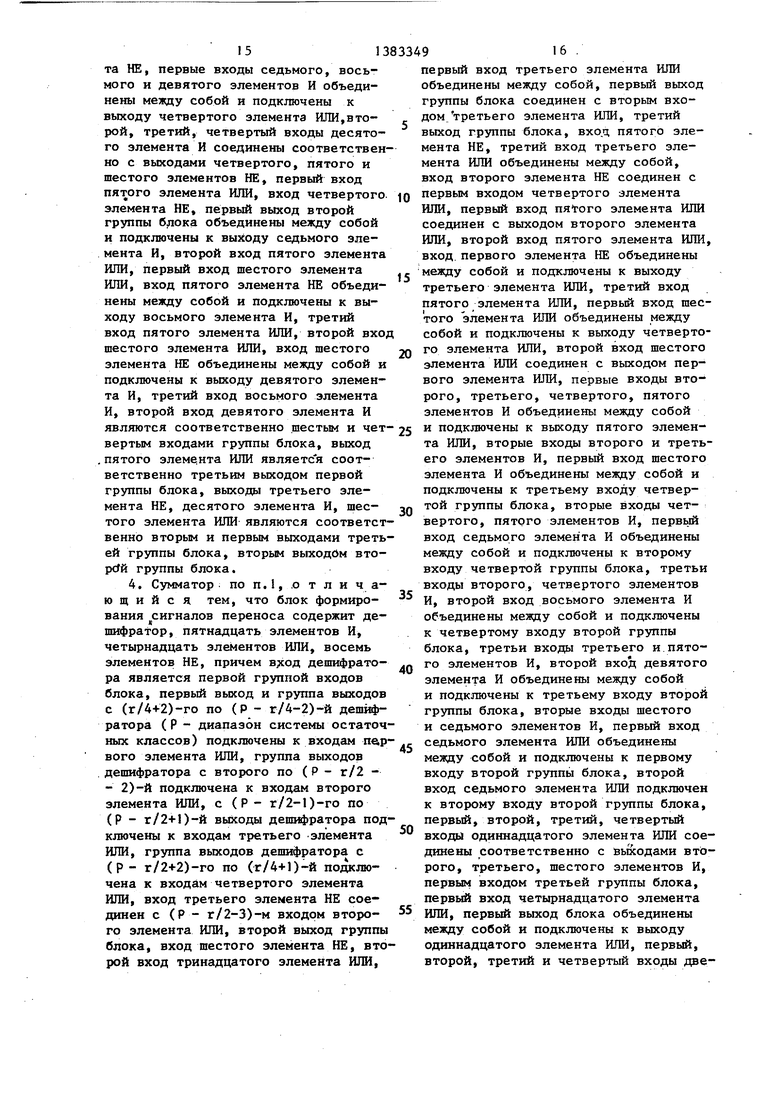

Блок 3 сравнения слагаемых с набором констант (фиг.2) содержит де30 шифраторы 33 и 34, первый 35 и второй 36 элементы ИЛИ, первый 37 и второй 38 элементы НЕ, пе1звый 39, второй 40, третий 41, четвертый 42, пятый 43, шестой 44 и седьмой 45 эле35 менты И, третий элемент ИЛИ 46, восьмой 47 и девятый 48 элементы И, четвертый элемент ИЛИ 49, десятый 50, одиннадцатый 51, двенадцатый 52, тринадцатый 53 элементы И, пятый эле0 мент ИЛИ 54, четырнадцатый олемент

И 55,первую 56 и вторую 57 группы входов с первого по четвертый выходы 58-61 первой группы 25 выходов блока 3, с первого по четвертый выходы 62-65 второй группы 26 выходов бл015а 3, с первого .по шестой выходы 66-71 третьей группы 27 выходов блока 3. Дешифраторы 33 и 34 преобразуют код системы остаточных классов в унитарный код. Наиболее целесообразна реализация блока 3 в виде одной программируемой логической матрицы (ПЛМ),

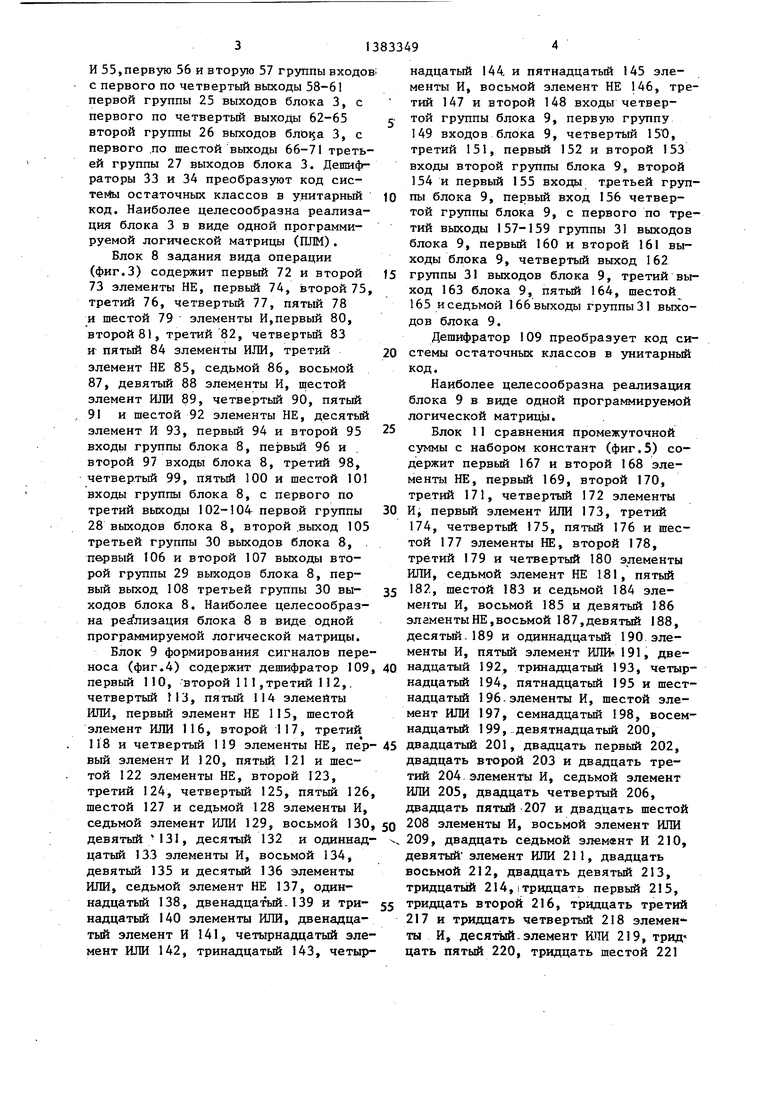

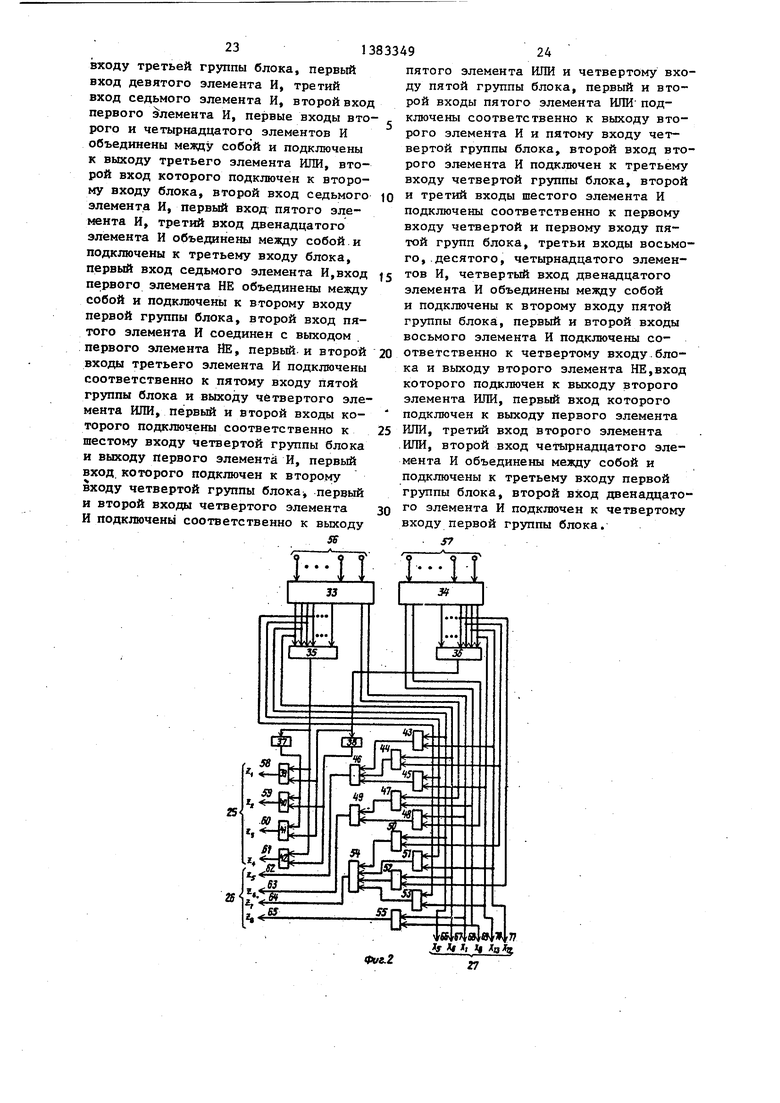

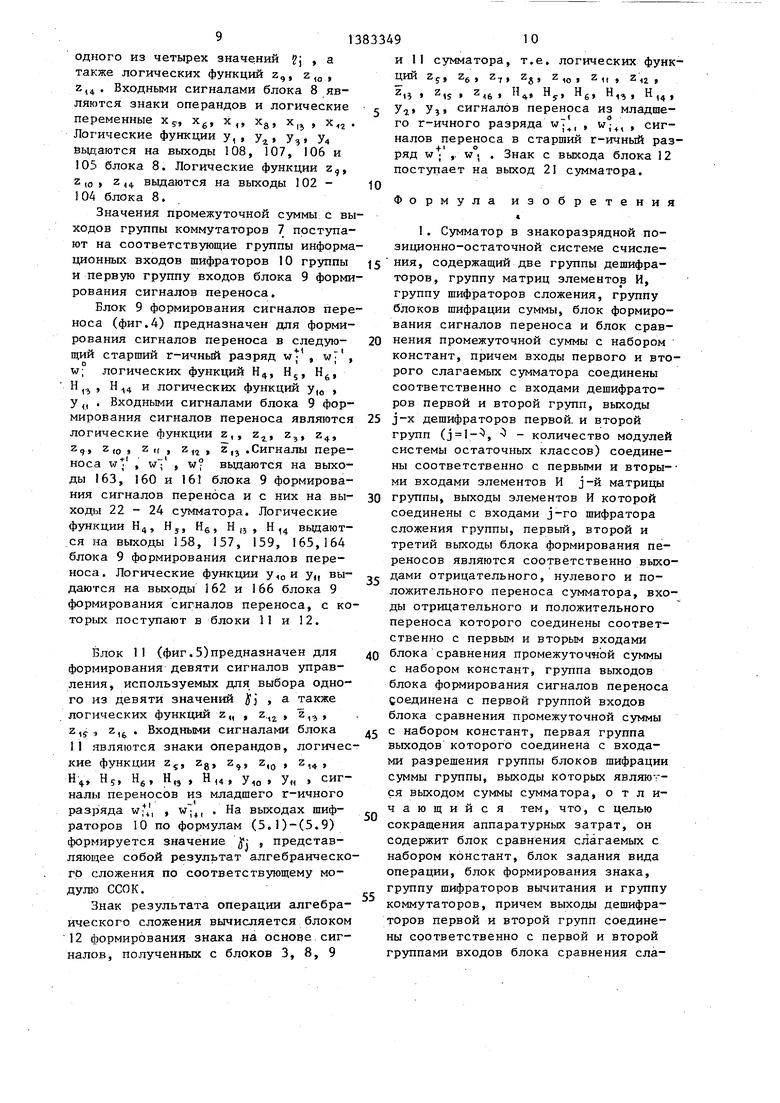

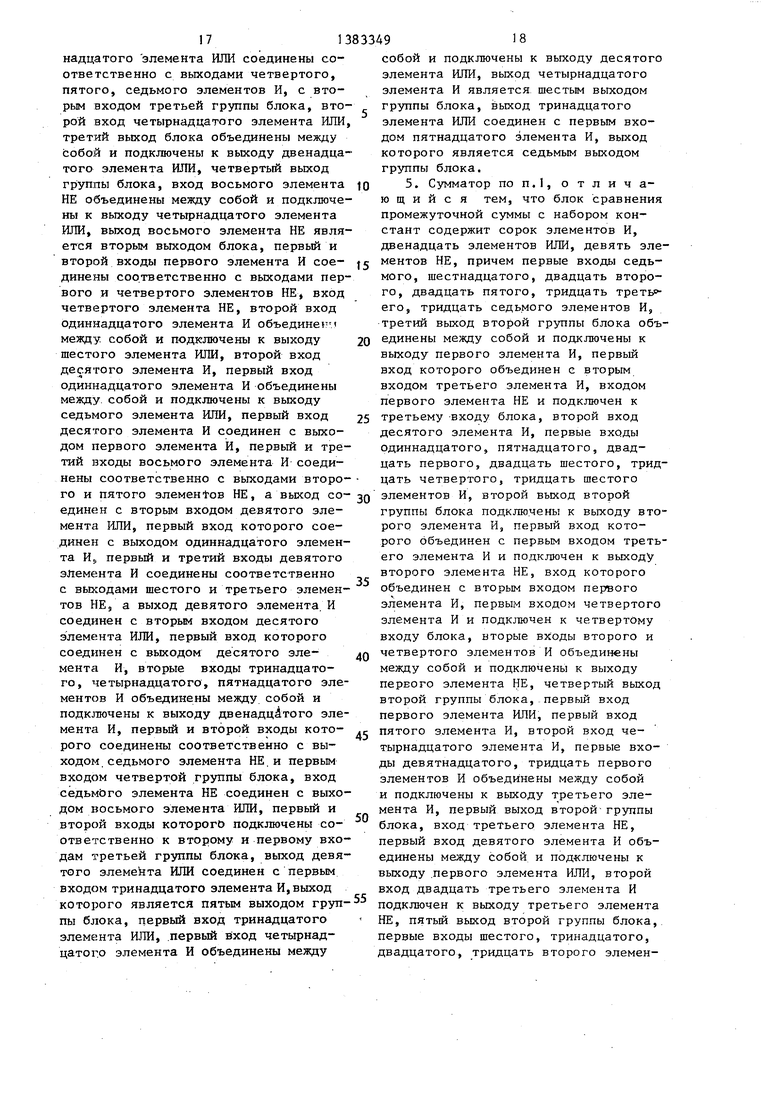

Блок 8 задания вида операции (фиг.З) содержит первый 72 и второй 73 элементы НЕ, первый 74, второй 75, третий 76, четвертый 77, пятый 78 и шестой 79 элементы И,первый 80, второй 81, третий 82, четвертый 83 и пятый 84 элементы ИЛИ, третий элемент НЕ 85, седьмой 86, восьмой 87, девятый 88 элементы И, шестой элемент ИЛИ 89, четвертый 90, пятый 91 и шестой 92 элементы НЕ, десятый элемент И 93, первый 94 и второй 95 входы группы блока 8, первый 96 и второй 97 входы блока 8, третий 98, четвертый 99, пятый 100 и шестой 101 входы группы блока 8, с первого по третий выходы 102-104 первой группы 28 выходов блока 8, второй .выход 105 третьей группы 30 выходов блока 8, . первый 106 и второй 107 выходы второй группы 29 выходов блока 8, первый выход 108 третьей группы 30 вы- ходов блока 8. Наиболее целесообразна реализация блока 8 в виде одной программируемой логической матрицы.

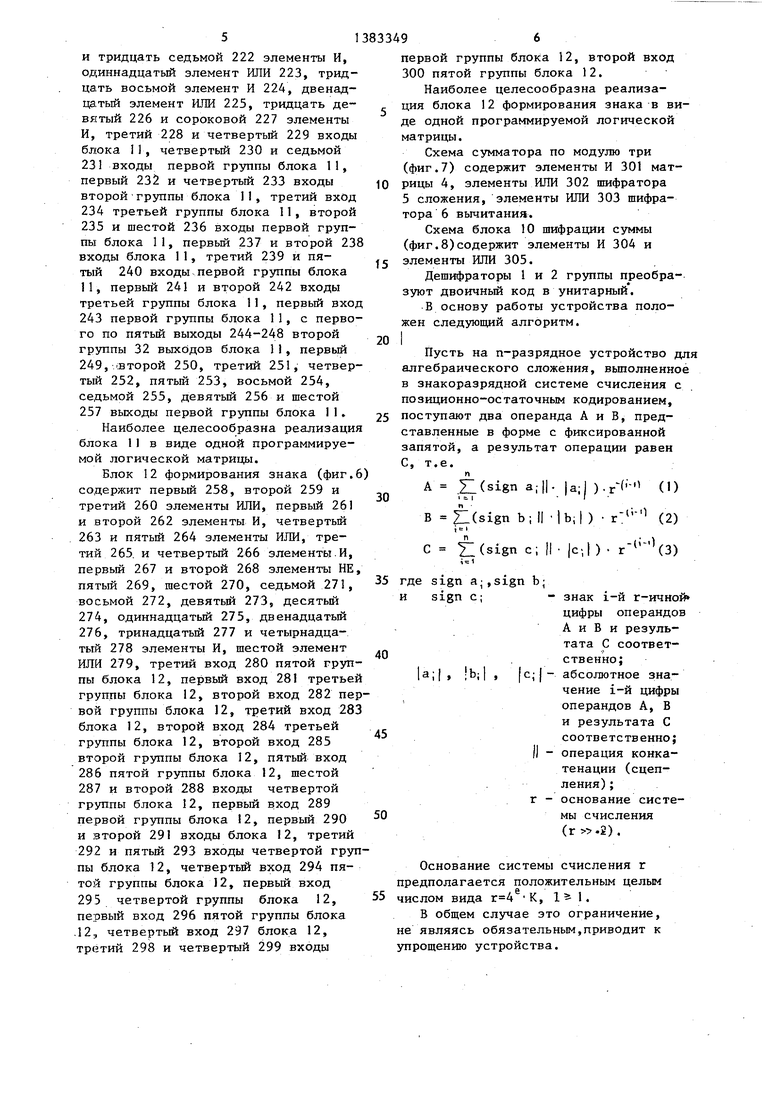

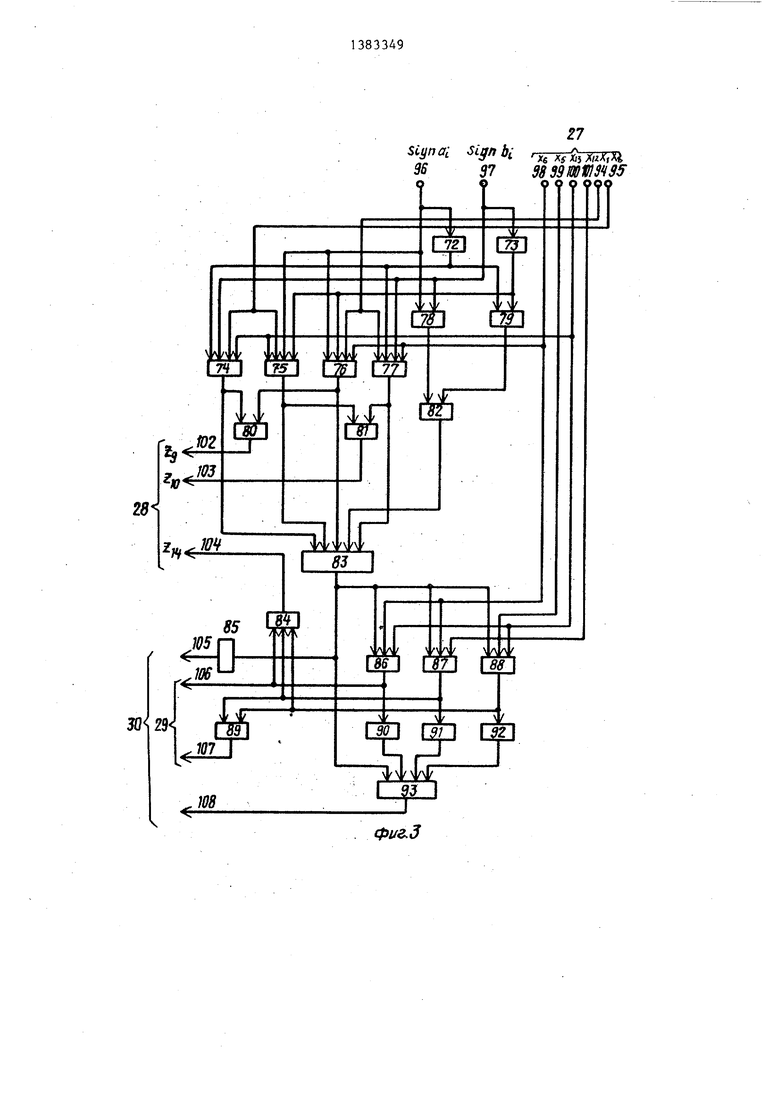

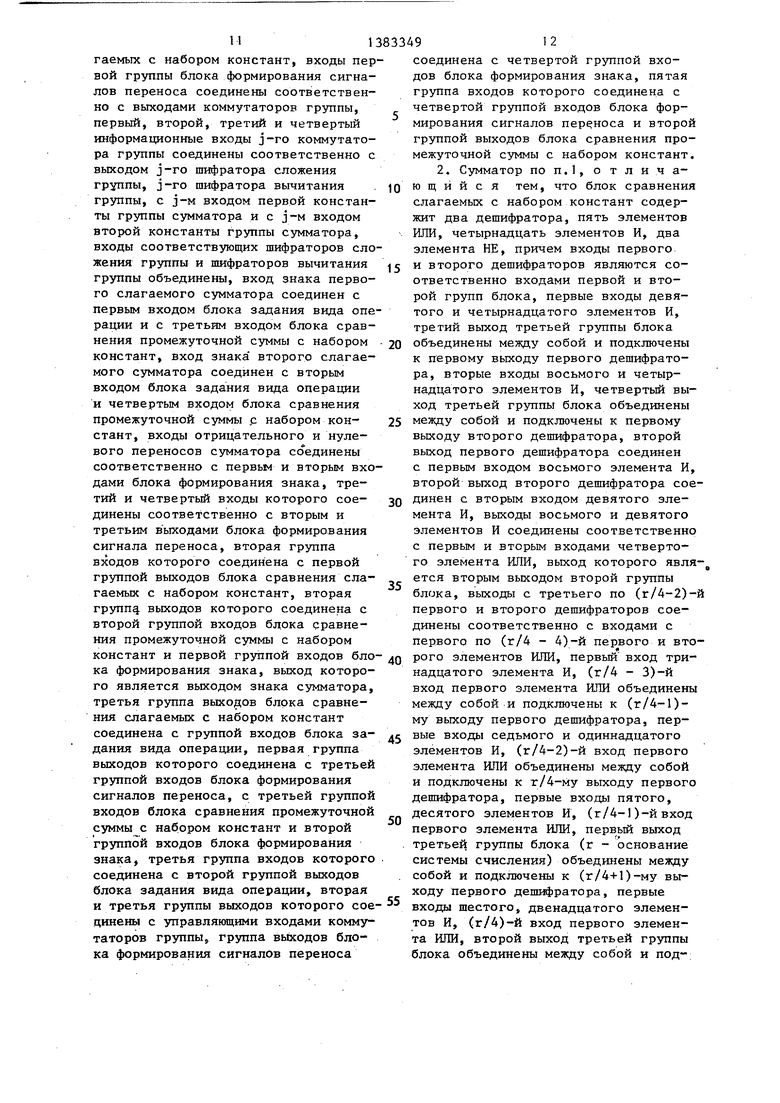

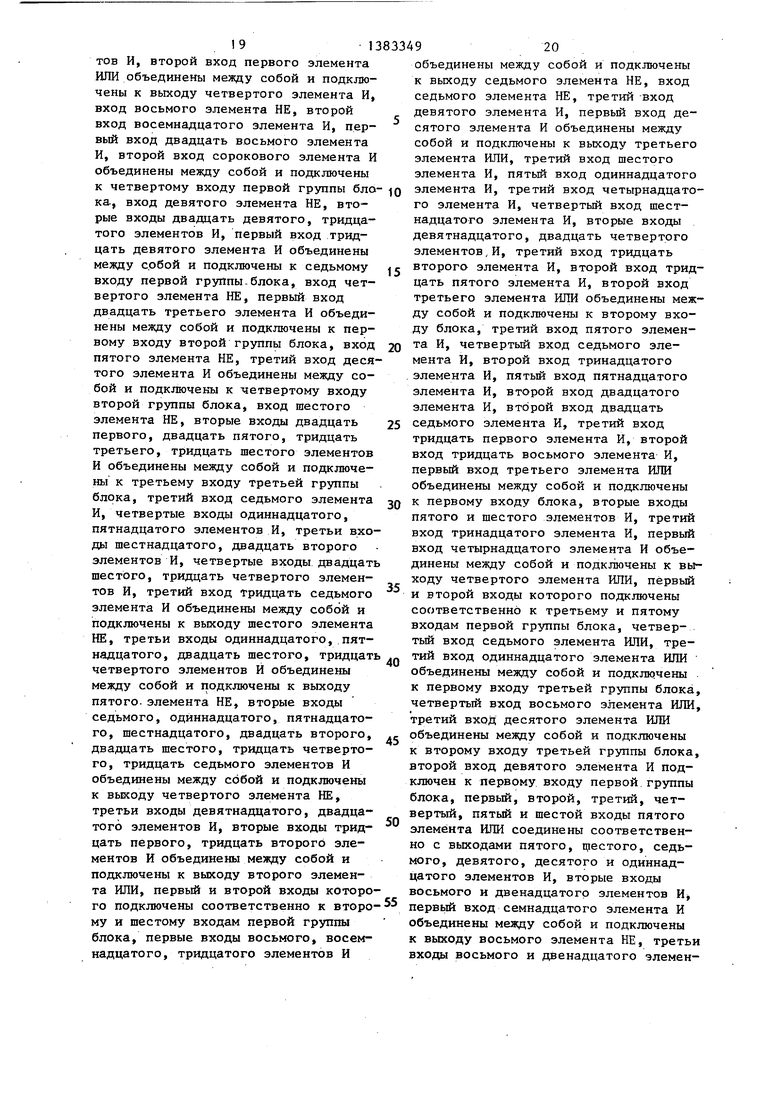

Блок 9 формирования сигналов переноса (фиг.4) содержит дешифратор 109 первый ПО, второй 111 ,третий 11 2,. четвертый 113, пятый 114 элемейты ИЛИ, первый элемент НЕ 115, шестой элемент ИЛИ 116, второй 117, третий 118 и четвертый 119 элементы НЕ, пер- вый элемент И 120, пятый 121 и шестой 122 элементы НЕ, второй 123, третий 124, четвертьй 125, пятый 126, шестой 127 и седьмой 128 элементы И, седьмой элемент ИЛИ 129, восьмой 130 девятый 431, десятый 132 и одиннад- цатый 133 элементы И, восьмой 134, девятый 135 и десятый 136 элементы ИЛИ, седьмой элемент НЕ 137, одиннадцатый 138, двенадцатый-139 и три- надцатый 140 элементы ИЛИ, двенадцатый элемент И 141, четырнадцатый элемент ИЛИ 142, тринадцатый 143, четырнадцатый 144. и пятнадцатый 145 элементы И, восьмой элемент НЕ 146, третий 147 и второй 148 входы четвертой группы блока 9, первую группу 149 входов блока 9, четвертый 150, третий 151, первый 152 и второй 153 входы второй группы блока 9, второй 154 и первый 155 входы третьей группы блока 9, первый вход 156 четвертой группы блока 9, с первого по третий выходы 157-159 группы 31 выходов блока 9, первый 160 и второй 161 выходы блока 9, четвертый выход 162 группы 31 выходов блока 9, третий выход 163 блока 9, пятый 164, шестой 165 иседьмой 166 выходы группы 31 выходов блока 9.

Дешифратор 109 преобразует код системы остаточных классов в унитарный код,

Наиболее целесообразна реализация блока 9 в виде одной программируемой логической матриць.

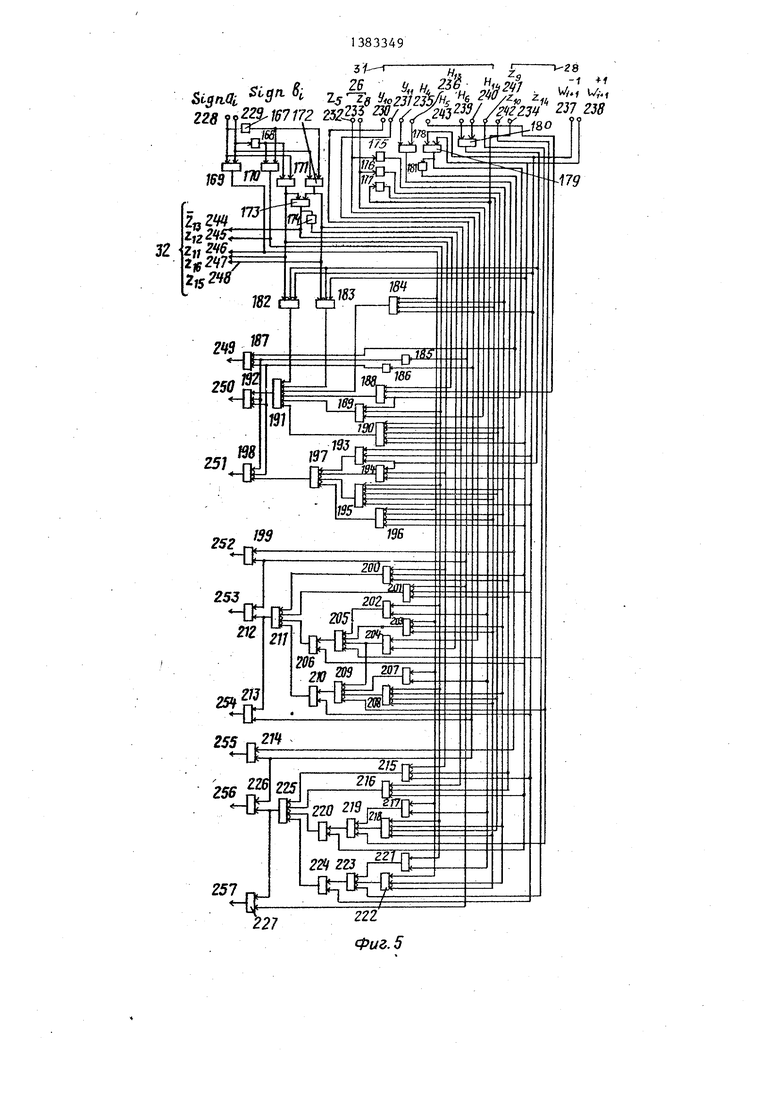

Блок 11 сравнения промежуточной суммы с набором констант (фиг.З) содержит первый 167 и второй 168 элементы НЕ, первый 169, второй 170, третий 171, четвертый 172 элементы И, первый элемент ИЛИ 173, третий 174, четвертый 175, пятый 176 и шестой 177 элементы НЕ, второй 178, третий 179 и четвертый 180 элементы ИЛИ, седьмой элемент НЕ 181, пятый 182, шестой 183 и седьмой 184 элементы И, восьмой 185 и девятый 186 элементы НЕ, восьмой 187,девятый 188, десятьш-189 и одиннадцатый 190 элементы И, пятый элемент ИЛИч 191, двенадцатый 192, тринадцатый 193, четырнадцатый 194, пятнадцатый 195 и шестнадцатый 196-элементы И, шестой элемент ИЛИ 197, семнадцатый 198, восемнадцатый 199, девятнадцатый 200, двадцатый 201, двадцать первый 202, двадцать второй 203 и двадцать третий 204 элементы И, седьмой элемент ИЛИ 205, двадцать четвертый 206, двадцать пятый 207 и двадцать шестой 208 элементы И, восьмой элемент ИЛИ 209, двадцать седьмой элемент И 210, девятый элемент ИЛИ 211, двадцать восьмой 212, двадцать девятый 213, тридцатьй 214,Тридцать первый 215, тридцать второй 216, тридцать третий 217 и тридцать четвертый 218 элементы И, десятый-элемент ЮТИ 219, трид цать пятый 220, тридцать шестой 221

и тридцать седьмой 222 элементы И, одиннадцатый элемент ИЛИ 223, тридцать восьмой элемент И 224, двенадцатый элемент ИЛИ 225, тридцать девятый 226 и сороковой 227 элементы И, третий 228 и четвертый 229 входы блока i1, четвертьй 230 и седьмой 231 входы первой группы блока 11, первый 232 и четвертый 233 входы второй группы блока 11, третий вход

234третьей группы блока 11, второй

235и шестой 236 входы первой группы блока 11, первый 237 и второй 238 входы блока 11, третий 239 и пятый 240 входы первой группы блока 11, первый 241 и второй 242 входы третьей группы блока 11, первый вход 243 первой группы блока 11, с первого по пятьй выходы 244-248 второй группы 32 выходов блока 11, первый

249, шторой 250, третий 251, четвертый 252, пятый 253, восьмой 254, седьмой 255, девятый 256 и шестой 257 выходы первой группы блока 11,

Наиболее целесообразна реализация блока 11 в виде одной программируемой логической матрицы.

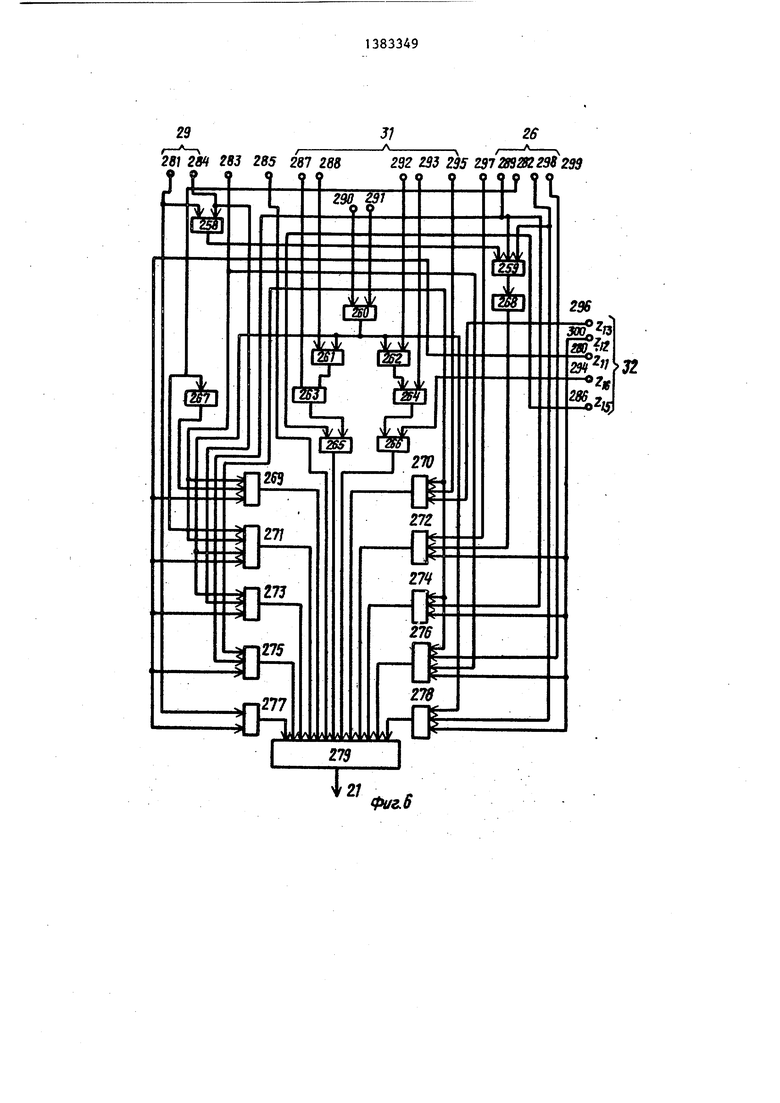

Блок 12 формирования знака (фиг.6 содержит первый 258, второй 259 и третий 260 элементы ИЛИ, первый 261 и второй 262 элементы И, четвертый 263 и пятый 264 элементы ИЛИ, третий 265. и четвертый 266 элементы.И, первый 267 и второй 268 элементы НЕ, пятый 269, шестой 270, седьмой 271, восьмой 272, девятый 273, десятый 274, одиннадцатый 275, двенадцатый 276, тринадцатый 277 и четырнадцатый 278 элементы И, шестой элемент ИЛИ 279, третий вход 280 пятой группы блока 12, первый вход 281 третьей группы блока 12, второй вход 282 первой группы блока 12, третий вход 283 блока 12, второй вход 284 третьей группы блока 12, второй вход 285 второй группы блока 12, пятый вход

286пятой группы блока 12, шестой

287и второй 288 входы четвертой группы блока 12, первый вход 289 первой группы блока 12, первый 290 и второй 291 входы блока 12, третий

292 и пятый 293 входы четвертой грзш пы блока 12, четвертый вход 294 пятой группы блока 12, первый вход 295 четвертой группы блока 12, первый вход 296 пятой группы блока ,12,, четвертый вход 297 блока 12, третий 298 и четвертый 299 входы

5

,.

5

первой группы блока 12, второй вход 300 пятой группы блока 12.

Наиболее целесообразна реализация блока 12 формирования знака в виде одной программируемой логической матрицы.

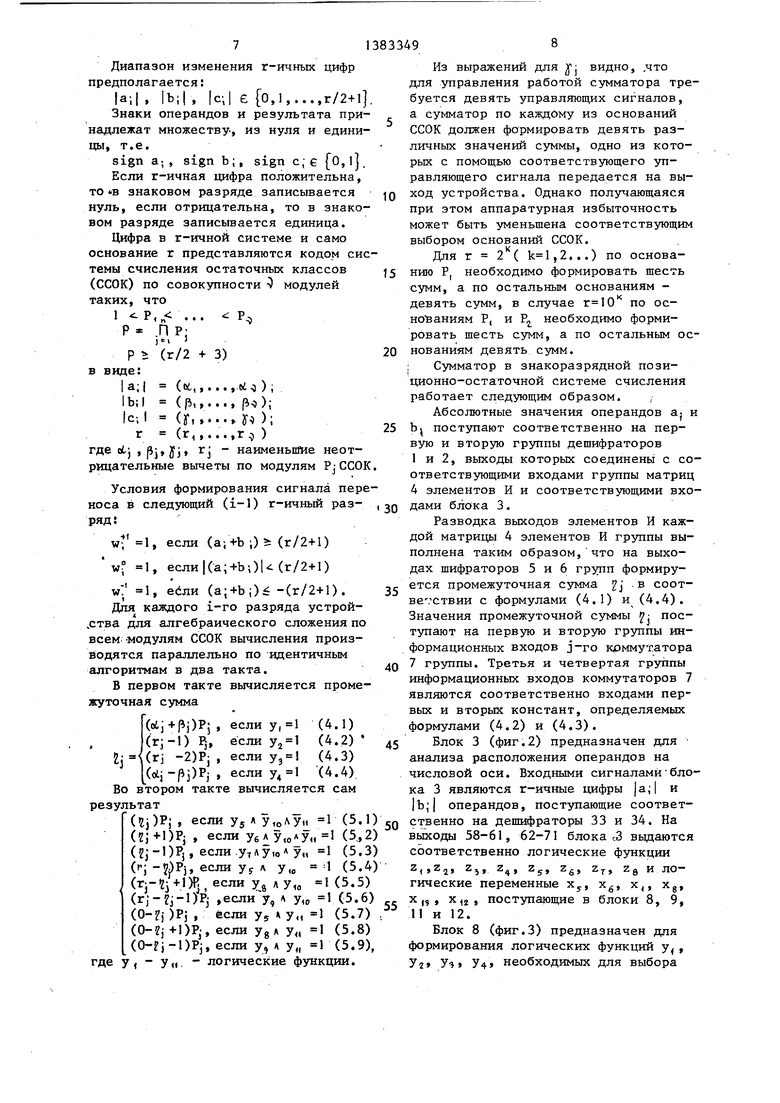

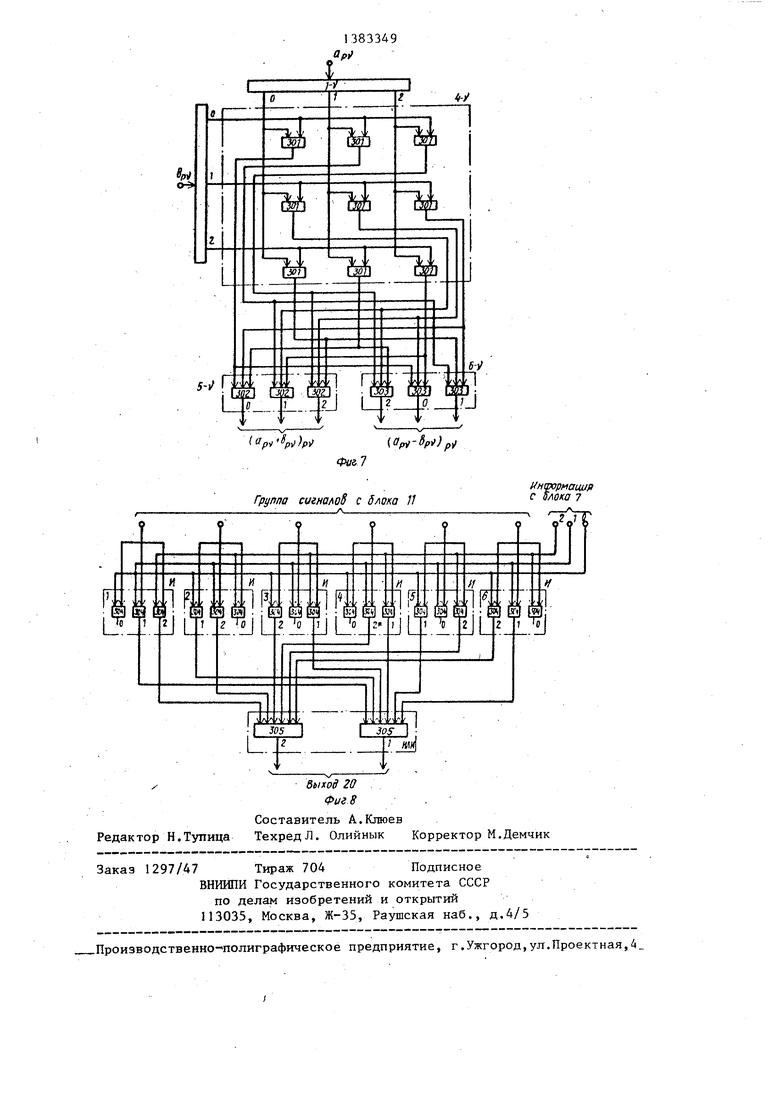

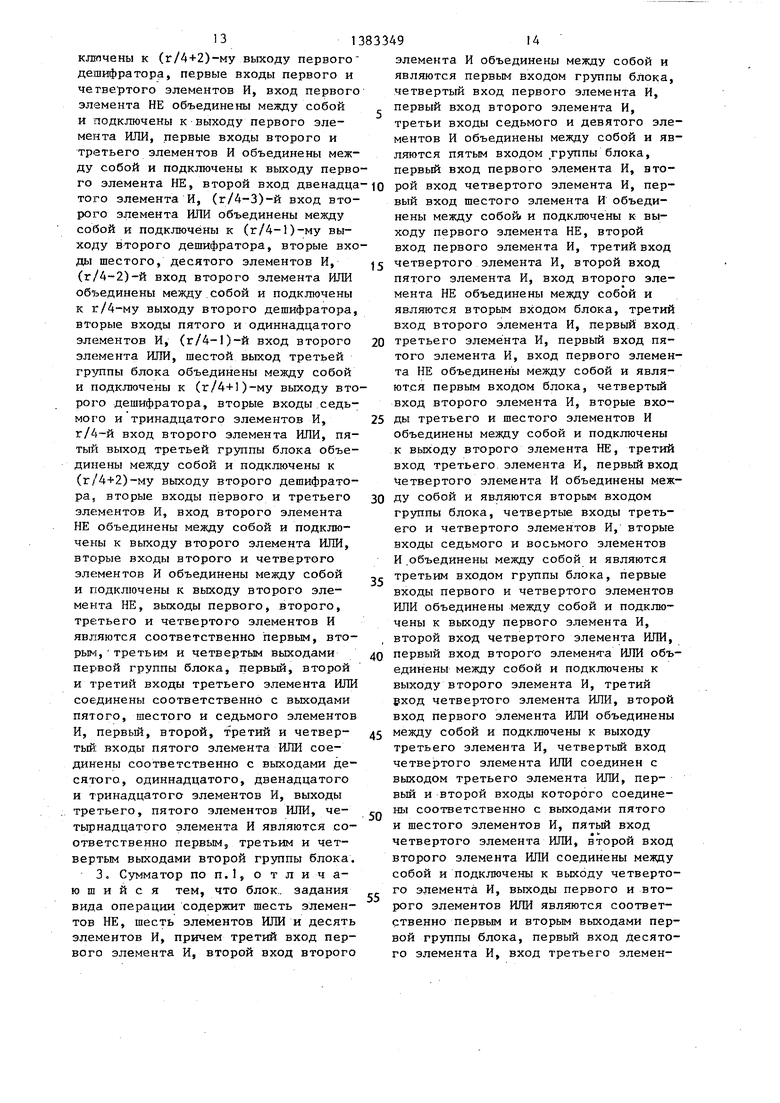

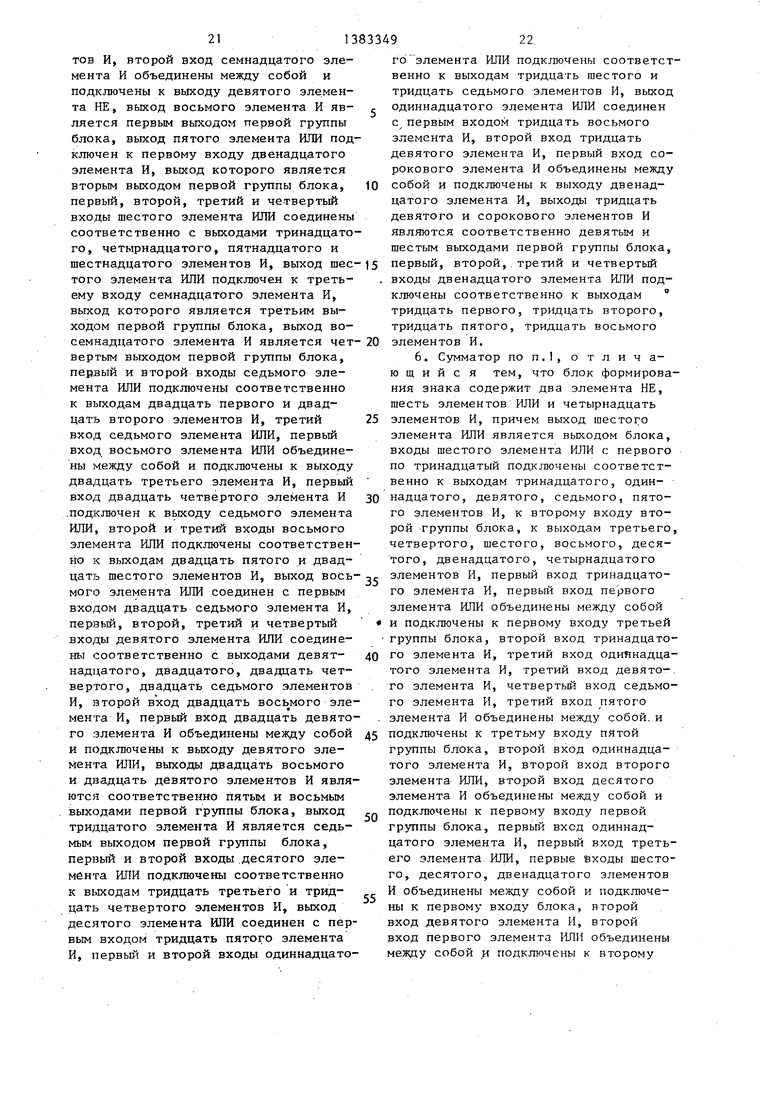

Схема сумматора по модулю три (фиг.7) содержит элементы И 301 матрицы 4, элементы ИЛИ 302 шифратора 5 сложения, элементы ИЛИ 303 шифратора 6 вычитания.

Схема блока 10 шифрации суммы (фиг.8)содержит элементы И 304 и элементы ИЛИ 305.

Дешифраторы 1 и 2 группы преобразуют двоичный код в унитарный.

В основу работы устройства положен следующий алгоритм.

Пусть на п-разрядное устройство для алгебраического сложения, вьшолненное в знакоразрядной системе счисления с позиционно-остаточным кодированием, поступают два операнда А и В, представленные в форме с фиксированной запятой, а результат операции равен С, т.е.

А ZKsign а; 11- |а;1 ). (1)

1 1 I I

В i:(sign b;lMbi|) r: - (2)

.-(i-),

fi n

С ZKsign c; II |c;| ) . r

(3)

5

где sign a;,sign b; и sign c;

- знак i-й r-ичной цифры операндов A и В и результата С соответственно;

1а;, ;Ь;| , (с;|- абсолютное значение i-й цифры операндов А, В и результата С соответственно; 11 - операция конкатенации (сцепления) ;

г - основание системы счисления (г.2).

Основание системы счисления г предполагается положительным целым числом вида К, 1-1.

В общем случае это ограничение, не являясь обязательным,приводит к упрощению устройства.

Диапазон изменения г-ичных цифр предполагается

|а-,| , Ibil , |с;| o,l,...,r/2+l.

Знаки операндов и результата принадлежат множеству, из нуля и единицы, т.е.

sign а,, signb;, sign с; е О,l.

Если г-ичная цифра положительна, то в знаковом разряде записывается нуль, если отрицательна, то в знаковом разряде записывается единица.

Цифра в г-ичной системе и само основание г представляются кодом системы счисления остаточных классов (ССОК) по совокупности модулей

. Р + 3)

(et,в );

... р-}); (1Г|...у-); (г,,...,г )

где otj , pjtj наименьшие неотрицательные вычеты по модулям PjCCOK

Условия формирования сигнала переноса в следующий (i-1) г-ичный раз- ряд:

1, если (а;+Ь ;) s (r/2+l) 1, если |(a;+bOU (r/2+l)

1, ебли (a;+bi)i -(r/2+l).

Для каждого i-го разряда устрой- ,ства для алгебраического сложения по всем модулям ССОК вычисления производятся параллельно по идентичным алгоритмам в два такта.

В первом такте вычисляется промежуточная сумма

fi

w;

Wi

w

l

(otj+pj)Pj , если у, 1

(rj-1) Pj, если yj l (rj -2)Pj , если уз 1 (otj-pj)Pj- , если

45

50

(4.1) (4.2) (4.3)

( Bo B TOpOM такте вычисляется сам

езультат

(j)Pis если У5 А у,олу„ 1 (5.1) («j+OPj , если УбАу„, (5.,2) (2j-l)P,, если утлу, 1 (5.3) (г; -j:)Pj, если у л у,„ 1 (5.4) ( +1)Р-, если Yg А у,о 1 (5.5) ()Pj ,если, л у,о 1 (5.6) ( )Pj , если У5 А у„ 1 (5.7) ,. ()P-, если ygA у, 1 (5.8) ( -l)Pj, если у, А у„ 1 (5.9),

де у, - У(1 логические функции.

Из выражений для j видно, .что для управления работой сумматора требуется девять управляющих сигналов, а сумматор по каждому из оснований ССОК должен формировать девять различных значений суммы, одно из которых с помощью соответствующего управляющего сигнала передается на выход устройства. Однако получающаяся при этом аппаратурная избыточность может быть уменьшена соответствующим выбором оснований ССОК.

Для г 2( ,2...)

нию Р

по основа- необходимо формировать шесть

0

д

35

0

45

0

сумм, а по остальным основаниям - девять сумм, в случае

по ОС- необходимо формино ваниям Р, и P,j

ровать щесть сумм, а по остальным основаниям девять сумм. Сумматор в знакоразрядной пози- ционно-остаточной системе счисления работает следующим образом. /

Абсолютные значения операндов а- и 5 Ь поступают соответственно на первую и вторую группы дешифраторов 1 и 2, выходы которых соединены с соответствующими входами группы матриц 4 элементов И и соответствующими входами блока 3.

Разводка выходов элементов И каждой матрицы 4 элементов И группы выполнена таким образом, что на выходах шифраторов 5 и 6 групп формируется промежуточная сумма j .в соответствии с формулами (4.1) и (4.4). Значения промежуточной : поступают на первую и вторую грзшпы информационных входов J-го крммут.атора 7 группы. Третья и четвертая группы информационных входов коммутаторов 7 являются соответственно входами первых и вторых констант, определяемых формулами (4.2) и (4.3).

Блок 3 (фиг.2) предназначен для анализа расположения операндов на числовой оси. Входными сигналамиблока 3 являются г-ичные цифры j а; | и lb;j операндов, постз пающие соответственно на дешифраторы 33 и 34. На выходы 58-61, 62-71 блока сЗ выдаются соответственно логические фзшкции

5

б

в

И ЛО8

гические переменные Ху, х, х,, х X „ , х,2, поступающие в блоки 8, 9, 11 и 12.

Блок В (фиг.З) предназначен для формирования логических функций у, Уг Уэ У4 необходимых для выбора

одного из четырех значений j , а также логических функций z,, z ,3, z,4. Входными сигналами блока 8 являются знаки операндов и логические переменные х, х, х,, Хд, х,, , х„ Логические функции у,, у, у, у вьздаются на выходы 108, 107, 106 и 105 блока 8. Логические функции z,, Z ,0 ) z,4 вьщаются на выходы 102 - 104 блока 8.

Значения промежуточной суммы с выходов группы коммутаторов 7 поступают на соответствующие группы информационных входов шифраторов 10 группы и первую грзшпу входов блока 9 формирования сигналов переноса.

Блок 9 формирования сигналов переноса (фиг.4) предназначен для форми

рования сигналов переноса в следующий старший г-ичный разряд w , w , w; логических функций Н,, Hj, Н,

о

Н ,, , и логических функций у, у (, , Входными сигналами блока 9 формирования сигналов переноса являются 25 j-x дешифраторов первой, и второй

1

)

логические функции z,, z Zg, z ,0 , z ,f , z, , .Сигналы переноса , wV , w° выдаются на выходы 163, 160 и 161 блока 9 формирования сигналов переноса и с них на выходы 22 - 24 сумматора. Логические функции Н4, Hj, Нб, Н ,3 , Н ,4 вьщаются на выходы 158, 157, 159, 165,164 блока 9 формирования сигналов переноса. Логические функции у,о и у„ вы- .,5 отрицательного, нулевого и подаются на выходы 162 и 166 блока 9 ложительного переноса сумматора, вхо- формирования сигналов переноса, с ко- ды отрицательного и положительного торых поступают в блоки 11 и 12. переноса которого соединены соответственно с первым и вторым входами 40 блока сравнения промежуточной суммы с набором констант, группа выходов блока формирования сигналов переноса соединена с первой группой входов блока сравнения промежуточной суммы д5 с набором констант, первая группа выходов которого соединена с входами разрешения группы блоков шифрации

суммы группы, выходы которых ЯВЛЯЮ

ся выходом суммы сумматора, отличающийся тем, что, с целью сокращения аппаратурных затрат, он содержит блок сравнения слагаемых с набором констант, блок задания вида операции, блок формирования знака, группу шифраторов вьмитания и группу коммутаторов, причем выходы дешифраторов первой и второй групп соединены соответственно с первой и второй группами входов блока сравнения слаБлок 1 (фиг.5)предназначен для формирования девяти сигналов управления, используемых дпя выбора одного из девяти значений , а также логических функций z,, , z.,j, , z,., z,y., z, . Входными сигналами блока И являются знаки операндов, логические функции Zj, Zg, z,, Z,Q , Z, ,

H, Hj, Hg, Н,э , H,4, y,o , У„ , сигналы переносов из младшего г-ичного разряда vff , , w j , . На выходах шифраторов 10 по формулам (5.1)-(5.9) формируется значение ; , представ- собой результат алгебраического сложения по соответствующему мо- дулнз ССОК.

Знак результата операции алгебраического сложения вычисляется блоком 12 формирования знака на основе сигналов, полученных с блоков 3, 8, 9

50

55

ю

138334910

и 11 сумматора, т.е. логических функ

ций Z

f

б

7 f

-& П.. Н.

ЧО I

Н

z It )

Н,

12

Н,

5 j-x дешифраторов первой, и второй

13 15 у 6 I ll 14

1 У сигналов переноса из младшего г-ичного разряда wT, , w;, , сигналов переноса в старший г-ичный разряд ,. w° . Знак с выхода блока 12 поступает на выход 21 сумматора.

Формула изобретения

«

j-x дешифраторов первой, и второй

групп ( 1-, - количество модулей системы остаточных классов) соединены соответственно с первыми и вторы-- ми входами элементов И j-и матрицы группы, выходы элементов И которой соединены с входами j-ro шифратора сложения группы, первый, второй и третий выходы блока формирования переносов являются соответственно выхогаемых с набором констант, входы первой группы блока формирования сигналов переноса соединены соответственно с выходами коммутаторов группы, первый, второй, третий и четвертый информационные входы j-ro коммутатора группы соединены соответственно с выходом j-ro шифратора сложения группы, j-ro шифратора вычитания группы, с J-M входом первой константы группы сумматора и с J-M входом второй константы группы сумматора, входы соответствующих шифраторов сложения группы и шифраторов вычитания группы объединены, вход знака первого слагаемого сумматора соединен с первым входом блока задания вида операции и с третьим входом блока сравнения промежуточной суммы с набором констант, вход знака второго слагаемого сумматора соединен с вторьм входом блока задания вида операции и четвертым входом блока сравнения промежуточной суммы р набором констант, входы отрицательного и нулевого переносов сумматора соединены соответственно с первым и вторым входами блока формирования знака, третий и четвертый входы которого соединены соответственно с вторым и третьим выходами блока формирования сигнала переноса, вторая группа входов которого соединена с первой группой выходов блока сравнения сла- гаемьк с набором констант, вторая группу выходов которого соединена с второй группой входов блока сравнения промежуточной суммы с набором констант и первой группой входов блока формирования знака, выход которого является выходом знака сумматора, третья группа выходов блока сравнения слагаемых с набором констант соединена с группой входов блока задания вида операции, первая группа выходов которого соединена с третьей группой входов блока формирования сигналов переноса, с третьей группой входов блока сравнения промежуточной суммы с набором констант и второй группой входов блока формирования знака, третья группа входов которого соединена с второй группой выходов блока задания вида операции, вторая и третья группы выходов которого сое динены с управлянлцими входами коммутаторов группы, группа вькодов блока формирования сигналов переноса

10

15

20

25

30

35

40

45

50

55

соединена с четвертой группой входов блока формирования знака, пятая группа входов которого соединена с четвертой грзшпой входов блока формирования сигналов переноса и второй группой выходов блока сравнения промежуточной суммы с набором констант. 2. Сумматор по П.1, о т л и ч а- ю щ и и с я тем, что блок сравнения слагаемых с набором констант содержит два дешифратора, пять элементов ИЛИ, четырнадцать элементов И, два элемента НЕ, причем входы первого и второго дешифраторов являются соответственно входами первой и второй групп блока, первые входы девятого и четырнадцатого элементов И, третий выход третьей группы блока объединены между собой и подключены к первому выходу первого дешифратора, вторые входы восьмого и четырнадцатого элементов И, четвертый выход третьей группы блока объединены между собой и подключены к первому вькоду второго дешифратора, второй выход первого дешифратора соединен с первым входом восьмого элемента И, второй выход второго дешифратора соединен с вторым входом девятого элемента И, выходы восьмого и девятого элементов И соединены соответственно с первьп и вторым входами четвертого элемента ИЛИ, выход которого явля- ется вторым выходом второй группы блока, выходы с третьего по (г/4-2)-й первого и второго дешифраторов соединены соответственно с входами с первого по (г/4 - 4)-и первого и второго элементов ИЛИ, первьй вход тринадцатого элемента И, (г/4 - 3)-й вход первого элемента ИЛИ объединены между собой и подключены к (r/4-l)- му выходу первого дешифратора, первые входы седьмого и одиннадцатого элементов И, (г/4-2)-и вход первого элемента ИЛИ объединены мезаду собой и подключены к г/4-му выходу первого дешифратора, первые входы пятого, десятого элементов И, (r/4-l)-й вход первого элемента ИЛИ, первьй выход третьей группы блока (г - основание системы счисления) объединены между собой и подключены к (г/4+1)-му выходу первого дешифратора, первые входы шестого, двенадцатого элементов И, (г/4)-и вход первого элемента ИЛИ, второй выход третьей группы блока объединены между собой и подклетчены к (г/4+2)-му выходу первого дешифратора, первые входы первого и четвертого элементов И, вход первого элемента НЕ объединены между собой и подключены к выходу первого элемента ИЛИ, первые входы второго и третьего элементов И объединены между собой и подключены к выходу перво го элемента НЕ, второй вход двенадца того элемента И, (г/4-3)-й вход вто- рюго элемента ИЛИ объединены между собой и подключены к (г/4-1)-му выходу второго дешифратора, вторые вхо ды шестого, десятого элементов И, (г/4-2)-и вход второго элемента ИЛИ объединены между собой и подключены к г/4-му выходу второго дешифратора, вторые входы пятого и одиннадцатого элементов И, (г/4-1)-и вход второго элемента ИЛИ, шестой выход третьей группы блока объединены между собой и подключены к (г/4+1)-му выходу вто рого дешифратора, вторые входы седьмого и тринадцатого элементов И, r/4-й вход второго элемента ИЛИ, пятый выход третьей группы блока объединены между собой и подключены к (г/4+2)-му выходу второго дешифратора, вторые входы первого и третьего элементов И, вход второго элемента НЕ обьединены между собой и подключены к выходу второго элемента ИЛИ, вторые входы второго и четвертого элементов И объединены между собой и подключены к выходу второго элемента НЕ, выходы первого, второго, третьего и четвертого элементов И являются соответственно первым, вторым, третьим и четвертым выходами пер1вой группы блока, первый, второй и третий входы третьего элемента ИЛИ соединены соответственно с выходами пятого, шестого и седьмого элементов И, первый, второй, третий и четвертый: входы пятого элемента ИЛИ соединены соответственно с выходами десятого, одиннадцатого, двенадцатого и тринадцатого элементов И, выходы третьего, пятого элементов ИЛИ, четырнадцатого элемента И являются соответственно первым, третьим и четвертым выходами второй группы блока. 3. Сумматор по п.1, о т л и ч а- ю ш и и с я тем, что блок,, задания вида операции содержит шесть элементов НЕ, шесть элементов ИЛИ и десять элементов И, причем третий вход первого элемента И, второй вход второго

10

15

20

25

30

35

40

45

50

55

элемента И объединены между собой и являются первым входом группы блока, четвертый вход первого элемента И, первый вход второго элемента И, третьи входы седьмого и девятого элементов И объединены между собой и являются пятым входом группы блока, первый вход первого элемента И, второй вход четвертого элемента И, первый вход шестого элемента И объединены между собой и подключены к выходу первого элемента НЕ, второй вход первого элемента И, третий вход четвертого элемента И, второй вход пятого элемента И, вход второго элемента НЕ объединены между собой и являются вторым входом блока, третий вход второго элемента И, первый вход третьего элемента И, первый вход пятого элемента И, вход первого элемента НЕ объединены между собой и являются первым входом блока, четвертьй вход второго элемента И, вторые входы третьего и шестого элементов И объединены между собой и подключены к выходу второго элемента НЕ, третий вход третьего элемента И, первый вход Четвертого элемента И обьединены между собой и являются вторым входом группы блока, четвертые входы третьего и четвертого элементов И, вторые входы седьмого и восьмого элементов И .объединены между собой и являются третьим входом группы блока, первые входы первого и четвертого элементов РШИ объединены между собой и подключены к выходу первого элемента И, второй вход четвертого элемента ИЛИ, первый вход второго элемен«га ИЛИ объединены между собой и подключены к выходу второго элемента И, третий еход четвертого элемента ИЛИ, второй вход первого элемента ИЛИ объединены между собой и подключены к выходу третьего элемента И, четвертый вход четвертого элемента ИЛИ соединен с выходом третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами пятого и шестого элементов И, пятый вход четвертого элемента ИЛИ, второй вход второго элемента Ш1И соединены между собой и подключены к выходу четвертого элемента И, выходы первого и второго элементов ИЛИ являются соответственно первым и вторым выходами первой группы блока, первый вход Десятого элемента И, вход третьего элемента НЕ, первые входы седьмого, восьмого и девятого элементов И объединены между собой и подключены к выходу четвертого элемента ИЛИ,второй, третий, четвертый входы десятого элемента И соединены соответственно с выходами четвертого, пятого и шестого элементов НЕ, первый вход пятого элемента ИЛИ, вход четвертого элемента НЕ, первый выход второй группы блока объединены между собой и подключены к выходу седьмого элемента И, второй вход пятого элемента ИЛИ, первый вход шестого элемента ИЛИ, вход пятого элемента НЕ объединены между собой и подключены к выходу восьмого элемента И, третий вход пятого элемента ИЛИ, второй вхо шестого элемента ИЛИ, вход шестого элемента НЕ объединены между собой и подключены к выходу девятого элемента И, третий вход восьмого элемента И, второй вход девятого элемента И являются соответственно шестым и четвертым входами группы блока, выход .пятого элем€1нта ИЛИ являетс я соответственно третьим выходом первой группы блока, выходы третьего элемента НЕ, десятого элемента И, шестого элемента ИЛИ являются соответственно вторым и первым выходами третьей группы блока, вторым выходом вто- pdPi группы блока.

0

5

0

5

0

5

0

5

первый вход третьего элемента ИЛИ объединены между собой, первый выход группы блока соединен с вторьш входом третьего элемента ИЛИ, третий выход группы блока, вход пятого элемента НЕ, третий вход третьего элемента ИЛИ объединены между собой, вход второго элемента НЕ соединен с первым входом четвертого элемента ИЛИ, первый вход пятого элемента ШШ соединен с выходом второго элемента ИЛИ, второй вход пятого элемента ИЛИ, вход первого элемента НЕ объединены между собой и подключены к выходу третьего элемента ИЛИ, третий вход пятого элемента ИЛИ, первый вход шестого элемента ИЛИ объединены между собой и подключены к выходу четвертого элемента ИЛИ, второй вход шестого элемента ИЛИ соединен с выходом первого элемента ИЛИ, первые входы второго, третьего, четвертого, пятого элементов И объединены между собой и подключены к выходу пятого элемента ИЛИ, вторые входы второго и третьего элементов И, первый вход шестого элемента И объединены между собой и подключены к третьему входу четвертой группы блока, вторые входы четвертого, пятого элементов И, первый вход седьмого элемента И объединены между собой и подключены к второму входу четвертой группы блока, третьи входы второго, четвертого элементов И, второй вход восьмого элемента И объединены между собой и подключены к четвертому входу второй группы блока, третьи входы третьего и пятого элементов И, второй вход девятого элемента И объединены между собой и подключены к третьему входу второй группы блока, вторые входы шестого и седьмого элементов И, первый вход седьмого элемента РШИ объединены меладу собой и подключены к первому входу второй группы блока, второй вход седьмого элемента ИЛИ подключен к второму входу второй группы блока, первый, второй, третий, четвертый входы одиннадцатого элемента ИЛИ соединены соответственно с йькодами второго, третьего, шестого элементов И, первым входом третьей группы блока, первый вход четырнадцатого элемента ИЛИ, первый выход блока объединены между собой и подключены к выходу одиннадцатого элемента ИЛИ, первый, второй, третий и четвертый входы двенадцатого элемента ИШ1 соединены соответственно с выходами четвертого, пятого, седьмого элементов И, с вторым входом третьей группы блока, второй вход четырнадцатого элемента ИЛИ третий выход блока объединены между собой и подключены к выходу двенадцатого элемента ИЛИ, четвертый вькод группы блока, вход восьмого элемента НЕ объединены между собой и подключены к выходу четьфнадцатого элемента ИЛИ, выход восьмого элемента НЕ является вторым выходом блока, первый и второй входы первого элемента И соединены соо.тветственно с выходами первого и четвертого элементов НЕ, вход четвертого элемента НЕ, второй вход одиннадцатого элемента И объединенм между собой и подключены к выходу шестого элемента ИЛИ, второй вход дес.ятого элемента И, первый вход одиннадцатого элемента И объединены между, собой и подключены к выходу седьмого элемента ИЛИ, первый вход десятого элемента И соединен с выходом первого элемента И, первый и третий входы восьмого элемента И соединены соответственно с выходами второго и пятого элeмeнtoв НЕ, а выход соединен с вторым входом девятого элемента ИЛИ, первый вход которого соединен с выходом одиннадцатого элемента И;, первьй и третий входы девятого элем€ нта И соединены соответственно с вЬкодами шестого и третьего элементов НЕ, а выход девятого элемента/И соединен с вторым входом десятого элемента ИЛИ, первый вход которого соединен с выходом десятого элемента И, вторые входы тринадцатого, четырнадцатого, пятнадцатого элементов И объединены между собой и подключены к выходу двенадцатого элемента И, первый и второй входы которого соединены соответственно с выходом седьмого элемента НЕ, и первьм входом четвертой группы блока, вход сёдьм&го элемента НЕ соединен с выходом восьмого элемента ИЛИ, первый и второй входы которого подключены соответственно к второму и первому входам третьей группы блока, выход девятого элемента ИЛИ соединен с первым входом тринадцатого элемента И, выход которого является пятым выходом группы блока, первый вход тринадцатого элемента ИЛИ, .первый вход четырнадцатого элемента И объединены между

0

S

0

5

0

5

0

5

0

5

собой и подключены к выходу десятого элемента ИЛИ, выход четырнадцатого элемента И является шестым выходом группы блока, выход тринадцатого элемента ИЛИ соединен с первым входом пятнадцатого элемента И, выход которого является седьмым вькодом группы блока.

5

0

5

0

5

0

5

0

5

объединены между собой и подключены к выходу седьмого элемента НЕ, вход седьмого элемента НЕ, третий вход девятого элемента И, первьй вход десятого элемента И объединены между собой и подключены к выходу третьего элемента ИЛИ, третий вход шестого элемента И, пятый вход одиннадцатого элемента И, третий вход четырнадцатого элемента И, четвертый вход шестнадцатого элемента И, вторые входы девятнадцатого, двадцать четвертого элементов,И, третий вход тридцать второго элемента И, второй вход тридцать пятого элемента И, второй вход третьего элемента ИЛИ объединены между собой и подключены к второму входу блока, третий вход пятого элемента И, четвертый вход седьмого элемента И, второй вход тринадцатого .элемента И, пятый вход пятнадцатого элемента И, второй вход двадцатого элемента И, второй вход двадцать седьмого элемента И, третий вход тридцать первого элемента И, второй вход тридцать восьмого элемента И, первый вход третьего элемента ИЛИ объединены между собой и подключены к первому входу блока, вторые входы пятого и шестого элементов И, третий вход тринадцатого элемента И, первый вход четырнадцатого элемента И объединены между собой и подключены к выходу четвертого элемента ИЛИ, первый и второй входы которого подключены соответственно к третьему и пятому входам первой группы блока, четвертый вход седьмого элемента ИЛИ, третий вход одиннадцатого элемента ИЛИ объединены между собой и подключены к первому входу третьей группы блока, четвертый вход восьмого элемента ИЛИ, третий вход десятого элемента ИЛИ объединены между собой и подключены к второму входу третьей группы блока, второй вход девятого элемента И подключен к первому входу первой группы блока, первый, второй, третий, четвертый, пятый и шестой входы пятого элемента ИЛИ соединены соответственно с выходами пятого, щестого, седьмого, девятого, десятого и одиннадцатого элементов И, вторые входы восьмого и двенадцатого элементов И первый вход семнадцатого элемента И объединены между собой и подключены к выходу восьмого элемента НЕ, третьи входы восьмого и двенадцатого элемен

10

25

30

тов и, второй вход семнадцатого элемента И объединены между собой и подключены к выходу девятого элемента НЕ, выход восьмого элемента И является первым выходом первой группы блока, выход пятого элемента ИЛИ подключен к первому входу двенадцатого элемента И, выход которого является вторым выходом первой группы блока, первый, второй, третий и четвертый входы шестого элемента ИЛИ соединены соответственно с выходами тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого элементов И, выход шее-15 того элемента ИЛИ подключен к третьему входу семнадцатого элемента И, выход которого является третьим выходом первой группы блока, выход восемнадцатого элемента И является чет- 20 вертым выходом первой группы блока, первый и второй входы седьмого элемента ИЛИ подключены соответственно к выходам двадцать первого и двадцать второго элементов И, третий вход седьмого элемента ИЛИ, первый вход восьмого элемента ИЛИ объединены между собой и подключены к выходу двадцать третьего элемента И, первый вход двадцать четвертого элемента И .подключен к вькоду седьмого элемента ИЛИ, второй и третий входы восьмого элемента ИЛИ подключены соответственно к выходам двадцать пятого и двадцать шестого элементов И, выход восьмого элемента ИЛИ соединен с первым входом двадцать седьмого элемента И, первьш, второй, третий и четвертый входы девятого элемента ИЛИ соединены соответственно с выходами девятнадцатого, двадцатого, двадцать четвертого, двадцать седьмого элементов . И, второй вход двадцать элемента И, первый вход двадцать девятого элемента И объединены между собой 45 и подключены к выходу девятого элемента ИЛИ, вьпсоды двадцать восьмого и двадцать девятого элементов И являются соответственно пятым и восьмым выходами первой группы блока, выход тридцатого элемента И является седьмым выходом первой группы блока, первый и второй входы .десятого элемента ИЛИ подключены соответственно к выходам тридцать третьего и тридцать четвертого элементов И, выход десятого элемента ИЛИ соединен с пер- вьвл входом тридцать пятого элемента И, первый и второй входы одиннадцато138334922

го элемента ИЛИ подключены соответственно к выходам тридцать шестого и тридцать седьмого элементов И, выход одиннадцатого элемента ИЛИ соединен с первым входом тридцать восьмого элемента И, второй вход тридцать девятого элемента И, первый вход сорокового элемента И объединены между собой и подключены к выходу двенадцатого элемента И, выходы тридцать девятого и сорокового элементов И являются соответственно девятым и шестым выходами первой группы блока, первый, второй, третий и четвертый входы двенадцатого элемента ИЛИ подключены соответственно к выходам тридцать первого, тридцать второго, тридцать пятого, тридцать восьмого элементов И.

40

50

55

ю щ и и с я тем, что блок формирования знака содержит два элемента НЕ, шесть элементов ИЛИ и четырнадцать элементов И, причем выход шестого элемента ИЛИ является выходом блока, входы шестого элемента ИЛИ с первого по тринадцатый подключены соответственно к выходам тринадцатого, один- надцатого, девятого, седьмого, пятого элементов И, к второму входу второй группы блока, к выходам третьего, четвертого, шестого, восьмого, десятого, двенадцатого, четырнадцатого элементов И, первый вход тринадцатого элемента И, первый вход первого элемента ИЛИ объединены между собой и подключены к первому входу третьей группы блока, второй вход тринадцатого элемента И, третий вход одиннадцатого элемента И, третий вход девято-. го элемента И, четвертьм вход седьмого элемента И, третий вход пятого элемента И объединены между собой..и подключены к третьму входу пятой группы блока, второй вход одиннадцатого элемента И, второй вход второго элемента ИЛИ, второй вход десятого элемента И объединены между собой и подключены к первому входу первой группы блока, первый вход одиннадцатого элемента Р1, первый вход третьего элемента ИЛИ, первые входы шестого, десятого, двенадцатого элементов И объединены между собой и подключены к первому входу блока, второй вход .девятого элемента И, второй вход первого элемента ИЛИ объединены между собой и подключены к второму

5

0

5 20 . 5

5

0

0

5

ю щ и и с я тем, что блок формирования знака содержит два элемента НЕ, шесть элементов ИЛИ и четырнадцать элементов И, причем выход шестого элемента ИЛИ является выходом блока, входы шестого элемента ИЛИ с первого по тринадцатый подключены соответственно к выходам тринадцатого, один- надцатого, девятого, седьмого, пятого элементов И, к второму входу второй группы блока, к выходам третьего, четвертого, шестого, восьмого, десятого, двенадцатого, четырнадцатого элементов И, первый вход тринадцатого элемента И, первый вход первого элемента ИЛИ объединены между собой и подключены к первому входу третьей группы блока, второй вход тринадцатого элемента И, третий вход одиннадцатого элемента И, третий вход девято-. го элемента И, четвертьм вход седьмого элемента И, третий вход пятого элемента И объединены между собой..и подключены к третьму входу пятой группы блока, второй вход одиннадцатого элемента И, второй вход второго элемента ИЛИ, второй вход десятого элемента И объединены между собой и подключены к первому входу первой группы блока, первый вход одиннадцатого элемента Р1, первый вход третьего элемента ИЛИ, первые входы шестого, десятого, двенадцатого элементов И объединены между собой и подключены к первому входу блока, второй вход .девятого элемента И, второй вход первого элемента ИЛИ объединены между собой и подключены к второму

Фиг.2

Jf Xf lit If /tq

г

74

%

.Ю2

Ш

3d

rgji

85

29

«

7(7

«

Ю8

7

Siynbi ((l 3S37 98 39 mV} 91 ЗУ

о о о

Ш

СШ

ЛЛ

ГЖ1

/

1

f

Фиг.3

J

fi3 Zn ifz

15S VfJ 148 О

N

C w Щ

25 28

A 3 ii li 1,0 is /50/5/752 Ш/Я Ш

НП Hid i/n

ws

J7

Фиг.

29

А

28 28 283 285 287 288232 Z33 295 297 2S92S2 238 23S

275 12/

31

26

А

.5

1

1383349 Др

Г

о-

Pm

-31±

im

СЖЗ

. Si I

j..jU

/ V VV() р

Фае 7 // /7/7tf сигнамВ с блока Л

1

И

I

|1Й

L

nft

t|:

-ijL шп

J

i Hwopr awjfi с алока 7

iiCrr

п

;/

п

r i II

I I.

ц:

| Устройство для сложения @ -разрядных чисел в избыточной системе счисления | 1984 |

|

SU1188731A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-03-23—Публикация

1986-07-04—Подача