Ьы)(од

€

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для компенсации искажений типа "преобладание | 1987 |

|

SU1506581A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство тактовой синхронизации | 1985 |

|

SU1254589A1 |

| Устройство для компенсации искажений типа преобладания | 1987 |

|

SU1496013A2 |

| Устройство для компенсации искажений типа "преобладание | 1983 |

|

SU1113899A1 |

| Формирователь управляющего сигнала для компенсации искажений типа "преобладание | 1989 |

|

SU1676109A2 |

Изобретение относится к электросвязи. Цель изобретения - повышение быстродействия и упрощения устр-ва, Устр-во содержит входной пороговый блок 1, блок 3 тактовой синхронизации, блок 4 сравнения, формирователь 5 управляющих сигналов. Введен блок 2 выделения фронтов. Блок 4, состоит из эл-тов И 6-9 и эл-тов ИЛИ 10 и 11. Формирователь 5 состоит из реверсивного счетчика 12 и преобразователя 13 код- напряжение. Для работы устр-ва используются все фронты принимаемых посылок дискретного сигнала. В зависимости от исполь- дуемого кода и языка для передами среднее отношение числа фронтов посылок к их общему числу 30--50°/о. 2 з.п. ф-лы,.2 ил.

ОЗ 00

сл

09 qD

Изобретение относится к электросвязи и может использоваться в приемной части систем передачи дискретной ииформации.

Цель изобретения - повьнпеиие быстродействия и упрощение устройства.

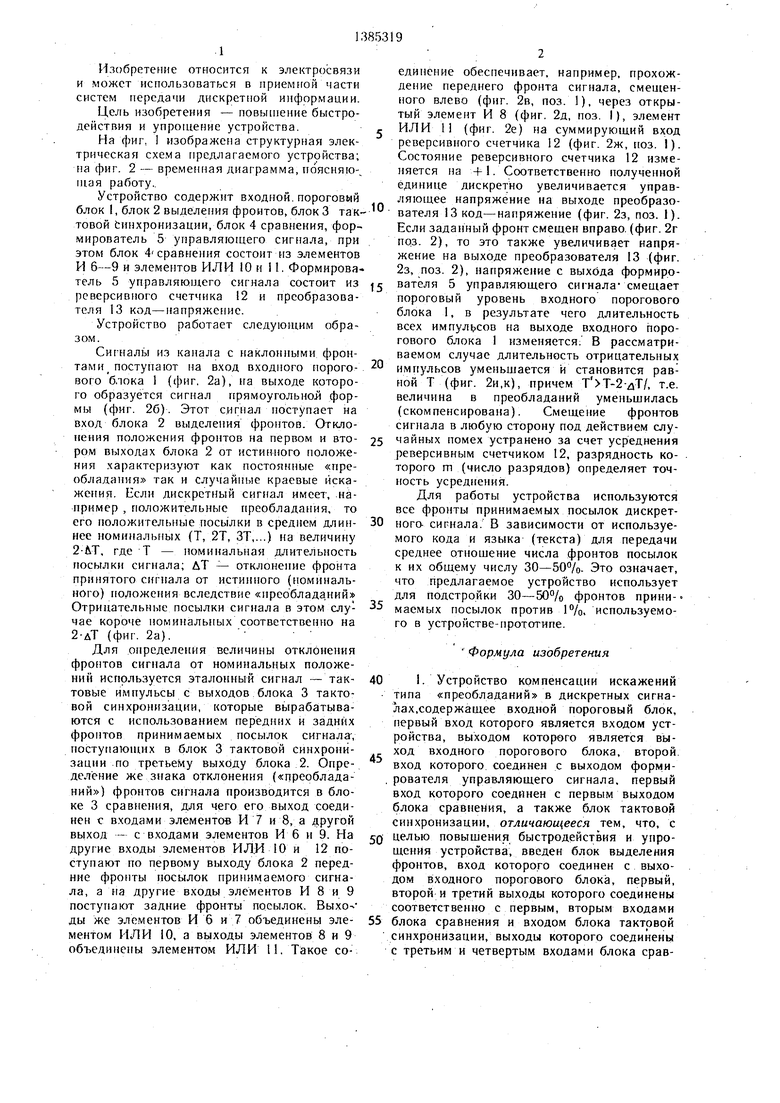

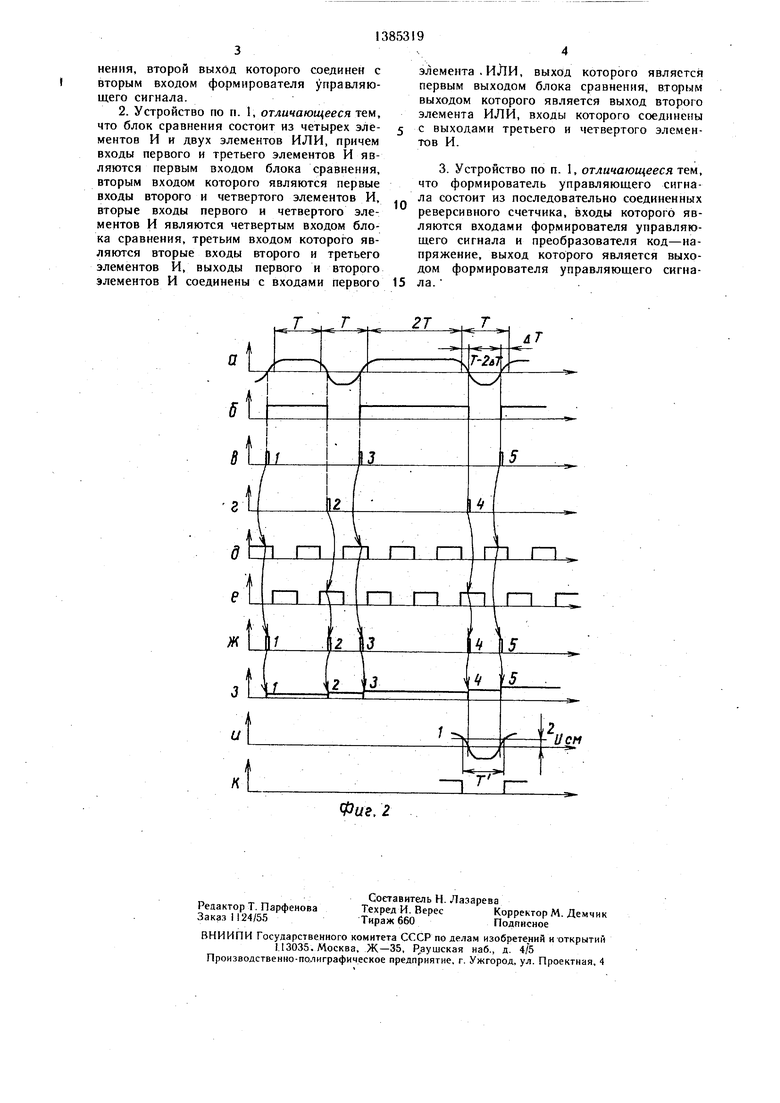

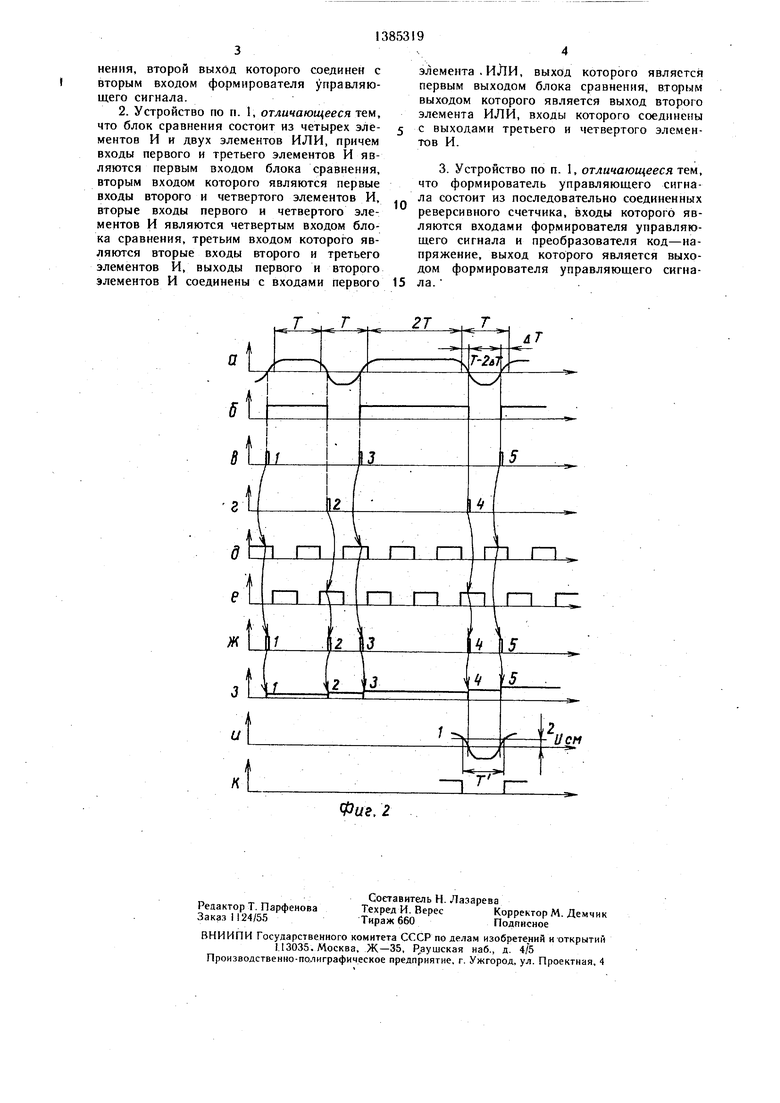

На фиг, 1 изображена структурная электрическая схема предлагаемого устр9нства; на фиг. 2 - временная диаграмма, пбясияю-, П1ая работу..

Устройство содержит входной.пороговый блок I, блок 2 выделения фронтов, блок 3 тактовой Синхронизации, блок 4 сравнения, формирователь 5 управляющего сигнала, при этом блок 4 сравнения состоит из элементов И 6-9 и элементов ИЛИ 10 и 11. Формирователь 5 управляюпхего сигнала состоит из реверсивного счетчика 12 и преобразователя 13 код-напряжение.

Устройство работает следующим образом.

Сигналь из канала с иаклониыми фронтами поступают на вход входного порогового блока 1 (())иг, 2а), на выходе которого образуется сигнал прямоугольной формы (фиг. 26). Этот сигнал иоступает на вход блока 2 выделения фронтов. Отклонения положения фронтов на первом и втором выходах блока 2 от истинного положения характеризуют как постоянные «преобладания так и случаЙ1п,е краевые искажения. Если дискретный сигнал имеет, .например , положительные преобладания, то его положительные посылки в среднем длиннее номинальных (Т, 2Т, ЗТ,...) на величину 2-ЛТ, где Т - номинальная длительность посылки сигнала; ДТ - отклонение фронта принятого сигнала от истинного (номинального) положения вследствие «прео блада.ний Отрицательные посылки сигнала в этом случае короче номинальных соответственно на 2-дТ (фиг. 2а). ;

Для определения величины отклонения фронтов сигнала от номинальных положений используется эталонный сигнал - тактовые импульсы с выходов блока 3 тактовой синхронизации, которые вырабатываются с использованием передних и задних фронтов принимаемых посылок сигнала , поступающих в блок 3 тактовой синхронизации по третьему выходу блока 2. Определение же знака отклонения («преобладаний) фронтов сигнала производится в блоке 3 сравнения, для чего его выход соединен с входами элементов И 7 и 8, а другой выход - с в.ходами элементов Мб н 9. На другие входы элементов ИДИ 10 и 12 поступают по первому выходу блока 2 передние фронты посылок принимаемого сигнала, а па другие входы элементов И 8 и 9 поступают задние фронты посылок. Выхо- ды же элементов И 6 и 7 объединены элементом ИЛИ 10, а выходы элементов 8 и 9 объединены элементом ИЛИ П. Такое соединение обеспечивает, например, прохождение переднего фронта сигнала, смещенного влево (фиг. 2в, поз. 1), через открытый элемент И 8 (фиг. 2д, поз. I), элемент

ИЛИ

(фиг. 2е) на суммирующий вход

реверсивного счетчика 12 (фиг. 2ж, поз. 1). Состояние реверсивного счетчика 12 изменяется на + 1. Соответственно полученной единице дискретно увеличивается управляющее напряжение на выходе преобразователя 13 код-напряжение (фиг. 2з, поз. 1). Если заданный фронт смещен вправо, (фиг. 2г поз. 2), то это также увеличивает напряжение на выходе преобразователя 13 (фиг. 2з, поз. 2), напряжение с выхода формирователя 5 управляющего сигнала- смещает пороговый уровень входного порогового блока 1, в результате чего длительность всех импульсов на выходе входного порогового блока 1 изменяется; В рассматриваемом случае длительность отрицательных

импульсов уменьщается и становится равной Т (фиг. 2и,к), причем Т Т-2-лТ/, т.е. величина в преобладаний уменьшилась (скомпенсирована). Смещение фронтов сигнала в любую сторону под действием слу5 чайных помех устранено за счет усреднения реверсивным счетчиком 12, разрядность которого гп (число разрядов) определяет точность усреднения.

Для работы устройства используются все фронты принимаемых посылок дискрет0 нога сигнала. В зависимости от используемого кода и языка (текста) для передачи среднее отнощение числа фронтов посылок к их общему числу 30-бО /о. Это означает, что предлагаемое устройство использует для Подстройки 30-50% фронтов прини-

маемых посылок против , используемого в устройстве-прототипе.

Формула изобретения

0 I. Устройство компенсации искажений типа «преобладаний в дискретных сигна- лах,содержащее входной пороговый блок, первый вход которого является входом устройства, выходом которого является вы5

ход входного порогового блока, второй.

вход которого соединен с выходом форми- . рователя управляющего сигнала, первый вход которого соединен с первым выходом блока сравнения, а также блок тактовой синхронизации, отличающееся тем, что, с

0 целью повышения быстродействия и упрощения устройства, введен блок выделения фронтов, вход которого соединен с выходом входного порогового блока, первый, второй и третий выходы которого соединены соответственно с первым, вторым входами

5 блока сравнения и входом блока тактовой синхронизации, выходы которого соединены с третьим и четвертым входами блока сравнения, второй выход которого соединен с вторым входом формирователя управляющего сигнала.

элемента . ИЛИ, выход которого является первым выходом блока сравнения, вторым выходом которого является выход второго элемента ИЛИ, входы которого соединены с выходами третьего н четвертого элементов И.

| Авторское свидетельство СССР № 915274, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-03-30—Публикация

1986-11-03—Подача