(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1988 |

|

SU1580364A1 |

| Многоканальное устройство для временного разделения и синхронизации импульсных сигналов | 1989 |

|

SU1651361A1 |

| Многоканальное адаптивное аналого-цифровое устройство | 1987 |

|

SU1520660A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1987 |

|

SU1416978A1 |

| Устройство для контроля последовательностей сигналов | 1989 |

|

SU1654826A1 |

| Многоканальное устройство для включения резервных радиостанций | 1990 |

|

SU1748299A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1275442A1 |

| Устройство для автоматического контроля и поиска неисправностей | 1986 |

|

SU1322288A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Микропрограммное устройство управления | 1987 |

|

SU1629910A1 |

Изобретение может быть использовано в системах контроля работоспособности и электронного оборудования и позволяет повысить быстродействие устройства. Коммутирующее устройство содержит регистр 3, ключи 4-1-4-п, элемент ИЛИ 6, формирователь 8 импульсов и дешифратор 9. Введение тактового генератора 2 приоритетного шифратора 5, регистра 7 и образование новых функциональных связей способствует тому, что время выдачи сообщения о состоянии каналов не зависит от количества контролируемых каналов, а зависит лищь от числа неисправных каналов. В описании приведен пример реализации приоритетного шифратора 5. 2 ил., 1 табл.

со

00

оо

СХ)

Изобретение относится к коммутационной технике и может быть использовано в системах контроля работоспособности электронного оборудования.

Цель изобретения - повышение быстродействия за счет того, что время выдачи сообщения о состоянии каналов не зависит от количества контролируемых каналов, а только от числа неисправных каналов.

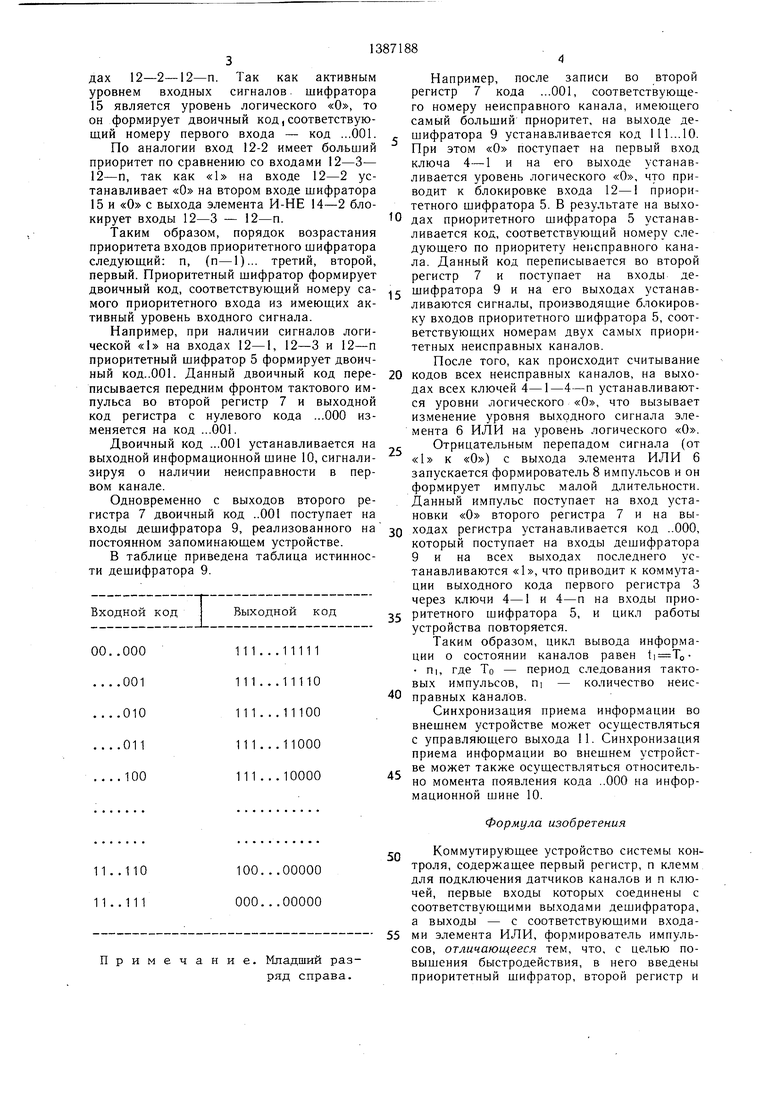

Выходные сигналы с клемм 1 - 1 - 1-п для подключения датчиков каналов переписываются в первый регистр 3 передНа фиг. 1 приведена структурная 10 ним фронтом тактовых импульсов, поступаю схема коммутирующего устройства системы щих с выхода тактового генератора 2. С фиг.

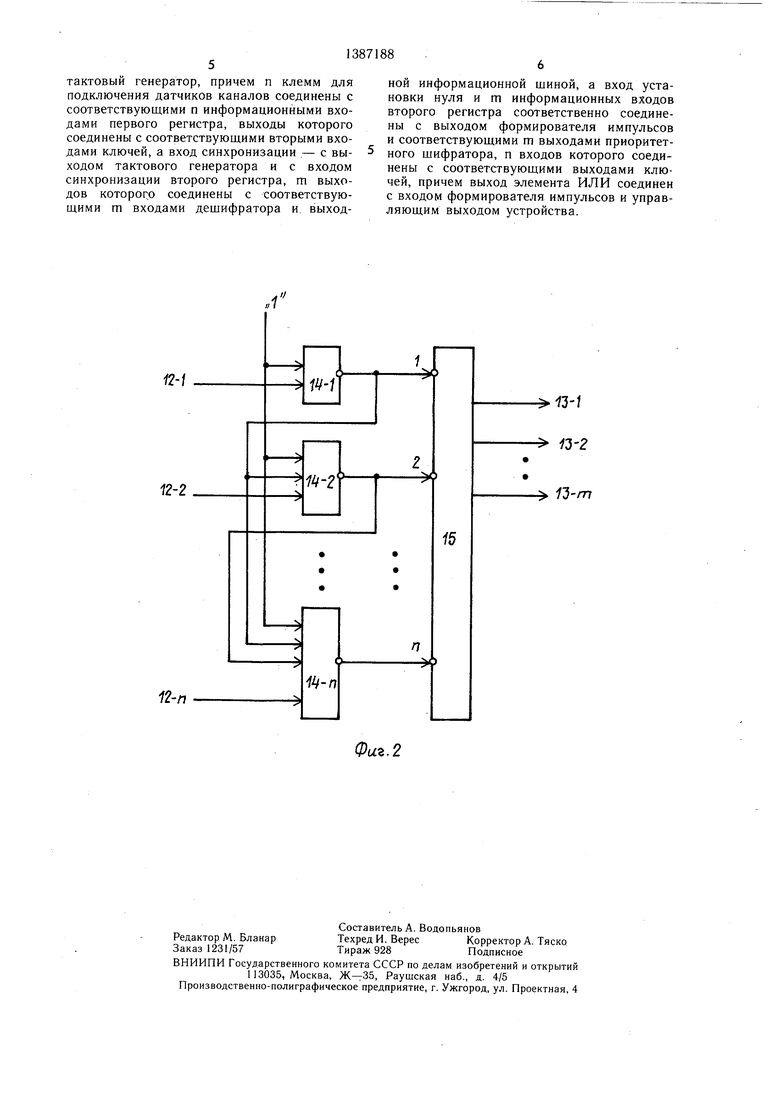

контроля; на фиг. 2 - функциональная схема приоритетного шифратора.

Устройство содержит клеммы 1 - 1 - 1-п для подключения датчиков каналов, тактовый генератор 2, первый регистр 3, ключи 4-1-4-п, приоритетный шифратор 5, элемент ИЛИ б, второй регистр 7, формирователь 8 импульсов, дешифратор 9, выходную информационную шину 10, уцравле- ющий выход 11, причем клеммы 1 - 1 - 1-п для подключения датчиков каналов соединены с соответствующими информационными входами первого регистра 3, выходы которого соединены с соответствующими вторыми входами ключей 4-1 - 4-п, первые входы которых соединены с соответствующими выходами дешифратора 9, m входов которого соединены с выходной информационной шиной 10 и с соответствующими гп выходами второго

выходов первого регистра 3 сигналы логического «О поступают на вторые входы ключей 4-1-4-п и устанавливают на их

с выходах сигналы логического «О, которые далее поступают на входы элемента ИЛИ 6 и на его выходе устанавливается потенциал логического «О, сигнализируя о том, что все каналы работают в требуемых режимах.

20 Если состояния некоторых контролируемых каналов в определенное время не соответствуют требуемым режимам работы, то на клеммах 1 - 1 - 1-п для подключения тех датчиков каналов, которые работают в неисправных каналах, устанавливаются сигналы логической «1. Передним фронтом тактового импульса логические состояния с клемм I - 1 - 1-п для подключения датчиков каналов переписываются в первый регистр 3. В результате на

35

регистра 7, вход синхронизации последнего о выходах соответствующих ключей 4-1 - соединен с выходом тактового генератора 2 и входом синхронизации первого регистра 3, причем п выходов ключей 4-1-4-п соединены с соответствующими входами элемента ИЛИ 6, выход которого соединен с управляющим выходом 11 устройства и входом формирователя 8 импульсов, выход которого соединен с входом установки нуля второго регистра 7, m информационных входов которого соединены с соответствующими выходами приоритетного шифратора 5, п входов последнего соединены с соответствующими выходами ключей 4-1-4-п. Приоритетный шифратор 5 содержит входы 12-1 -12-п, выходы 13-1 -13-т, элементы И-НЕ 14-1 -14-п,шифратор 15, причем m выходов шифратора 15 соединены с соответствующими выходами 13-1- 13-m приоритетного шифратора .5, входы 12-1 -12-п которого соединены с соответствующими первыми входами элементов И-НЕ 14-1 -14-п, вторые входы которых

4-п устанавливаются потенциалы логической «1, которые, поступая на входы элемента ИЛИ б, вызывают изменение уровня выходного сигнала.

Одновременно сигналы с выходов ключей 4-1-4-п поступают на входы приоритетного шифратора 5 и на входах последнего, соответствующих номерам неисправных каналов, устанавливаются сигналы логической «1.

Например, при неисправных первом, вто40 ром и п-м каналах сигналы логической

«1 устанавливаются на входах 12-1,

12-3 и 12-п приоритетного шифратора 5.

Приоритетный шифратор 5 (фиг. 2) работает следуюшим образом.

В рабочем состоянии сигнал логической «1 подается на вторые входы всех элементов И-НЕ 14-1 -14-п, подготавливая к работе приоритетный шифратор.

Активным уровнем входных сигналов приоритетного шифратора (фиг. 2) являетсоединены с шиной сигнала логической ся уровень логической «1: «1, а выходы каждого i-ro элемента И-НЕЕсли на входе 12-1 приоритетного

(14-i) соединены с (i-|-2)-M входом каж-шифратора 5 имеется «1 на выходе элемента И-НЕ 14-1 - «О. С выхода элемента И-НЕ 14-1 сигнал логического «О поступает на первую щину шифра- 55 тора 15 и на первые входы элементов И-НЕ 14-2-14-п, устанавливая на их выходах уровень сигнала логической «1 независимо от уровней сигналов на входого из последующих элементов И-НЕ 14-i+1 -14-п и с соответствующим входом шифратора 15..

Устройство работает следующим образом.

В исходном состоянии второй регистр 7

сброшен в «О и с выходов дещифратора 9

на первые входы ключей 4-1-4-п поступают сигналы логической «1.

Если состояния контролируемых каналов соответствуют требуемым режимам работ, на выходах всех клемм 1 - 1 - 1-п для подключения датчиков каналов устанавливаются сигналы логического «О.

Выходные сигналы с клемм 1 - 1 - 1-п для подключения датчиков каналов переписываются в первый регистр 3 перед ним фронтом тактовых импульсов, поступаю щих с выхода тактового генератора 2. С

ним фронтом тактовых импульсов, поступаю щих с выхода тактового генератора 2. С

выходов первого регистра 3 сигналы логического «О поступают на вторые входы ключей 4-1-4-п и устанавливают на их

выходах сигналы логического «О, которые далее поступают на входы элемента ИЛИ 6 и на его выходе устанавливается потенциал логического «О, сигнализируя о том, что все каналы работают в требуемых режимах.

Если состояния некоторых контролируемых каналов в определенное время не соответствуют требуемым режимам работы, то на клеммах 1 - 1 - 1-п для подключения тех датчиков каналов, которые работают в неисправных каналах, устанавливаются сигналы логической «1. Передним фронтом тактового импульса логические состояния с клемм I - 1 - 1-п для подключения датчиков каналов переписываются в первый регистр 3. В результате на

выходах соответствующих ключей 4-1 -

выходах соответствующих ключей 4-1 -

4-п устанавливаются потенциалы логической «1, которые, поступая на входы элемента ИЛИ б, вызывают изменение уровня выходного сигнала.

Одновременно сигналы с выходов ключей 4-1-4-п поступают на входы приоритетного шифратора 5 и на входах последнего, соответствующих номерам неисправных каналов, устанавливаются сигналы логической «1.

Например, при неисправных первом, втором и п-м каналах сигналы логической

«1 устанавливаются на входах 12-1,

12-3 и 12-п приоритетного шифратора 5.

Приоритетный шифратор 5 (фиг. 2) работает следуюшим образом.

В рабочем состоянии сигнал логической «1 подается на вторые входы всех элементов И-НЕ 14-1 -14-п, подготавливая к работе приоритетный шифратор.

Активным уровнем входных сигналов приоритетного шифратора (фиг. 2) является уровень логической «1: Если на входе 12-1 приоритетного

дах 12-2-12-п. Так как активным уровнем входных сигналов. шифратора 15 является уровень логического «О, то он формирует двоичный код, соответствующий номеру первого входа - код ...001.

По аналогии вход 12-2 имеет больший приоритет по сравнению со входами 12-3- 12-п, так как «1 на входе 12-2 устанавливает «О на втором входе шифратора 15 и «О с выхода элемента И-НЕ 14-2 блокирует входы 12-3 - 12-п.

Таким образом, порядок возрастания приоритета входов приоритетного шифратора следующий: п, (п-1)... третий, второй, первый. Приоритетный шифратор формирует

Например, после записи во второй регистр 7 кода ...001, соответствующего номеру неисправного канала, имеющего самый больший приоритет, на выходе де- - шифратора 9 устанавливается код 111...10. При этом «О поступает на первый вход ключа 4-1 и на его выходе устанавливается уровень логического «О, что приводит к блокировке входа 12-1 приоритетного шифратора 5. В результате на выхо- 10 дах приоритетного шифратора 5 устанавливается код, соответствующий номеру следующего по приоритету HeiicnpaBHoro канала. Данный код переписывается во второй регистр 7 и поступает на входы де- двоичный код, соответствующий номеру са- шифратора 9 и на его выходах устанав- мого приоритетного входа из имеющих ак-ливаются сигналы, производящие блокировтивный уровень входного сигнала.ку входов приоритетного щифратора 5, соотНапример, при наличии сигналов логи-ветствующих номерам двух самых приорической «1 на входах 12-1, 12-3 и 12-п тетных неисправных каналов. приоритетный шифратор 5 формирует двоич-После того, как происходит считывание

ный код..001. Данный двоичный код пере- 20 кодов всех неисправных каналов, на выхо- писывается передним фронтом тактового им-дах всех ключей 4-1-4-п устанавливаютпульса во второй регистр 7 и выходной код регистра с нулевого кода ...000 изменяется на код ...001.

Двоичный код ...001 устанавливается на выходной информационной шине 10, сигнализируя о наличии неисправности в первом канале.

Одновременно с выходов второго регистра 7 двоичный код ..001 поступает на

входы дешифратора 9, реализованного на о ходах регистра устанавливается код ..000, постоянном запоминающем устройстве.который поступает на входы дещифратора

9 и на всех выходах последнего устанавливаются «1, что приводит к коммутации выходного кода первого регистра 3 через ключи 4-1 и 4-п на входы прио- 35 ритетного щифратора 5, и цикл работы устройства повторяется.

Таким образом, цикл вывода информации о состоянии каналов равен П:, где То - период следования тактовых импульсов, п - количество неис- 40 правных каналов.

Синхронизация приема информации во внешнем устройстве может осуществляться с управляющего выхода 11. Синхронизация приема информации во внешнем устройстве может также осуществляться относительно момента появления кода ..000 на информационной шине 10.

25

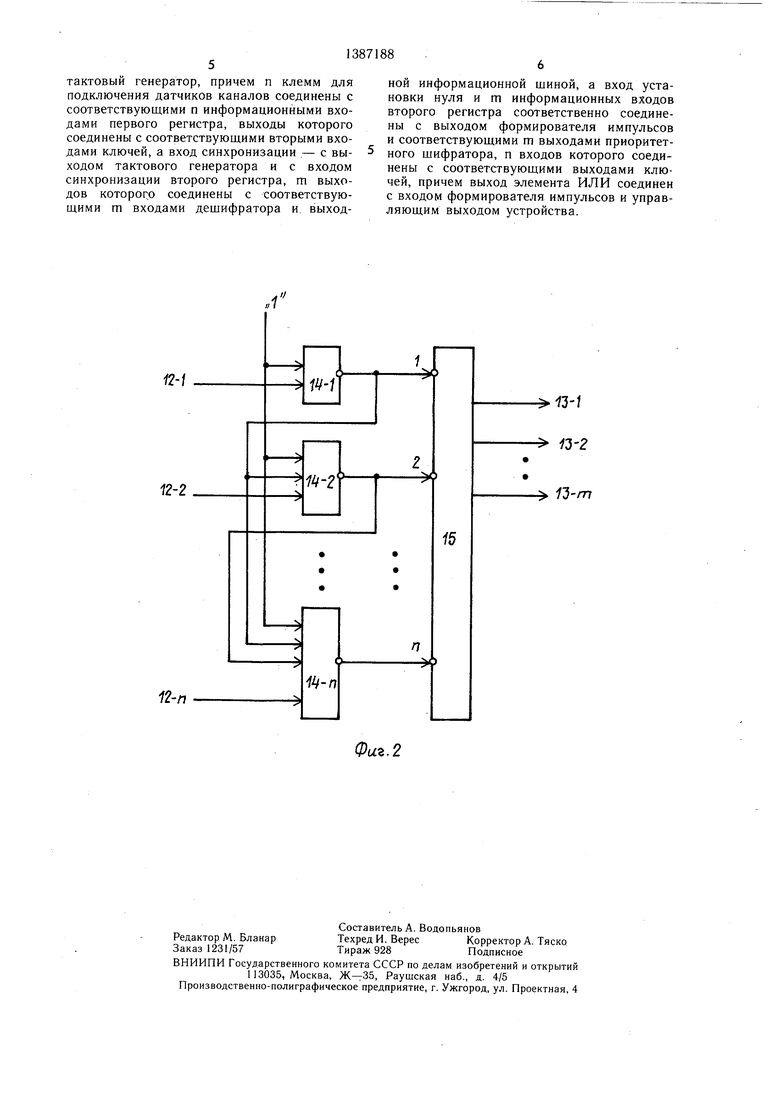

ся уровни логического «О, что вызывает изменение уровня выходного сигнала элемента 6 ИЛИ на уровень логического «О. Отрицательным перепадом сигнала (от «1 к «О) с выхода элемента ИЛИ 6 запускается формирователь 8 импульсов и он формирует импульс малой длительности. Данный импульс поступает на вход установки «О второго регистра 7 и на выВ таблице приведена таблица истинности дешифратора 9.

45

Примечание. Младший разряд справа.

кодов всех неисправных каналов, на выхо- дах всех ключей 4-1-4-п устанавливаютходах регистра устанавливается код ..000, который поступает на входы дещифратора

ся уровни логического «О, что вызывает изменение уровня выходного сигнала элемента 6 ИЛИ на уровень логического «О. Отрицательным перепадом сигнала (от «1 к «О) с выхода элемента ИЛИ 6 запускается формирователь 8 импульсов и он формирует импульс малой длительности. Данный импульс поступает на вход установки «О второго регистра 7 и на вы

Формула изобретения

КоммутируЮшее устройство системы контроля, содержащее первый регистр, п клемм для подключения датчиков каналов и п ключей, первые входы которых соединены с соответствующими выходами дешифратора, а выходы - с соответствующими входами элемента ИЛИ, формирователь импульсов, отличающееся тем, что, с целью повышения быстродействия, в него введены приоритетный шифратор, второй регистр и

тактовый генератор, причем п клемм для подключения датчиков каналов соединены с соответствующими п информационными входами первого регистра, выходы которого соединены с соответствующими вторыми входами ключей, а вход синхронизации ,- с выходом тактового генератора и с входом синхронизации второго регистра, m выходов которого соединены с соответствующими m входами дещифратора и выходной информационной щиной, а вход установки нуля и m информационных входов второго регистра соответственно соединены с выходом формирователя импульсов и соответствующими m выходами приоритетного щифратора, п входов которого соединены с соответствующими выходами ключей, причем выход элемента ИЛИ соединен с входом формирователя импульсов и управляющим выходом устройства.

Фиг. 2

| Коммутатор с самоконтролем | 1980 |

|

SU928642A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| КОММУТИРУЮЩЕЕ УСТРОЙСТВО СИСТЕМЫ АВТОКОНТРОЛЯ | 1972 |

|

SU434595A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-04-07—Публикация

1986-05-12—Подача